寫在前面

模塊復用是邏輯設計人員必須掌握的一個基本功,通過將成熟模塊打包成IP核,可實現重復利用,避免重復造輪子,大幅提高我們的開發效率。

接下來將之前設計的串口接收模塊和串口發送模塊打包成IP核,再分別調用這兩個IP核,構成串口接收--發送循回,依次驗證IP核打包及調用是否成功。

源碼在這:串口(UART)的FPGA實現

Vivado版本:Vivado 2019.2

開發板:xc7a35tfgg484-2

打包

打包串口發送模塊uart_tx

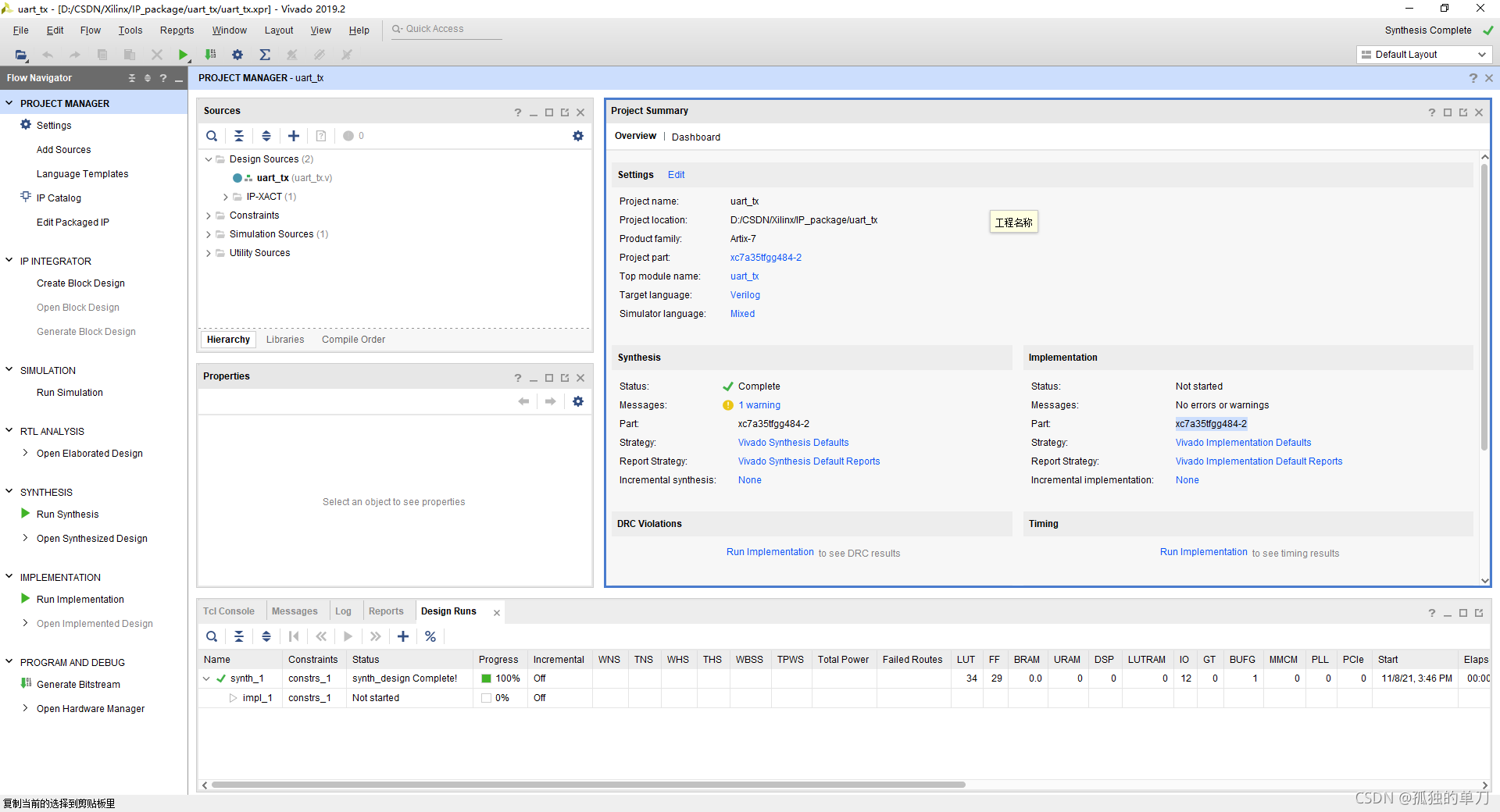

1、首先打開發送模塊的VIVADO工程,確保其編譯無誤(最好進行仿真驗證、上板驗證保證其功能正確性),如下:

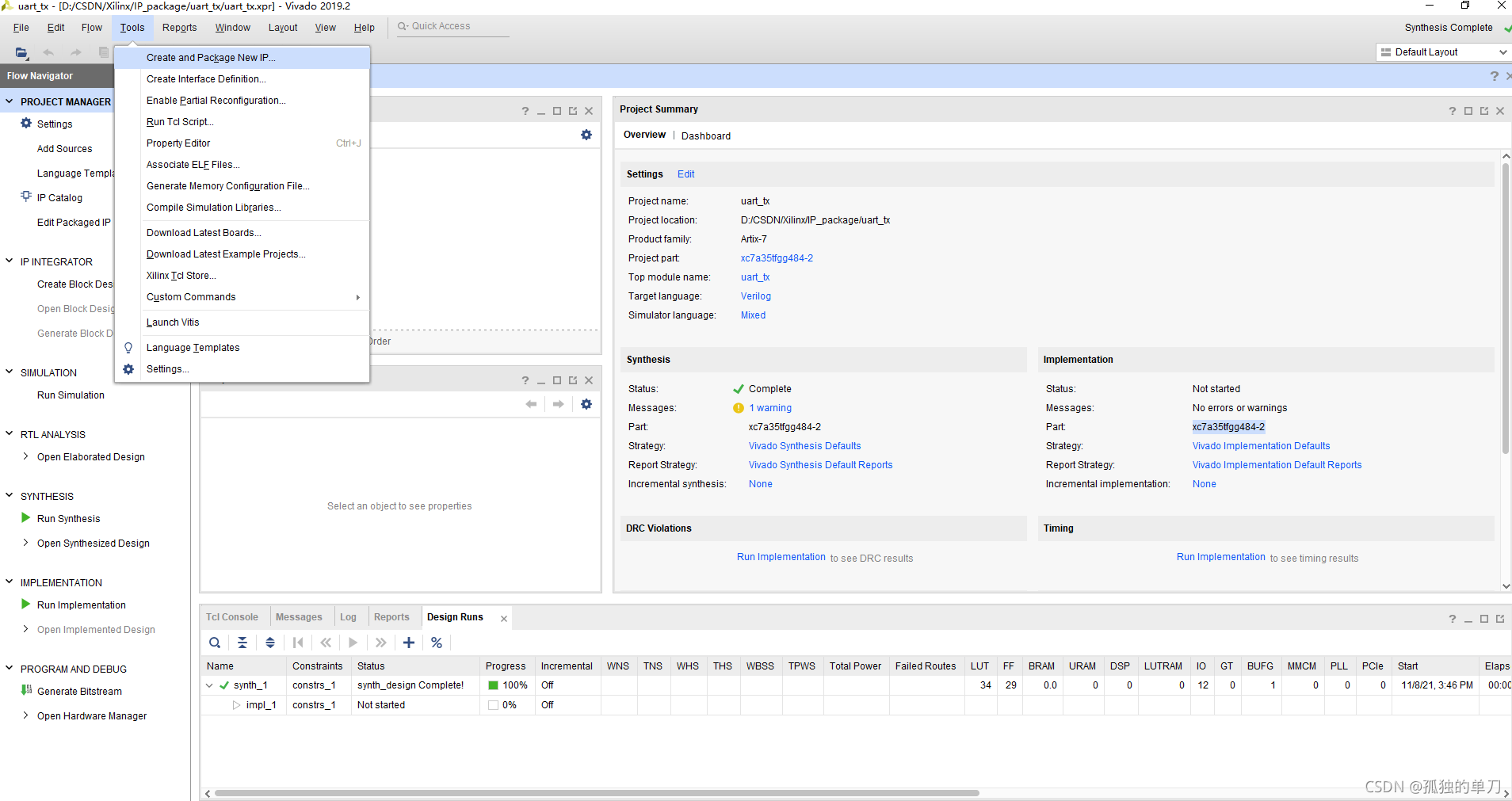

2、點擊Tools-----create and package new ip

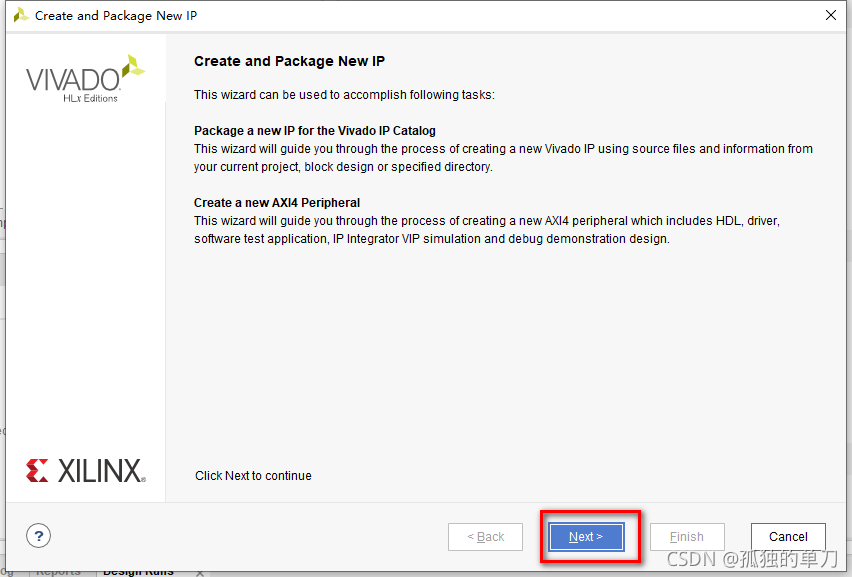

3、點擊Next

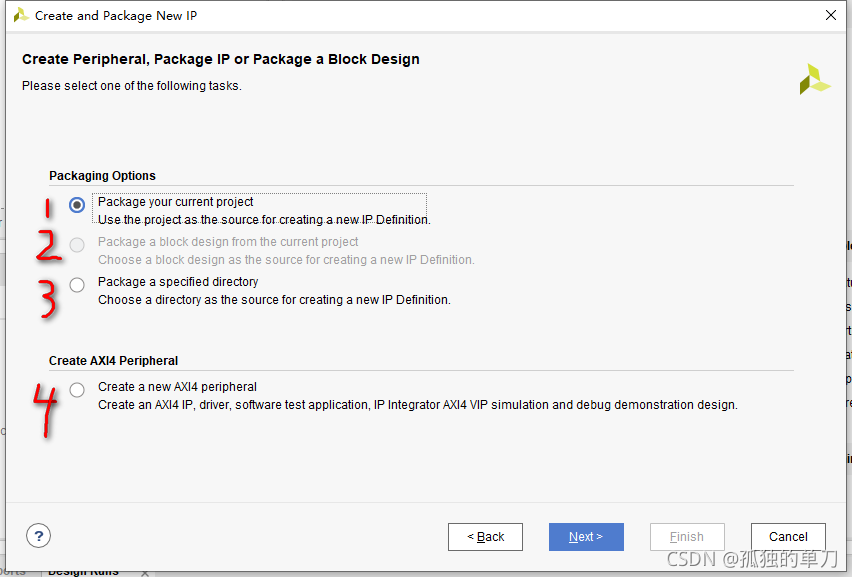

4、選擇選項1,點擊Next,各選項含義:

1---將當前工程打包為IP核

2----將當前工程的模塊設計打包為IP核

3----將一個特定的文件夾目錄打包為IP核

4----創建一個帶AXI接口的IP核

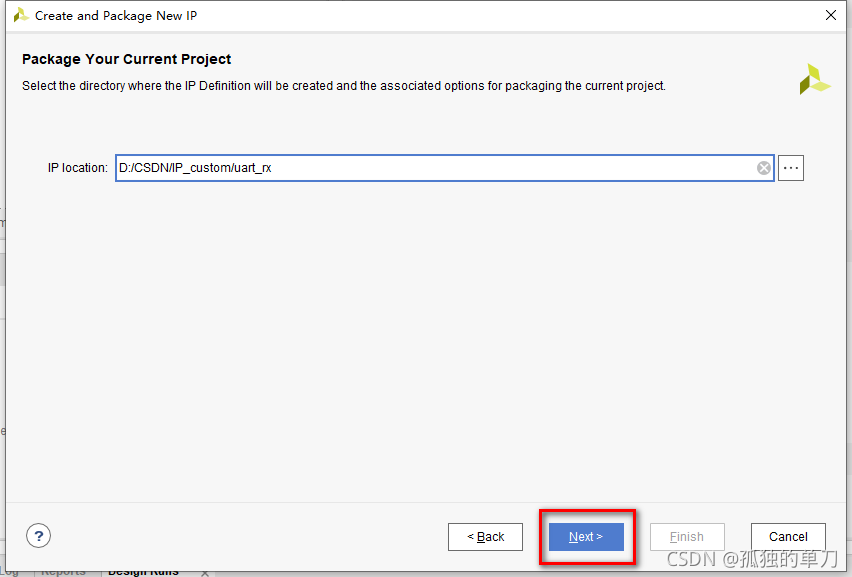

5、選擇IP存放路徑,建議專門建一個文件夾來管理所有建立的IP核,然后點擊Next

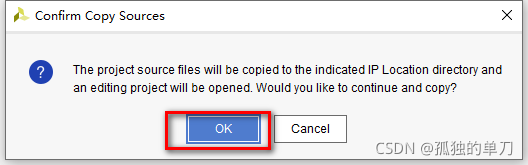

6、點擊OK,然后點擊NEXT,會自動創建一個新工程,用來生成IP核

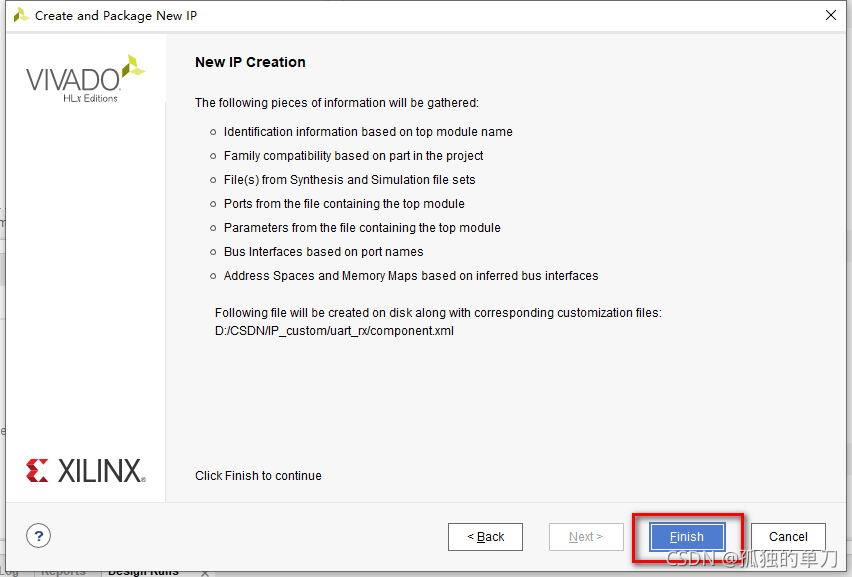

7、新生成的IP核打包工程如下:

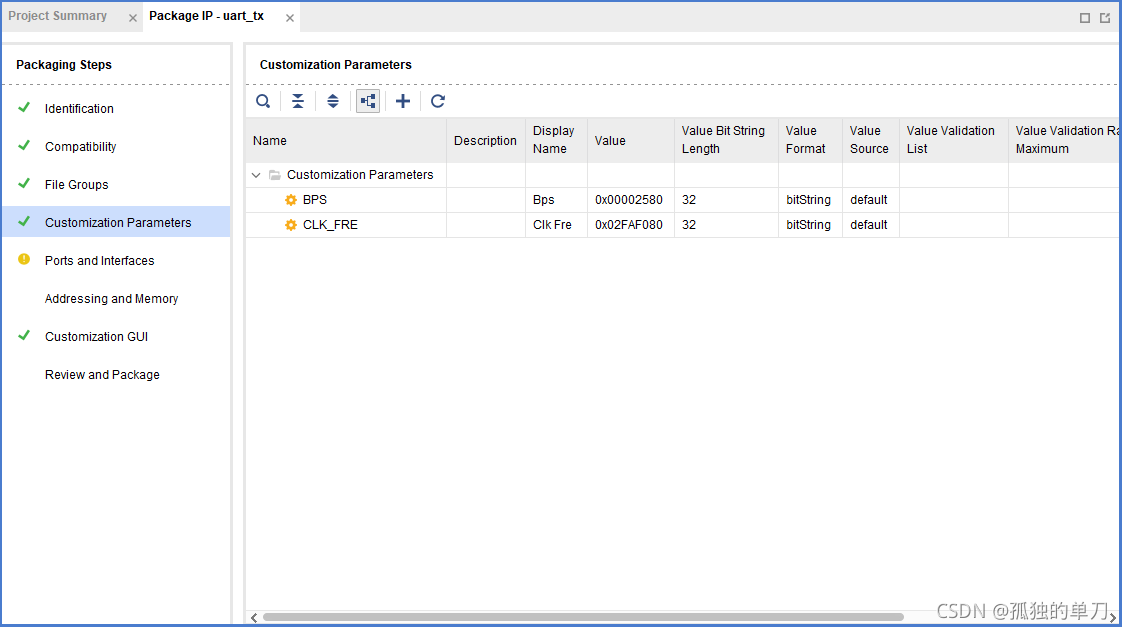

在右邊的界面可以配置一系列參數:

Identification:主要是一系列信息,如IP名字,開發者、版本號等。因為本文僅作示范,所以我這邊所有信息都沒改

compatibility:兼容的系列,這里根據自己需求添加所需要的系列芯片就好了。我這邊保持默認

file groups:IP核的文件架構,可以添加或刪除文件。比如添加仿真文件、例化文件,說明文件等。我這邊保持默認

Customization Parameters:定制化參數。可對參數進行自己的配置,如參數名稱啊,類型啊,自定義區間,可選列表等。

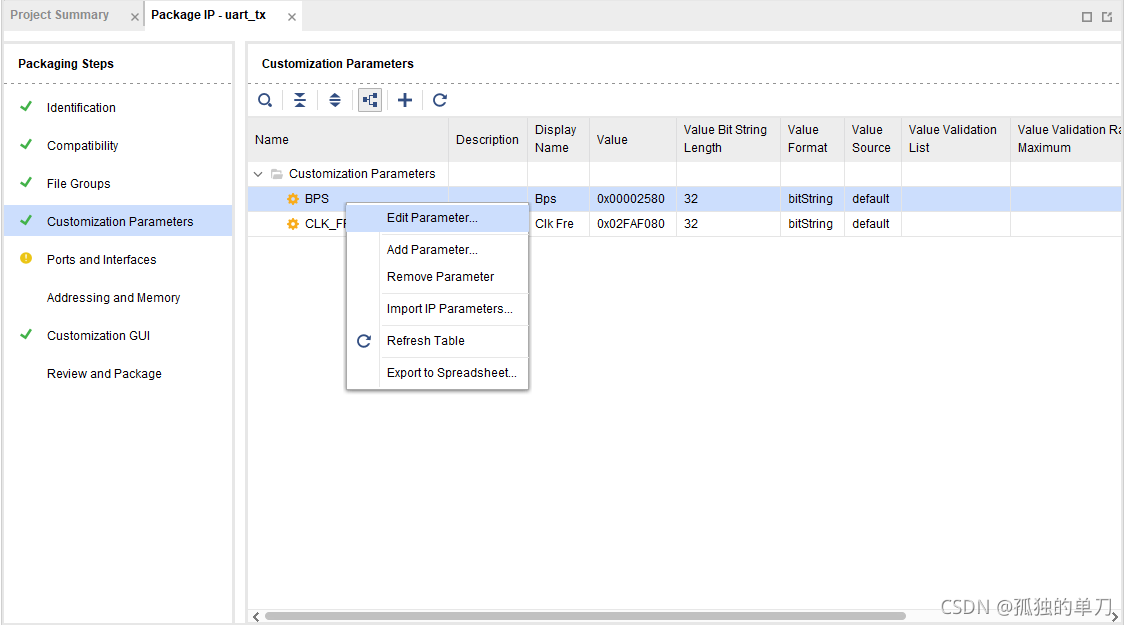

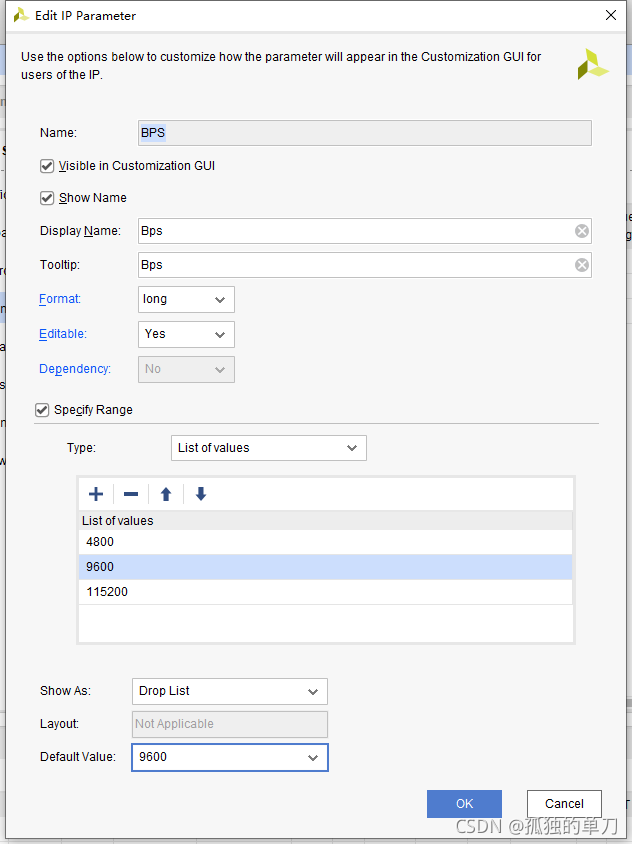

點擊BPS----edit parameter,對參數進行配置(該參數為串口模塊的波特率)

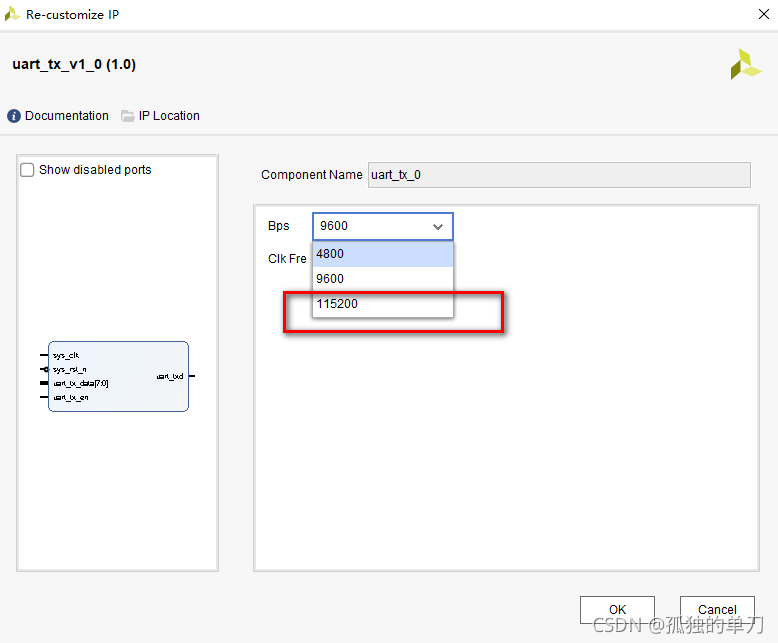

將格式Format改為long類型,再勾上Specify Range,Type改成List of values,再添加3個參數(僅作示范)--4800、9600、115200。再將默認值Default value改為9600。這樣就將該參數配置成了可選參數,默認9600,可選值:4800、9600、115200。

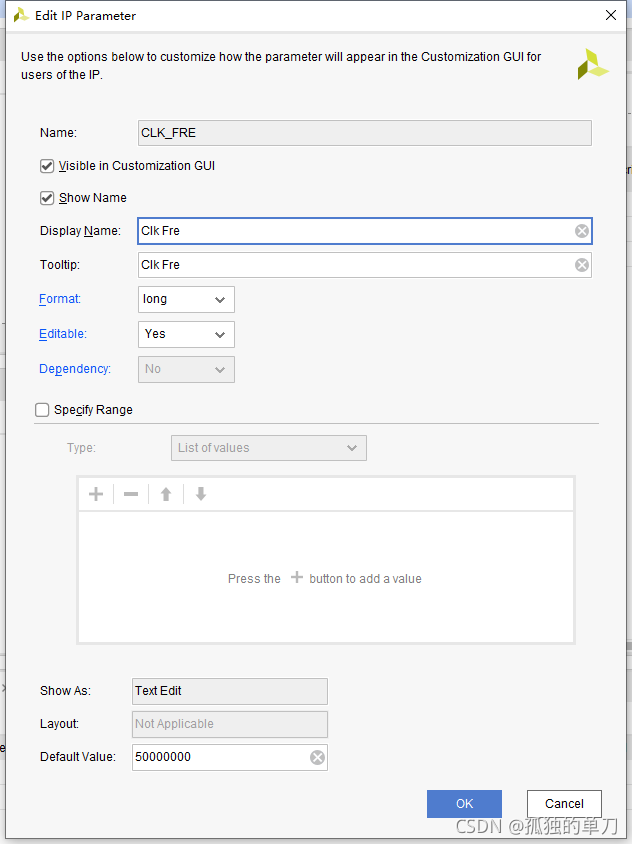

再使用同樣的方法將參數CLK_FRE(模塊時鐘頻率)改為long類型,默認50000000.

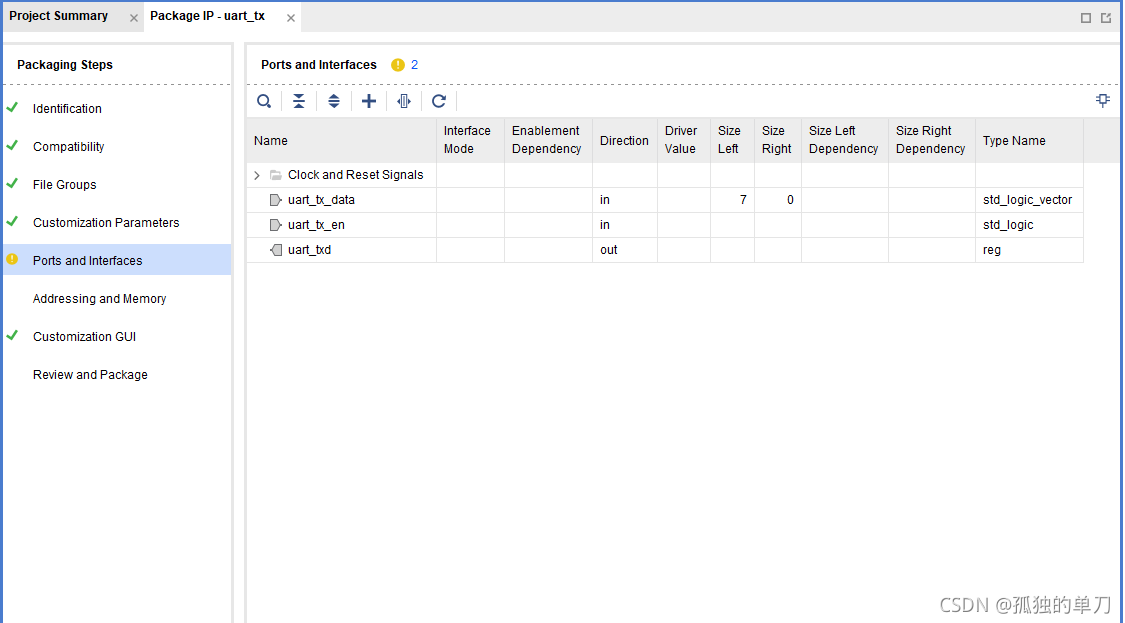

Ports and Interfaces:這里展示了IP的接口,可根據需求添加、刪除接口或者總線。

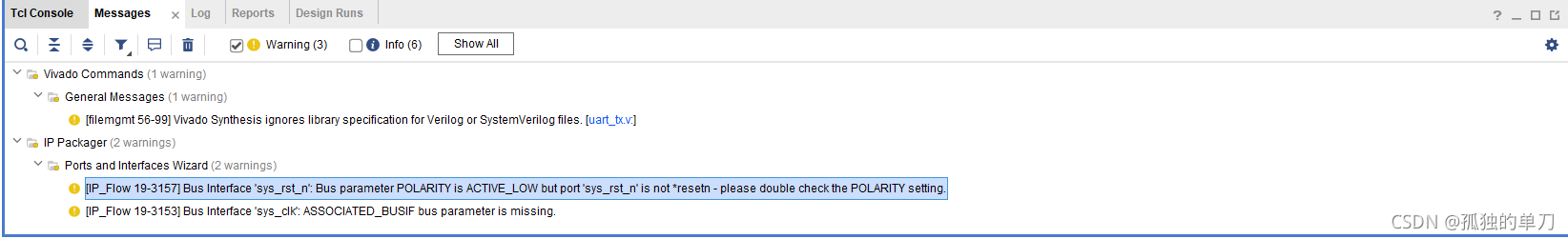

需要說明的是,這里很容易報警告:

這個警告是因為IP核打包器在設計中推斷出了時鐘端口或是復位端口。例如:如果信號名稱包含以下任何一種:[ ]clk,[ ]clkin, [ ]clock[ ], [ ]aclk 或 [ ]aclkin,那么IP打包器就會為將其判斷成為時鐘接口。被自動判斷出的接口,IP打包器會傾向于認為你使用AXI接口來處理這個信號,因為IP打包器工具主要是針對于AXI接口。所以如果你的IP中并不使用AXI總線,這兩條警告可以直接忽略,在實際的IP中不會有任何的影響。

Addressing and Memory:地址分配和儲存映射。本設計用不到,直接跳過,感興趣的可以看XILINX的手冊UG1118。

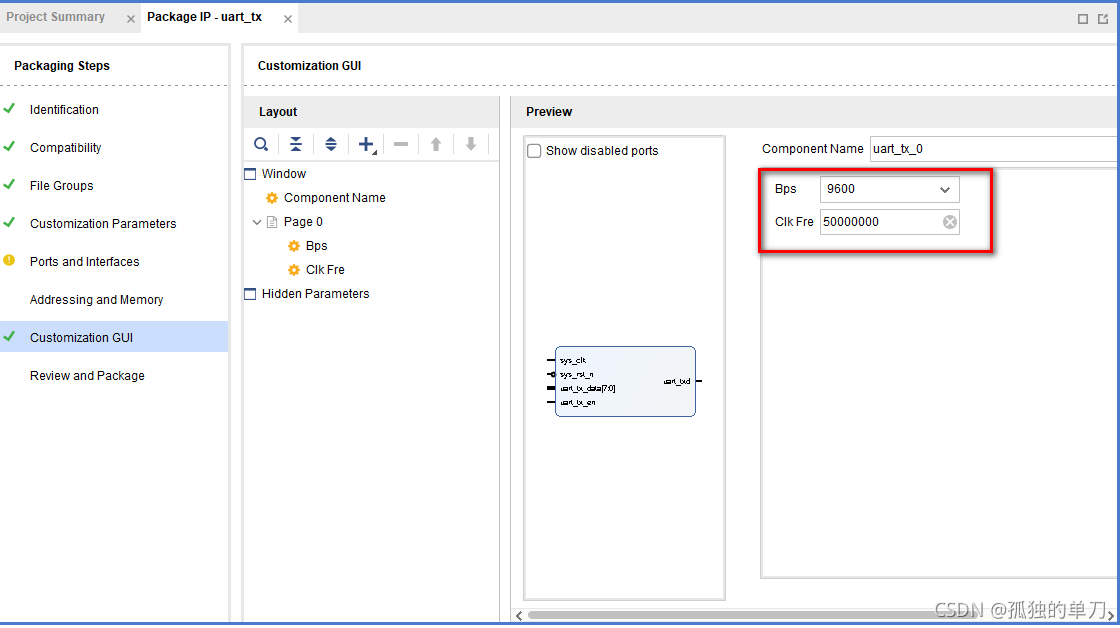

Customization GUI:參數設置的GUI界面。可以對以后配置IP核的界面做一個修改。可以看到,紅框內的參數都是我設置好的默認值。

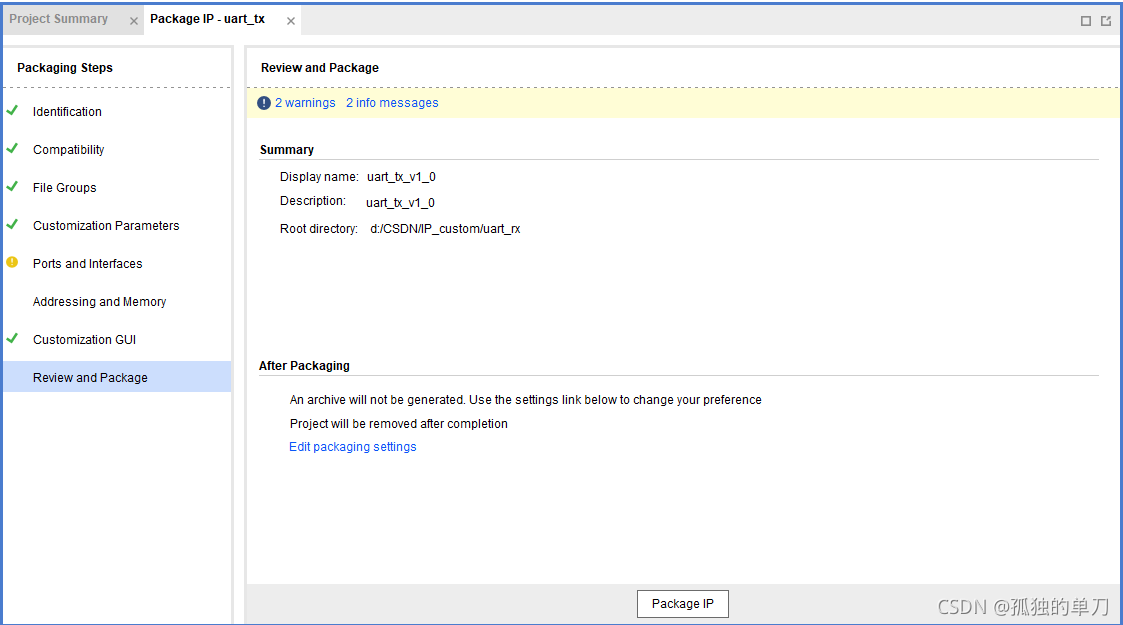

Review and Package:IP核總覽及生成界面。點擊Package IP完成IP打包

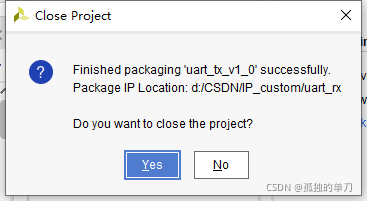

IP核成功打包,如下:

打包串口接收模塊uart_rx

使用同樣的方法把串口接收模塊也打包成IP。

調用

接下來分別調用這兩個IP核,構成串口接收--發送循回,依次驗證IP核打包及調用是否成功。

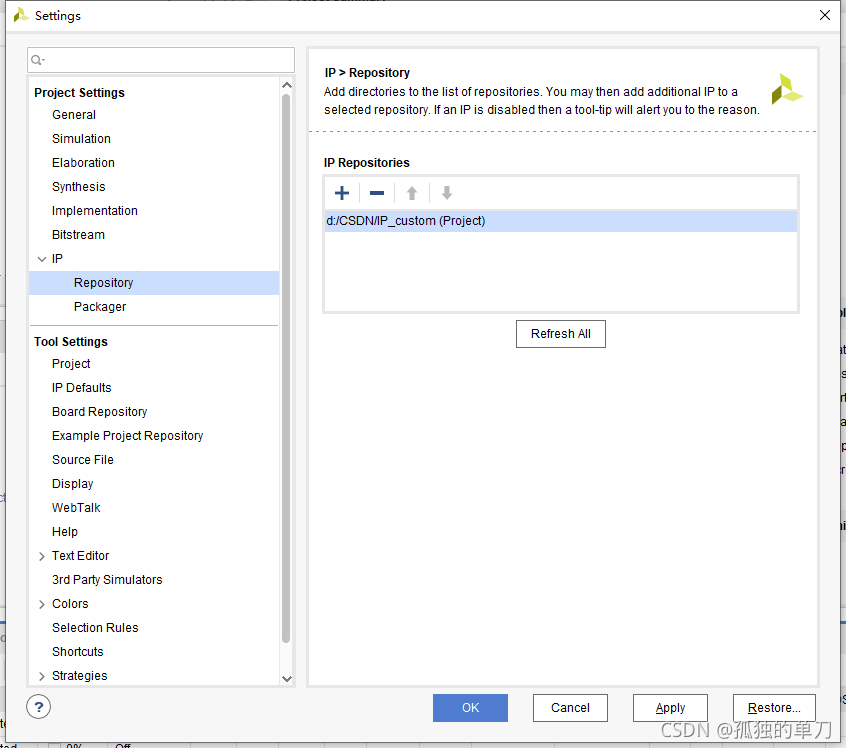

首先新建一個工程,點擊Settings----IP----Repository, 添加IP核所在路徑:

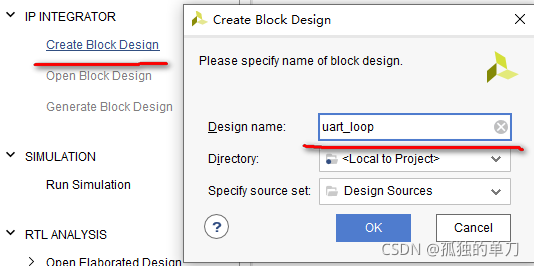

點擊 create block design,新建一個BD模塊,建議名稱與項目名稱一致。

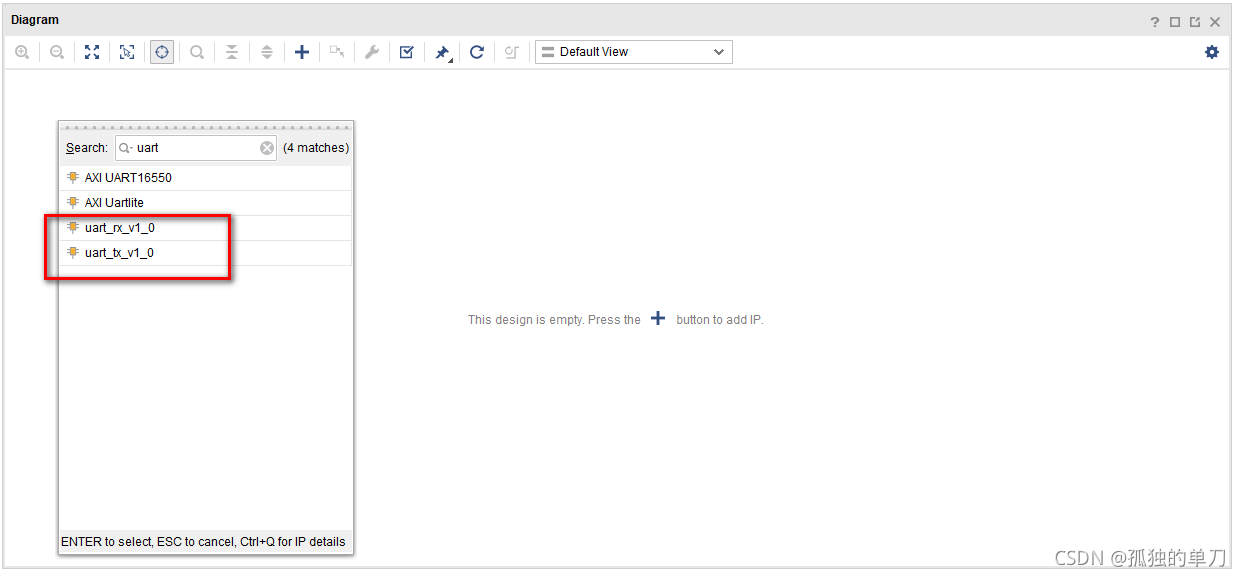

在BD編輯窗口添加IP,搜uart就出現了我們打包的兩個IP核:

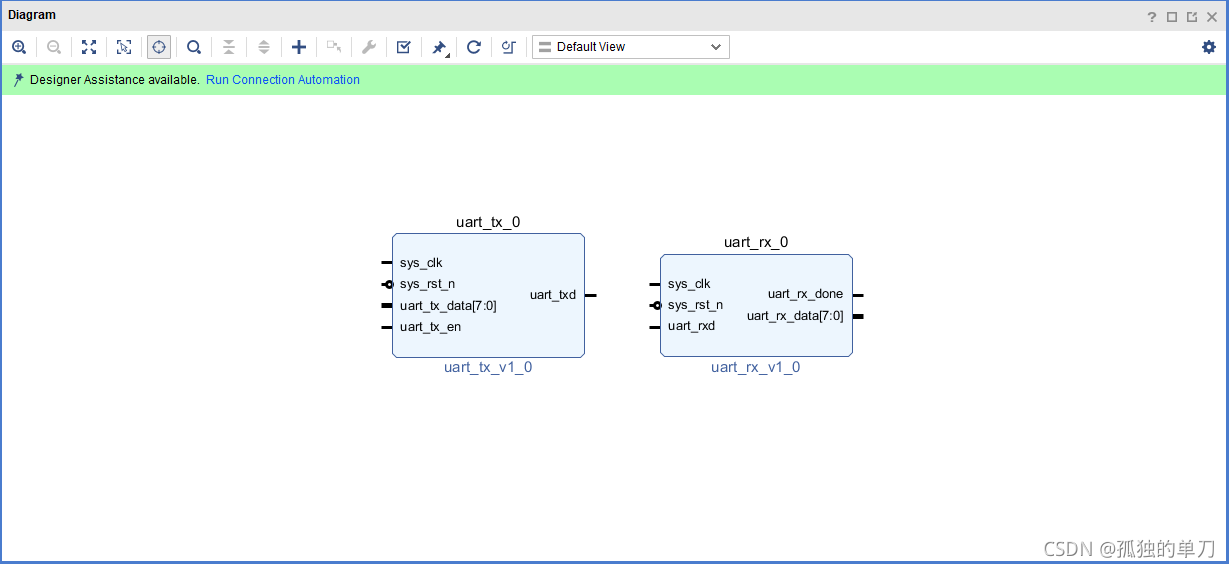

分別添加串口發送模塊和串口接收模塊:

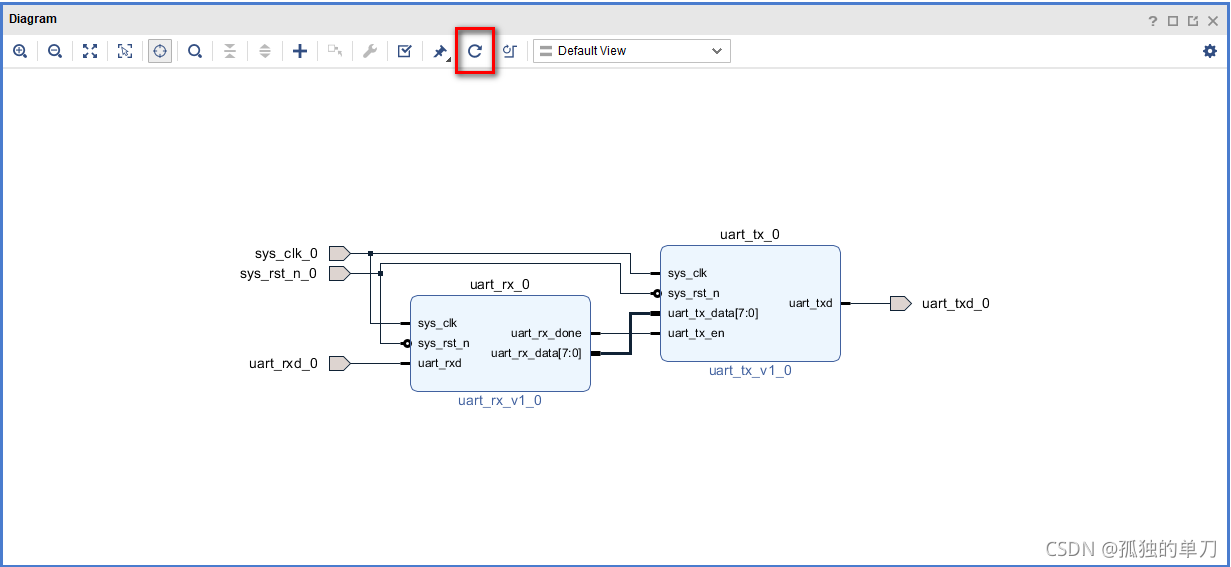

把對外的四個端口(clk,rst,txd,rxd)引出來,右擊sys_clk,點擊make external ,其他三個端口操作一致;再把對應的線連接,然后點擊regenerate layout:

這里我們的 Block Design 就設計完成了,在 Diagram 窗口空白處右擊,然后選擇“Validate Design” 驗證設計。驗證完成后彈出對話框提示“Validation Successful”表明設計無誤,點擊“OK”確認。最后按 快捷鍵“Ctrl+S”保存設計。

接下來在 Source 窗口中右鍵點擊 Block Design 設計文件“system.bd”,然后依次執行“Generate Output Products”和“Create HDL Wrapper”。

然后添加管腳約束,生成bit流文件。

測試

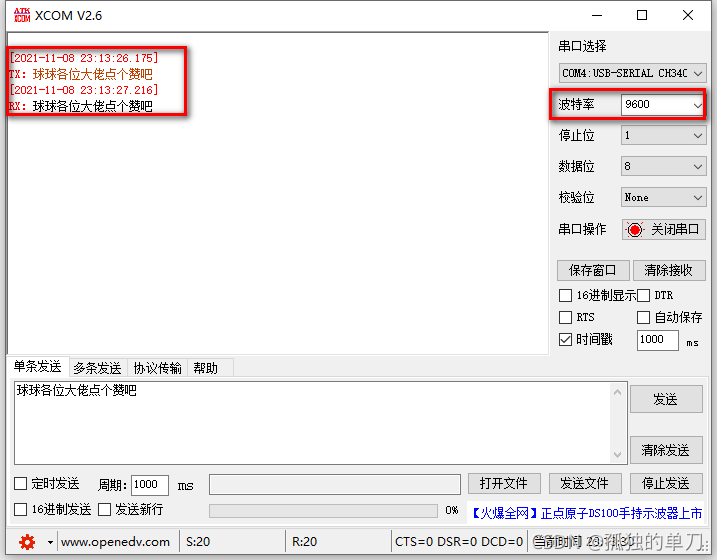

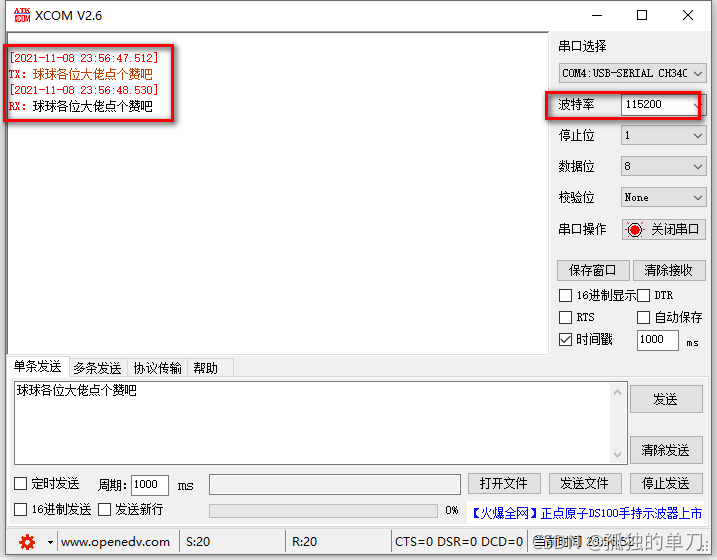

下載bit流文件,使用串口調試助手發送一包數據給FPGA,理論上FPGA馬上回相同的信息給串口調試助手(此時串口波特率9600):

返回設計階段,點擊IP核框圖,將波特率改為115200,如下:

重新生成并下載bit流文件,使用串口調試助手發送一包數據給FPGA,理論上FPGA馬上回相同的信息給串口調試助手(此時串口波特率115200):

參考資料:

UG1118----Creating and Packaging Custom IP

米聯客----XILINX 7 系列 FPGA 基礎入門

審核編輯:符乾江

-

IP核

+關注

關注

4文章

335瀏覽量

50244 -

Vivado

+關注

關注

19文章

823瀏覽量

67869

發布評論請先 登錄

相關推薦

一文詳解Video In to AXI4-Stream IP核

Vivado FIR IP核實現

ALINX發布100G以太網UDP/IP協議棧IP核

怎么集齊7個云平臺?本文教你!

vivado導入舊版本的項目,IP核心被鎖。

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

芯驛電子ALINX推出全新IP核產品線

教你打包一個自己的Vivado IP核

教你打包一個自己的Vivado IP核

評論