注:本文轉自賽靈思中文社區論壇,源文鏈接在此。本文原作者為XILINX工程師。

以下為個人譯文,僅供參考,如有疏漏之處,還請不吝賜教。

本篇博文是面向希望學習使用 Vivado 進行 FPGA 設計輸入的新手的系列博文第一講。

這些實踐旨在為用戶提供快速入門指導,幫助其簡要了解工具流程原理。我們選擇了一項非常簡單的設計,便于讀者理解流程中的不同步驟。

這些實踐將按如下順序展示:RTL 流程、基于 IP 的流程、基于 HLS 的流程、基于 IP integrator 的流程,最后是混用前述流程創建設計。

第一項實踐是 RTL 流程。 每個步驟都包含截屏,以便用戶自行嘗試時參考。

步驟如下:

1.調用 Vivado。

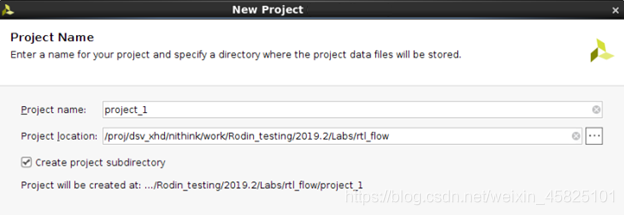

2.用戶提供自己選擇的工程名稱(該工具使用的默認工程名稱為 project_1),并提供工程創建路徑,然后單擊“下一步 (Next)”。

3.默認情況下,該工具會選中“選擇 RTL 工程 (Select RTL Project)”,然后單擊“下一步 (Next)”。

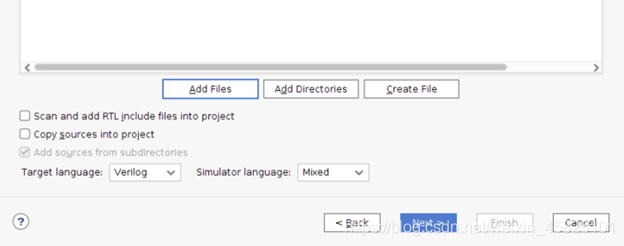

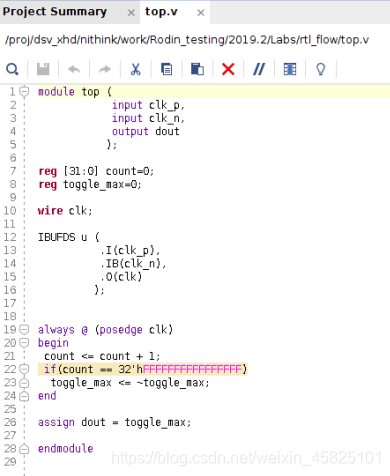

4. 該工具會提示您選擇“Add Sources”以添加源文件。選擇“添加文件 (Add Files)”,然后提供此處隨附的 RTL 文件 (top.v)。

單擊“下一步 (Next)”。

以下提供了 RTL 的詳細信息:

RTL 用于描述自由運行的簡單 32 位計數器。當該計數器達到其最大值時,就會翻轉觸發器。此觸發器連接到輸出。

這樣會使用另一個緩沖器 (IBUFDS) 來創建時鐘差分對,其輸出將在設計中使用。在下一節中,我們將講解為何使用此緩沖器。

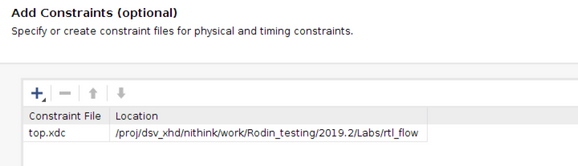

5. 您將看到“添加約束 (Add Constraints)”對話框,其中包含“添加 (Add Files)”選項。

選擇“Add Files”,提供此處隨附的 top.xdc,然后單擊“Next”。

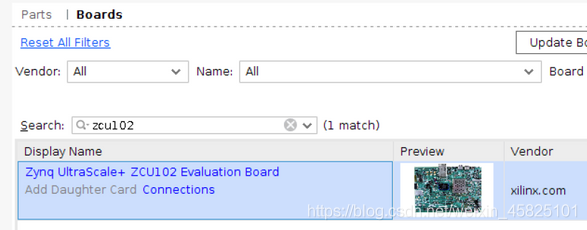

6.單擊開發板選項卡,搜索 zcu102,然后選擇此處顯示的開發板(Zynq UltraScale+ ZCU102 評估板)。

單擊“下一步 (Next)”。

7.在以下窗口中,單擊“完成 (Finish)”。

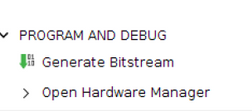

8.在左側,您將看到“生成比特流 (Generate Bitstream)”按鈕。

單擊此按鈕。

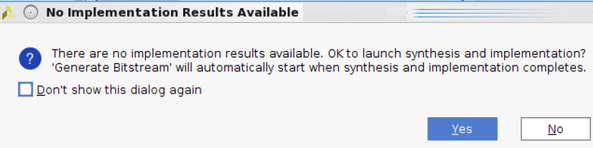

9.這樣將顯示如下提示:

單擊“是 (Yes)”。這樣將彈出另一條提示,要求您啟動運行。單擊“OK”。

這樣就會觸發綜合 (Synthesis),然后實現 (Implementation),并且將生成比特流。

實踐至此完成。

XDC 文件內容:

XDC 文件包含:

create_clock -name clk_p -period 8 [get_ports clk_p]

set_property LOC G21 [get_ports clk_p]

set_property LOC AG14 [get_ports dout]

set_property IOSTANDARD LVCMOS18 [get_ports dout]

set_property IOSTANDARD DIFF_HSTL_I_18 [get_ports clk_p]

使用 IBUFDS 的原因:

使用 IBUFDS 的原因是因為我們選擇的開發板需要差分時鐘。

每塊開發板都有其自己特定的管腳 LOC 及其支持的系統時鐘頻率。

此開發板支持 300Mhz 和 125Mhz,因此我們使用 125Mhz 和與之對應的管腳 LOC。輸出連接至 LED,其 LOC 為 AG14。最后 2 條語句用于指定端口的 IOSTANDARD。

審核編輯:符乾江

-

RTL

+關注

關注

1文章

385瀏覽量

59989 -

Vivado

+關注

關注

19文章

815瀏覽量

66931

發布評論請先 登錄

相關推薦

每次Vivado編譯的結果都一樣嗎

Vivado使用小技巧

LLC輸入功率與什么有關系

差分放大電路同相輸入和反相輸入怎么看

如何判斷同相輸入端和反相輸入端

單端輸入和雙端輸入的區別是什么

與非門的閑置輸入端如何處理

差模輸入信號的概念、原理及應用

差分放大電路單端輸入和雙端輸入的區別

PLC輸入設備有哪些

詳解Vivado非工程模式的精細設計過程

Vivado 設計輸入紀事—RTL 設計輸入

Vivado 設計輸入紀事—RTL 設計輸入

評論