易靈思在通過JTAG寫入Flash時,需要手動創建一個打通JTAG到Flash的bridge,這里我們來介紹下工程創建過程和燒寫操作。

一、創建spi_flash_loader工程

1、在工程安裝路徑"C:Efinity2021.2ipmipefx_spi_loadersource"有用于打通JTAG與Flash路徑的源文件。

2、復制工程安裝路徑 "...Efinity2021.2ipmipefx_spi_loaderfpgaT8Q144_eng_board"下的demo工程到相應的位置,并打開。

3、添加約束C:Efinity2021.2ipmipefx_spi_loaderfpgaconstraint

4、修改需要配置的器件 ;

4、把步驟1中的source文件添加到工程中。

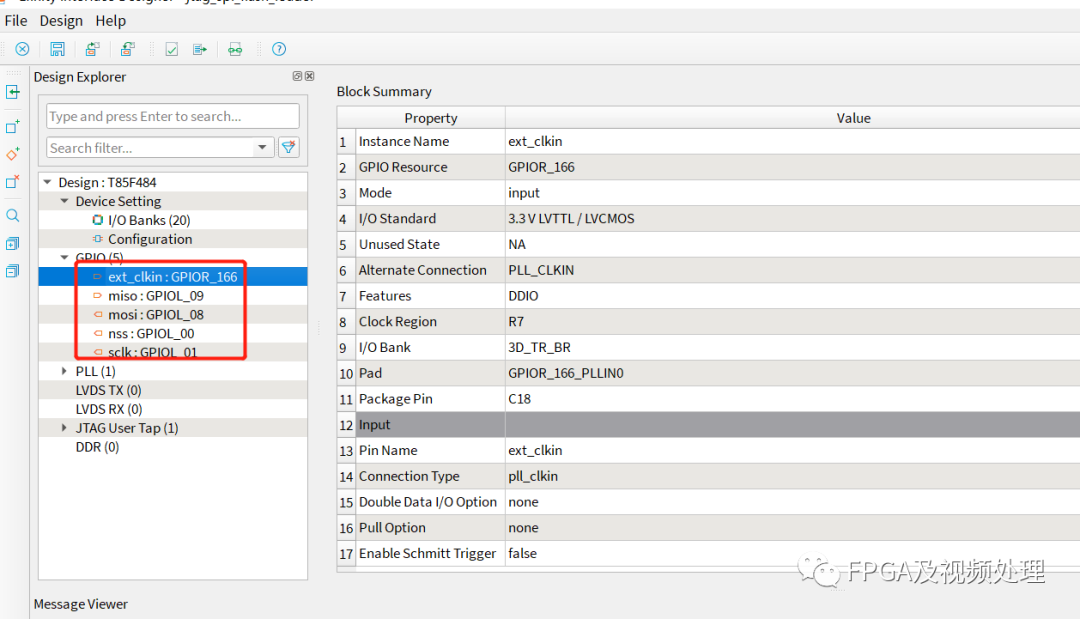

5、修改interface designer中時鐘。trion FPGA沒有內部振蕩器,所以需要外部時鐘;主要保留ext_clkin,miso,mosi,nss,sclk等信號。另外注意修改pll的輸入輸出時鐘,其中ext_clkin是pll的參考時鐘,Bridge使用的時鐘頻率最好不要超過50兆

6、刪除每個module部分的“'IP_MODULE_NAME”module,如下操作:

把 `IP_MODULE_NAME(adbg_crc32) (clk, data, enable,...);修改成 adbg_crc32(clk,data,enable,...);

7、修改top module信號定義。把用不到的信號屏蔽掉。并在內部重新定義rstn信號并賦值為1。

moduleefx_spi_loader_top(//System// input rstn,input clkin,// input locked,// SPI flash interfaceinput miso,// input miso_1,output sclk,output nss,// output nss_1,output mosi,// output mosi_1,// output wp_n,// output hold_n,);... ...wire rstn;assign rstn =1'b1;8、添加約束。

9、編譯即可以生成

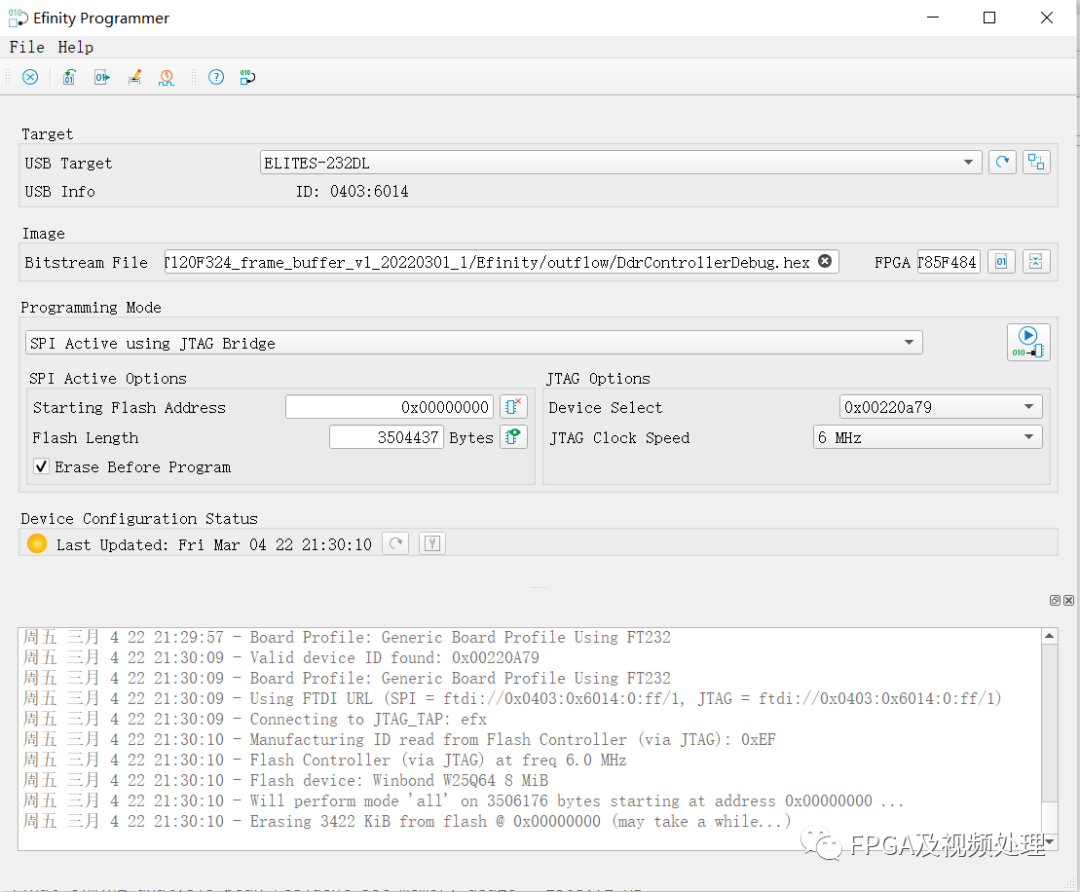

10、燒寫過程先在programmer中選擇jtag模式,配置spi_flash_loader.bin文件,完成之后,再選擇工程的hex文件,并把programming mode中的SPIActive usingJTAG Bridge

目前發現修改了FIFO的深度可能造成Flash的讀取驗證不成功。所以如果在小器件,比如T8上發現存在資源不夠,可以把和mosi_1,miso_1相關的模塊屏蔽。

parameter WFIFO_DEPTH = WFIFO_DEPTH_256 * 256;parameter RFIFO_DEPTH = RFIFO_DEPTH_256 * 256;審核編輯:郭婷

-

振蕩器

+關注

關注

28文章

4014瀏覽量

140870 -

易靈思

+關注

關注

5文章

57瀏覽量

5220

原文標題:易靈思spi_flash_loader工程創建

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

易靈思(Elitestek)FPGA編程器功能特點及驅動安裝方法

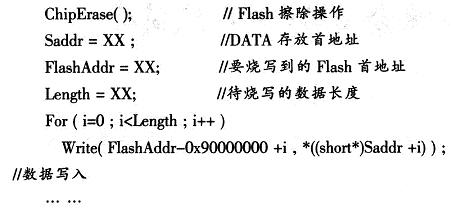

基于CCS的DSP片外Flash直接燒寫設計

JTAG接口在線燒寫Flash的實現

FPGA配置– 使用JTAG是如何燒寫SPI/BPI Flash的?

易靈思JTAG寫入Flash工程的創建過程和燒寫操作

易靈思JTAG寫入Flash工程的創建過程和燒寫操作

評論