本文提供一種校準數模轉換器(DAC)的方法,專用于引腳電子器件驅動器、比較器、負載、PMU和DPS。DAC具有差分非線性(DNL)和積分非線性(INL)等非線性特性,我們可以通過增益和偏置調整來盡可能降低這些特性。本文描述如何執行這些校準,以改善電平設置性能。

自動化測試設備(ATE)描述用于一次對單個或多個器件執行單次或一系列測試的測試儀器。不同類型的ATE測試電子器件、硬件和半導體器件。定時器件、DAC、ADC、多路復用器、繼電器和開關都是測試儀或ATE系統中的支持模塊。這些引腳電子器件可以利用精確的電壓和電流提供信號和電源。這些精密信號通過電平設置DAC進行配置。在ATE產品系列中,有些引腳電子器件包含校準寄存器,有些校準設置存儲在片外。本文介紹DAC的功能、誤差,以及如何通過增益和偏置調整進行校準。

數模轉換器(DAC)

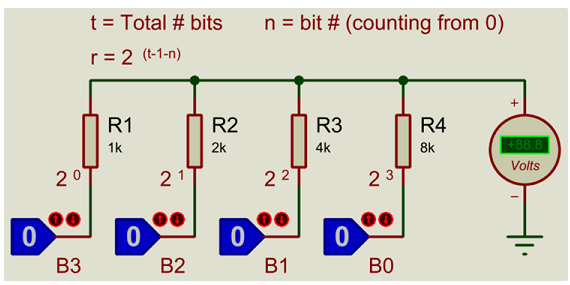

DAC是一種數據轉換器,用于將數字輸入轉換為相應的模擬輸出電平。一個N位DAC可以支持2N個輸出電平。位數越高,DAC輸出分辨率越高。

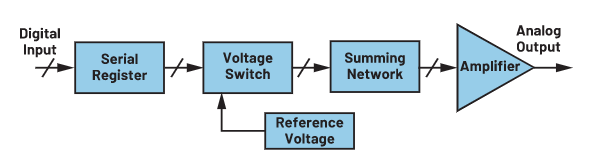

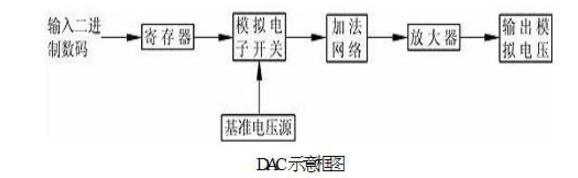

圖1. 數模轉換器(DAC)框圖。

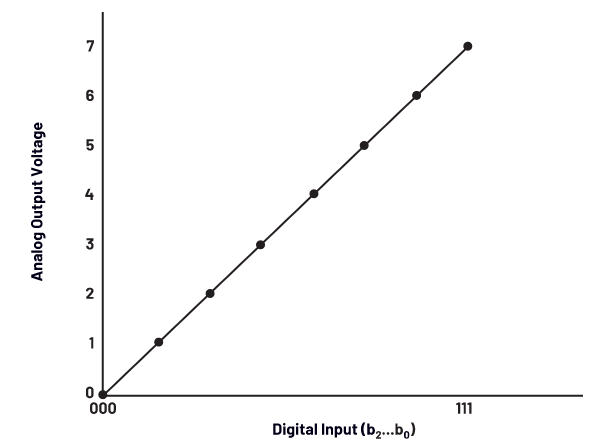

首先,N位數字輸入提供給DAC串行寄存器。電壓開關和電阻求和網絡將數字輸入轉換為模擬輸出電平。DAC圖的轉換特性如圖2所示。對于3位DAC,23個數字輸入生成8個模擬輸出電平。

圖2. 3位DAC的理想轉換函數。

DAC誤差

在現實世界中,轉換器并不理想。由于電阻值、插值和采樣的誤差,DAC的轉換函數并不是一條直線,或是線性的。這些誤差被稱為差分非線性(DNL)和積分非線性(INL)。DNL是輸出電平與理想步長之間的最大偏差,它由兩個連續輸出電壓電平之間的差值得出。INL是輸入/輸出特性與理想轉換函數之間的最大偏差。通過增益和偏置校正,可以減小INL誤差。

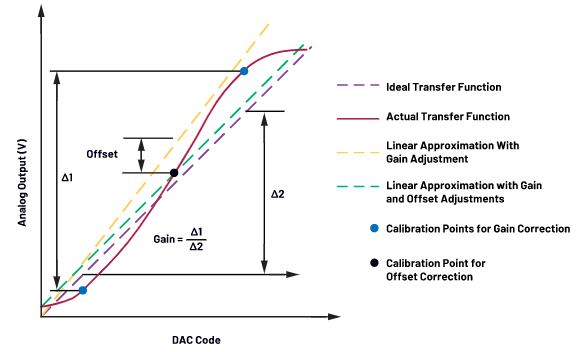

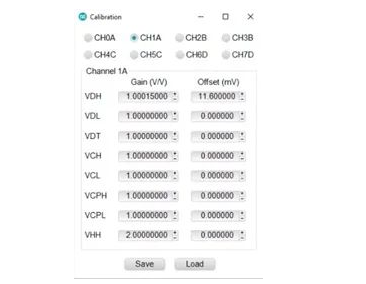

圖3中的INL顯示了實際轉換函數與理想轉換函數之間的偏差。DAC的增益誤差表示實際轉換函數的線性近似斜率與理想轉換函數斜率的匹配程度。在繪圖時,調整增益會影響線性近似角度。偏置誤差是測量值與所選的零偏置點之間的差值。如果調整偏置量,整個線性近似曲線會相應地向上或向下移動。單個代碼的INL是任意給定點上增益誤差和偏置誤差的和。校準之后,一旦增益和偏置誤差降至最低,那么轉換函數會是兩個端點之間的一條線。

圖3. INL誤差轉換函數。

校準程序

用戶可以建立校準程序,利用增益和偏置校正來降低DAC的非線性。以下步驟詳細說明了示例校準程序的每個步驟。

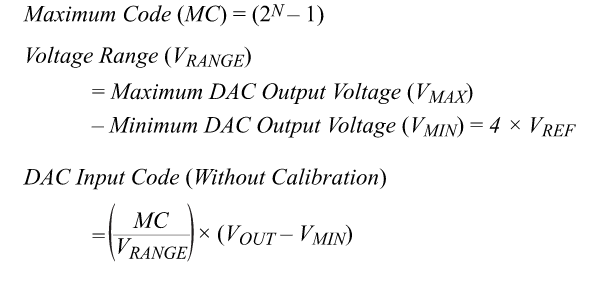

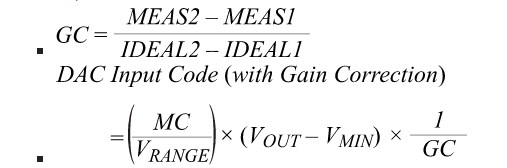

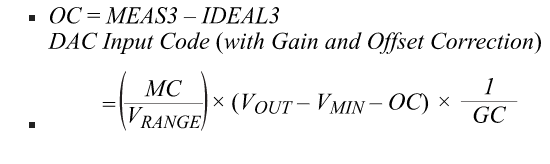

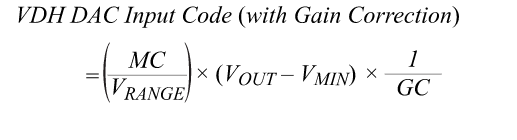

對于N位DAC:

增益校正(GC):

在最低和最高二進制值時,DAC的線性度會降低。因此,建議在外部二進制值或EC表推薦的校準點之間的5%至10%范圍內選擇校準點。進行以下計算時,我們假設選擇5%的校準點。

將DAC輸入設置為高于最低二進制值5%。計算預期的電壓輸出并將其記錄為IDEAL1。測量輸出電壓,并將其記錄為MEAS1。

將DAC輸入設置為低于最高二進制值5 %。計算并記錄IDEAL2。測量輸出電壓,并將其記錄為MEAS2。

偏置校正(OC):

所需的零偏置點因應用而異。用戶應該根據自己的應用定義最佳值。有些用戶可能喜歡使用0V來獲得準確的接地參考點。有些用戶喜歡使用操作范圍的中間值來盡量減少總體INL誤差。

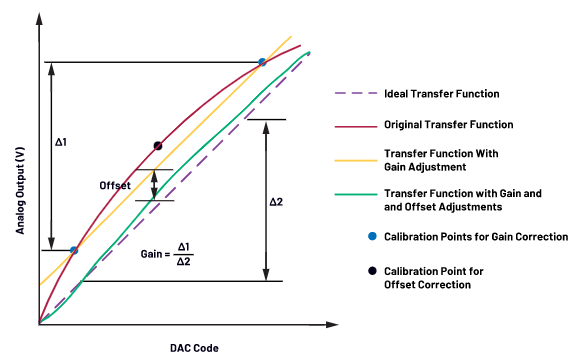

對電壓-代碼公式的斜率應用DAC增益校正,以確立單位增益。

選擇所需的零偏置電壓點并將其記錄為IDEAL3。使用更新后的電壓-代碼公式計算代碼。編程設置計算得出的代碼,然后測量輸出電壓,并將其記錄為MEAS3。

示例1

以MAX32007為例,它是一個八通道DCL,集成了電平設置DAC和PMU開關。MAX32007具有內部DAC,用于設置VDH、VDL、VDT/VCOM、VCH、VCL、VCPH和VCPL的電平。這些DAC沒有內部校準寄存器。校準DAC時,請遵循以下步驟:

按照評估套件數據手冊中的說明,啟動MAX32007評估(EV)套件。

將SMB連接器DATA0A和NTRM0A連接至1.2 V。

通過50 Ω端接裝置,將SMB連接器NDATA0A和TRM0A接地。

使用USB電纜,將評估套件連接至Windows? 10 PC。打開MAX32007評估套件軟件(GUI)。

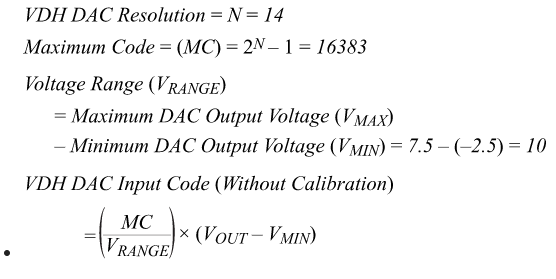

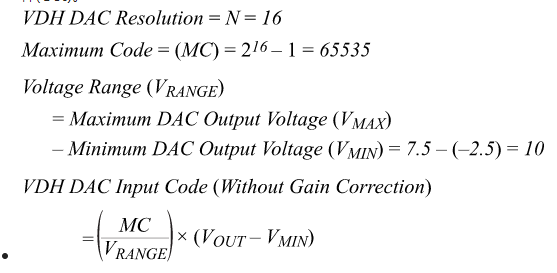

采用圖4所示的DAC電壓電平和驅動器設置。注意,最低VDH DAC工作電壓值為–1.5 V,最高工作電壓值為4.5 V;在本例中,零偏置點值為1.5 V。

圖4. 使用評估板軟件設置MAX32007的DAC電平。

施加VDH = –1.5 V,然后測量輸出電壓值。

施加VDH = 4.5 V,然后測量輸出電壓值。

增益校正 = 測量輸出電壓值之間的差值/理想值之間的差值。例如,(4.501–(–1.497))/(4.5–(–1.5)) = 0.999667。

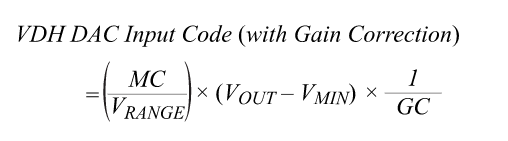

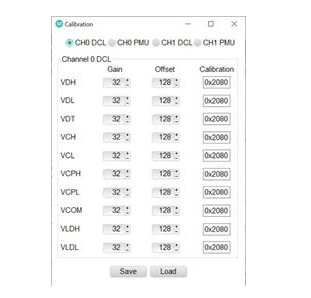

要應用增益校正,打開菜單 → 選項 → 校準,如圖5所示。

圖5. MAX32007 DAC的校準菜單。

圖6. 帶校準寄存器的DAC的INL誤差校正。

施加VDH = 1.5 V(包含增益校正代碼),然后測量輸出電壓值。

偏置校正 = 測量輸出值–理想值。例如,(1.502–1.5) = 0.002。

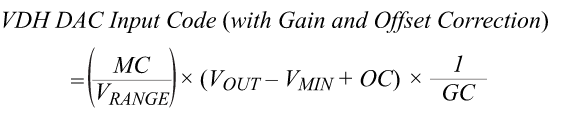

在執行增益和偏置校正之后,

示例2

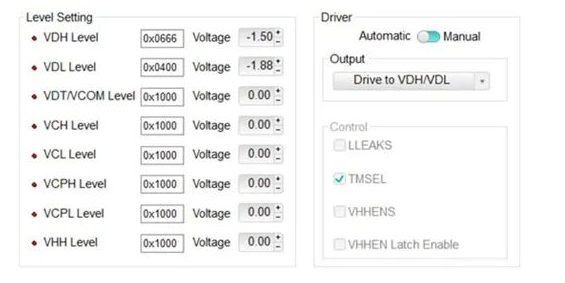

以 MAX9979為例,它是一個八通道DCL,集成了電平設置DAC和 PMU。MAX9979包含內部DAC,用于設置VDH、VDL、VDT、VCH、VCL、VCPH、VCPL、VCOM、VLDH、VLDL、VIN、VIOS、CLAMPHI/VHH和CLAMPLO的電平。這些DAC具有內部校準寄存器。在示例1中,調節了DAC輸出代碼,以盡量減少INL誤差。在示例2中,DAC輸入代碼保持不變,校準寄存器調整輸出級緩沖器以盡量減少INL誤差,如圖6所示。要校準DAC,請遵循以下步驟:

按照評估套件數據手冊中的說明,啟動 MAX9979評估套件。

將SMB連接器DATA0A和NTRM0A連接至1.2 V。

通過50 Ω端接裝置,將SMB連接器NDATA0A和TRM0A接地。

使用USB電纜,將評估套件連接至Windows 10 PC。打開MAX9979評估套件軟件(GUI)。

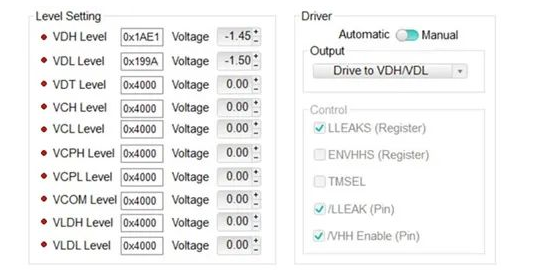

采用圖7所示的DAC電壓電平和驅動器設置。注意,VDH DAC的最低建議值為–1.5 V,最高建議值為4.5 V,零偏置點值為1.5 V。

圖7. 使用評估板軟件設置MAX9979的DAC電平。

施加VDH = -1.45 V,然后測量輸出電壓值。

施加VDH = 6.5 V,然后測量輸出電壓值。

增益校正 = 測量輸出電壓值之間的差值/理想值之間的差值。例如,(6.501 V–(–1.455 V))/(6.5 V–(–1.45 V)) = 1.0007 V。

進行增益校正后,

注意,要執行增益和偏置校正,請轉至菜單 → 選項 → 更改 → 校準,如圖8所示。有關將增益和偏置校正轉換為增益和偏置代碼的更多信息,參見MAX9979數據手冊。

圖8. MAX9979的校準寄存器設置

審核編輯:彭菁

-

寄存器

+關注

關注

31文章

5427瀏覽量

123712 -

連接器

+關注

關注

99文章

15282瀏覽量

139614 -

數模轉換器

+關注

關注

14文章

1057瀏覽量

84038

發布評論請先 登錄

總結DAC——數模轉換器

數模轉換器是什么

介紹DAC數模轉換器以及DMA的使用

DAC數模轉換器的主要特點有哪些

一文看懂理想數模轉換器 (DAC) 的重要屬性

DAC3152/DAC3162數模轉換器(DAC)數據表

DAC63204.DAC53204.DAC43204數模轉換器(DAC)數據表

DAC63202和DAC53202智能數模轉換器(DAC)數據表

關于校準數模轉換器(DAC)的方法

關于校準數模轉換器(DAC)的方法

評論