全球對數據的需求沒有減弱的跡象,并繼續對服務提供商施加壓力,要求他們更快地處理更多比特。這種壓力在大型數據中心中感受到了強烈的壓力,這些數據中心正在應對越來越需要帶寬的趨勢。這些趨勢包括對娛樂流媒體、物聯網應用、與聯網汽車和自動駕駛相關的服務以及具有密集分析的企業數字化轉型的需求增長。

數據中心推動接口演進

迫切需要在整個基礎設施中實現更快的數據傳輸協議,包括處理通過大量通道到達的不斷增加的數據量、存儲和維護數據、檢索和處理數據以及返回結果 - 具有附加值 -給客戶。

負責當今網絡和接口協議的各個機構正在加緊工作,以從他們的標準中獲得下一個性能提升。但是,網絡中不同點之間的過度速度不匹配可能會導致瓶頸。進步的速度需要保持領先,但不同的協議應該以相似的速度向前發展也很重要。

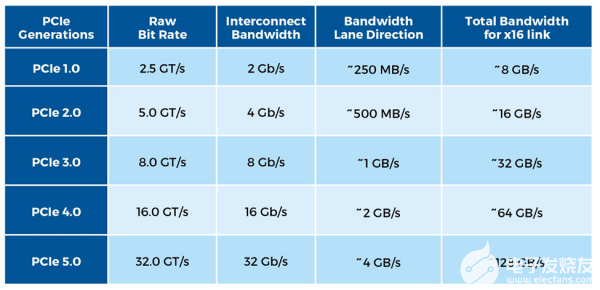

在領先數據中心運營商的需求推動下,PCIexpress? (PCIe?) 的發展大致與不斷發展的多千兆以太網規范保持同步。運營商正在從 100Gbit 以太網轉向在其整個場所采用最新的 400Gbit 連接。為了最大限度地提高所獲得的收益,需要更新更快的 PCIe 代來將數據中心的服務器與本地外圍設備(例如存儲和 AI 加速器卡)連接起來。PCIe 4.0 規范于 2017 年公布,帶寬是上一代的兩倍。隨后在 2019 年發布了 PCIe 5.0,將傳輸速度提高到 32GT/s,從而為 x16 鏈路提供 128GB/s 的總帶寬。

圖 1 總結了各代 PCIe 的總速度。PCI-SIG 已經在開發 PCIe 6.0,預計將在 2021 年完成新規范。PCIe 很可能會繼續成為需要性能的外圍通信的首選協議。

圖 1. PCIe 標準的發展速度與多千兆以太網類似。

PCIe 規范的獨特壽命

PCIe 5.0 產品現已進入市場。但是,舊規格沒有到期日期。向后兼容性是 PCIe 的一個關鍵優勢,它允許早期規范為個人計算、游戲以及一些企業計算和網絡應用程序等機會提供經過驗證的高性能解決方案。

除了按照最新規范設計的設備外,設計人員還需要高度集成的現成 PCIe 芯片,以支持前幾代產品,以利用這些既定且廣泛接受的標準。然后,設計人員可以從幾代 PCIe 中選擇最合適的選項,以實現具有出色性能的實用且價格合理的解決方案。芯片制造商可以繼續利用他們的設計 IP 和對與每一代 PCIe 標準相關的客戶支持技術的投資。

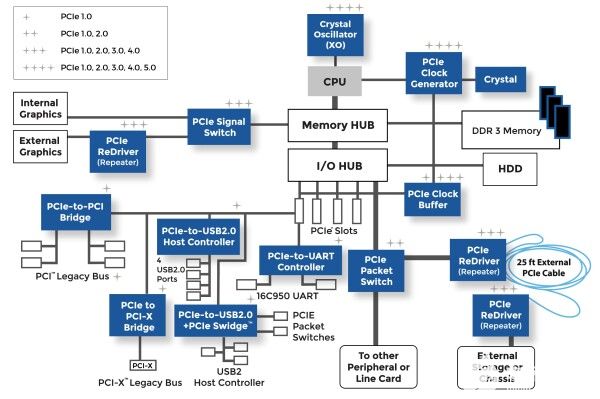

Diodes 有大量標準 IC 可供選擇,為 PCIe 2.0、3.0、4.0 和 5.0 代提供支持(如圖 2 所示)。設計人員可以從中選擇任何一種,為各種應用實現高性能接口。

圖 2. Diodes 產品組合為 PCIe 1.0、2.0、3.0、4.0 和 5.0 提供了全面的選擇。

使用 Diodes 的 PCIe IC 進行靈活設計

如圖 2 所示,橋接器和交換機是 PCIe 架構中的關鍵組件,用于連接各種類型的主機和端點設備。包橋通常在 OSI 參考模型中的兩個層之間或兩個協議之間提供接口。橋接器還可用于連接 PCIe 和傳統 PCI 標準(包括 PCI-X),或連接到 USB 端口或 UART 總線接口。分組交換機是多端口/多通道設備,通常用于將單個根聯合體擴展到多個端口。提供了額外的通道來訪問其他對等系統,例如外圍設備或線卡。Diodes 提供具有各種端口配置和轉換功能的數據包橋接器和交換機。

此外,Diodes 結合了 PCIe 封包開關和 PCIe 至 USB2.0 橋接器的功能,以創建 PI7C9X442SL PCI Express 至 USB 2.0 PCIe Swidge?。這種創新設備可以從一個 PCIe x1 上游端口扇出到兩個 x1 下游端口和四個 USB 2.0 端口,允許從系統主機處理器訪問多個 PCIe 和 USB 設備。

為了提高高速系統中的信號完整性,或者需要通過更長的連接(例如外部顯卡或外部存儲)驅動信號的任何地方,用于 PCIe 2.0、PCIe 3.0 和 PCIe 4.0 的 PCIe ReDriver? 可以使用,如圖 2 所示。ReDriver 使用均衡和預加重等技術補償傳輸線損耗,并包含引入最小延遲的輸出驅動器。其效果是恢復信號余量并最小化抖動,有效地保持接收器的低誤碼率。與重定時器相比,ReDriver 實施起來更容易、更經濟,重定時器集成了包括時鐘和數據恢復在內的附加功能。

此外,Diodes 還擁有一系列無源雙向 PCIe 2.0、PCIe 3.0 和 PCIe 4.0 信號多路復用器/解復用器。這些可用于將單個 PCIe 通道連接到多個通道,例如用于圖形或計算的帶寬擴展,或將系統連接到多協議接口。

Diodes 還具有適用于所有 PCIe 代的時序 IC,由圖中所示的晶體振蕩器、時鐘發生器和時鐘緩沖器功能指示。Diodes 的 PCIe 時鐘發生器可以產生特定的時鐘信號頻率,輸出抖動極低,適用于 PCIe 應用和其他需要類似性能的系統時鐘。時鐘緩沖器采用時鐘發生器參考信號并產生多個輸出以分布在 PCB 上。有多種配置可供選擇,利用 Diodes 的專有 PLL 設計,最大限度地減少抖動以滿足適用的 PCIe 規范。在可用的設備中,Diodes 的 1.8V PI6CG18xxx 時鐘發生器和 1.5V PI6CG15xxx 緩沖器是具有 2、4 和 8 通道配置的 PCIe 4.0 IC。它們的集成功能為每個輸出節省了四個外部電阻,

結論

PCIe 標準處于開發的最前沿,可實現領先的超大規模數據中心所需的高帶寬互連。除了與最快的多千兆位以太網規范緊密匹配的最新一代的高速之外,舊標準的壽命和確保各代之間的向后兼容性使設計人員能夠創建實用、負擔得起和高性能的解決方案消費、桌面和工業用途。支持涵蓋多代標準的廣泛 PCIe 芯片組合(例如 Diodes PCIe 時序芯片、驅動器、ReDrivers、開關和橋接器組合)是成功的重要因素。

-

PCI

+關注

關注

4文章

672瀏覽量

130541 -

PCIe

+關注

關注

15文章

1268瀏覽量

83313

發布評論請先 登錄

相關推薦

Linux文件系統知識點詳解

一文詳解PCIe的知識點

一文詳解PCIe的知識點

評論