汽車原始設備制造商 (OEM) 一直處于移動出行(Mobility)和高級駕駛輔助系統(tǒng) (ADAS) 的前沿,在這個快速發(fā)展的領域爭奪領導地位。隨著這些系統(tǒng)的進步,車輛中半導體元件的數(shù)量也隨之增加,以應對不斷增加的新功能。

面對車用半導體市場如此快速的增長, 瑞薩電子開發(fā)了許多車用產品,這其中包括微控制器(MCU),高度集成的片上系統(tǒng) (SoC) 處理器,存儲器以及電源管理系統(tǒng)(PMIC)。

然而,隨著行業(yè)的發(fā)展,問題仍然存在:“我們如何才能在整個行業(yè)中標準化這些元件的開發(fā)和設計,以便我們能夠應對風險并自信地聲稱該部件在功能上是安全的?”

因此,在 ISO 26262 的第一版中,汽車行業(yè)嘗試了開發(fā)的標準化,以便將如下所列出的大型系統(tǒng)元件開發(fā)時的風險降至最低:

因某些相關關系的遺漏,或不完整的分析所導致的系統(tǒng)性風險

設備故障所導致的隨機硬件失效。

在過去大約十年的時間里,汽車 OEM 一直依靠該標準的第 5 部分(part 5)

來幫助他們解決硬件故障,以實現(xiàn)業(yè)界公認的“安全”設計。瑞薩電子在產品開發(fā)中也采用了類似的標準,通過使用失效模式影響診斷分析 (FMEDA) 以及相關失效分析 (DFA) 對我們的產品進行分析,并提出解決設計中隨機硬件失效的策略。

在該標準第 5 部分的基礎上,為了應對汽車系統(tǒng)的復雜性,ISO 26262 擴大了其覆蓋范圍,包括進了專門針對半導體元件的第 11 部分(part 11)。

為了滿足提高功能安全的同時降低成本的這一新需求,除了我們的 R-Car 片上系統(tǒng)處理器之外,瑞薩還為汽車系統(tǒng)設計人員提供多軌、高功率的電源管理系統(tǒng) (PMIC)。這不僅能夠減少元件數(shù)量,還能夠提供系統(tǒng)開發(fā)所需的高性能。

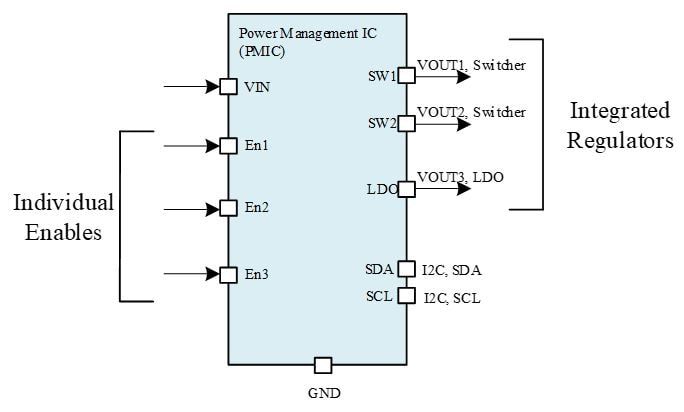

圖像

圖 1:具有 3 個輸出的基本 PMIC

為幫助汽車設計師了解在購買 PMIC 時需要注意哪些事項,我們將對功能安全設計時所需要的分析進行說明。為了解決在元件層面和系統(tǒng)層面上的相關失效及隨機硬件失效問題,瑞薩電子的所有電源產品均采用了類似的架構。這樣下次當您發(fā)現(xiàn)我們的 R-Car 套件搭載了瑞薩的 PMIC 時,您就會對自己的選擇充滿信心。

1. ISO 26262 分析方法(ISO 26262 Analysis Tools)

在通讀 ISO 26262 后,我們總結了該規(guī)格推薦的3種用于開發(fā)符合功能安全的產品的分析方法,具體如下:

框圖;

失效模式,影響及其診斷分析(FMEDA: Failure Modes Effects and Diagnostics Analysis);

相關失效分析 (DFA: Dependent Failure Analysis)。

這些方法之所以會被推薦,是因為它們能夠降低復雜性的同時完成功能安全的設計。瑞薩電子為了解決隨機硬件失效的問題,在設計每一款PMIC產品時都采用了這些分析方法。

1.1 框圖(The Block Diagram)

通讀 ISO 26262 的規(guī)格,可以明顯感覺到規(guī)格制定者重視的一件事:避免不必要的復雜性。并且,該規(guī)格給出了一套制作框圖的標準:

對設計進行抽象化,以確保每個區(qū)塊都有專門的功能,消除不必要的(往往會引起混亂的)混合功能。

使用概念安全分析(conceptual safety analysis )對運作流程簡化,并對具體功能的執(zhí)行位置進行最優(yōu)化。。

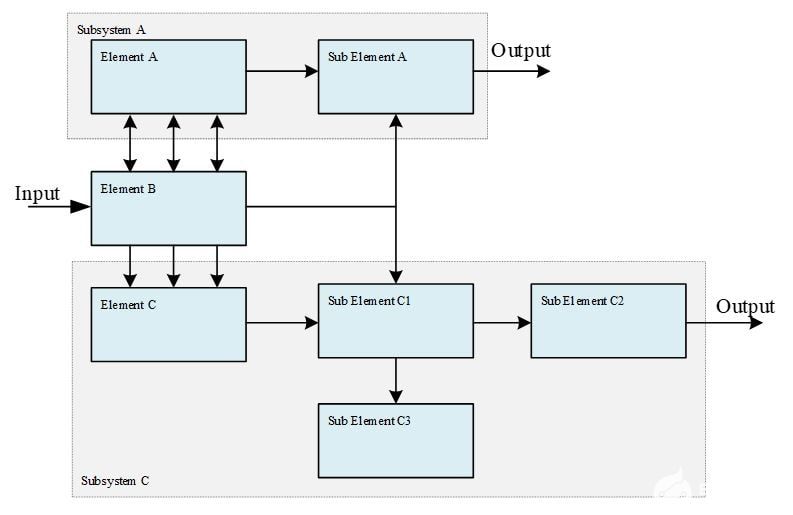

圖 2 顯示了此類框圖的一個簡單示例。

圖像

圖 2:系統(tǒng)框圖示例

1.2 失效分析方法 (Failure Analysis Tools)

在開始分析之前,我們需要確認規(guī)格希望我們在分析中使用的方法。這些方法可幫助我們確認安全機制和其保護對象的相關性(Dependent Failure)以及魯棒性設計(Robust Design)所允許的故障模式。

DFA:此分析方法有助于我們對相關失效進行識別。例如,當我們想要找出安全機制和其保護對象的元件之間相關失效時,可以使用此方法。

下面給出幾種利用該分析方法進行識別的常見案例:

VCC:為安全機制供電的電路發(fā)生漂移、噪聲或故障時,可能會對供電設備產生不利影響。

溫度:溫度的升高或降低可能會影響監(jiān)測精度的同時,降低其控制某些對象的能力。

DFA 通過識別并減輕相關關系(Dependencies)的方法,使這些影響得到減輕。

FMEDA:該分析方法在考慮了例如電阻串損壞和漂移等普遍被接受的故障模式的前提下,對功能所受的影響進行分析。同時還可用作失效性模擬器,對 ASIL 評級的安全范圍是否合理的進行確認。

DFA 需要識別各個功能之間的相關性,而 FMEDA則是一種更為直接的方法。FMEDA 的目標是調查功能的層次結構并將預想的故障模式應用于每個元素。此處涵蓋的故障最初在 ISO 26262 的第 5 部分中引入,然后在第二版的第 11 部分中進行了擴展。其中包括:

電阻器故障和元漂移

內存中的軟錯誤率,以及數(shù)字邏輯電路中的固定型故障

數(shù)據(jù)傳輸失敗

在概念設計階段,將這些故障應用于設計,創(chuàng)建機制來解決故障模式,然后分配覆蓋范圍。

2. 瑞薩 PMIC 架構介紹(Introducing Renesas PMIC Architecture)

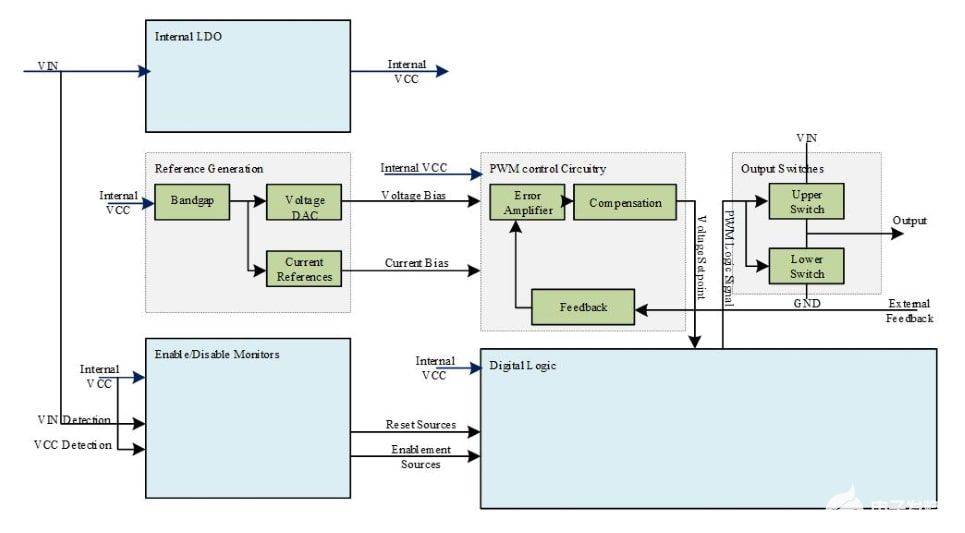

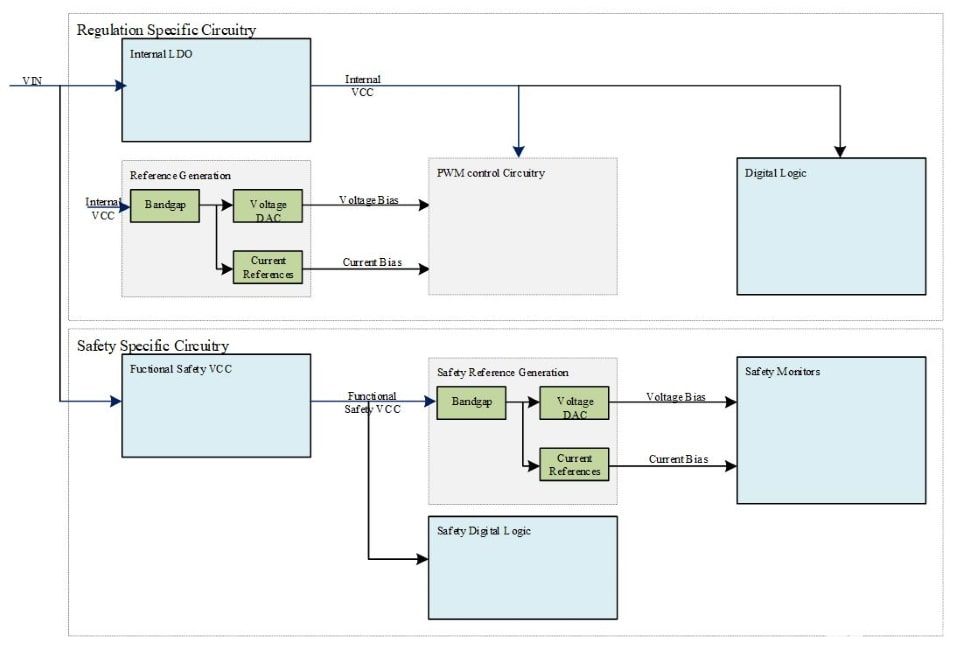

瑞薩電子基于這些分析的結果,定義了產品的主要元素。

基準電壓的生成:這通常包括分配帶隙和偏置電壓的電路。

內部電源的生成:為設備的內部元件提供電源的內部電源域。

開關:這包括提供輸入電壓切換的預驅動器和驅動器電路。

PWM 控制電路:這包括整個控制回路。

調節(jié)器使能:啟用或禁用調節(jié)器。

數(shù)字核心:控制上述要素的構成使其可用于不同的應用。

通常,這些系統(tǒng)就是PMIC(電源管理系統(tǒng))的基本構成要素,如圖 3 所示。

圖像

圖 3:基本監(jiān)管架構

結合 DFA 和 FMEDA,我們可以從概念上分析我們的架構,并考慮追加必要的功能和安全機制,以提高對硬件失效方面的魯棒性。雖然此分析并非詳盡,但它將為我們的數(shù)據(jù)資料提供一些背景信息。

2.1.1 內部軌和偏置生成(Internal Rail and Bias Generation)

瑞薩電子在設計產品時,首先會明確各個要素間的偏置關系。例如,為設備周圍的電路提供抽頭電壓的DAC。

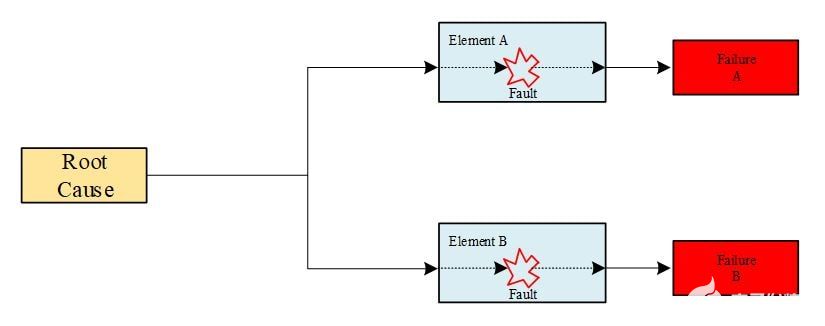

我們根據(jù)DFA 定義了故障模型并總結為以下內容。

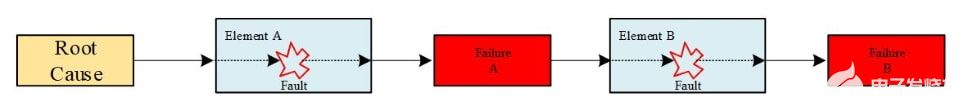

共因失效 (CCF: Common Cause Failure):單個故障導致兩個獨立元件各自發(fā)生故障。

圖像

圖 4:共因失效模型

級聯(lián)失效(Cascading Failure):一個元件出現(xiàn)的故障導致另一個元件出現(xiàn)故障。

圖像

圖 5:級聯(lián)失效模型

將這兩種失效模型與圖 3 結合來看,偏置和 VCC使用了同一個生成源,如果出現(xiàn)故障,將會影響電壓調節(jié)和監(jiān)測機制。

為了解決這個問題,原始架構被更改的更加獨立。

圖像

圖 6:改進的偏置結構,具有單獨的電力供給

圖 6 給出了處理這種相關關系時的一種方法,其中有單獨的偏置電路(帶隙)和電壓 DAC 來創(chuàng)建各自獨立的偏置點。這減少了電路之間的相關性,這也是為什么您會在我們的許多數(shù)據(jù)表中找到獨立的帶隙、帶隙監(jiān)測器和 VCC 監(jiān)測器的原因。安全要求越嚴格,解決方案就越復雜。

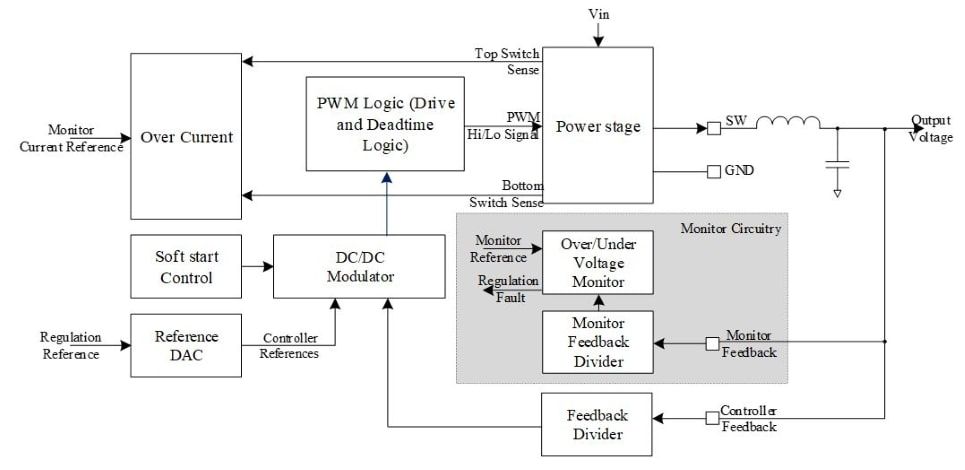

2.1.2 PWM 控制電路和輸出開關及驅動器(PWM Control Circuit & Output Switches and Drivers)

在設計反饋回路時,不同的架構決定了不同的性能以及必要的安全機構,因此反饋回路的設計對PMIC尤為重要。具體的失效模式分析示例如下:

由于被固定在高電平或低電平而導致輸出切換的故障:這將導致由于直通短路或將輸出直接連接到地或 VIN 而導致切換出現(xiàn)無規(guī)則性的問題。

為防止負載變化期間相對于設定值出現(xiàn)的過度變化的控制回路補償:這里的潛在故障是,控制器的帶寬急劇變化可能導致過壓或振蕩現(xiàn)象的發(fā)生。

由于許多故障會導致輸出電壓偏離其設定值或輸出電流超過設備或其負載的安全額定值,因此PMIC需要具有監(jiān)控輸出電流和輸出電壓的安全機制。這些安全機制通常由比較器或板載模數(shù) (A/D) 轉換器來實現(xiàn)。

接下來,我們將用 DFA 來分析反饋節(jié)點。在反饋路徑中,通常有一個電阻分壓器網絡將輸出電壓轉換為內部參考電平。若該電阻器出現(xiàn)故障,目標設定值會變得不正確,并且影響監(jiān)測機制的監(jiān)測能力。

因此我們得出了以下標準:

設備需要設置兩個獨立的反饋源,以解決反饋節(jié)點與板上另一個引腳或另一個電壓短路的相關故障。

這種獨立的反饋源需要一個冗余電阻分壓器來解決電阻反饋網絡任何部分的短路故障模式。

出于這個原因,您經常會在我們的產品中看到除了反饋引腳之外還有另一個用于監(jiān)控的引腳。如果是內置反饋電阻,則大多情況下會為了冗余性而設立其他不同的路徑。

圖像

圖 7:基本 DC/DC 調制器

對于最后的兩節(jié)中,我們的焦點將由控制回路轉向監(jiān)測機制。

2.1.3 監(jiān)視器和控制(Monitors and Controls)

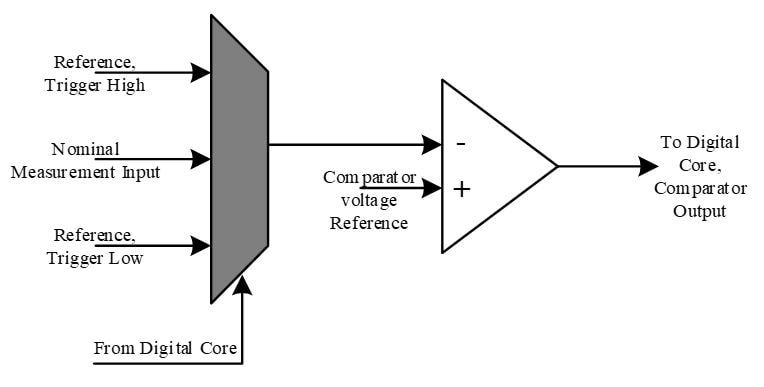

監(jiān)視器和使能控制可以說是設備中最重要的電路之一,因為它們對于確保系統(tǒng)功能安全的安全機制的實施至關重要。它們由以下一系列比較器電路組成:

過流監(jiān)測。

上電復位監(jiān)測。

輸出電壓(過壓和欠壓)監(jiān)測。

內部時鐘監(jiān)測。

在進行 FMEDA分析 時,我們假設比較器輸出出現(xiàn)了固定型故障(固定在高位和低位)。在這兩個故障中,固定在低位的影響更大,因為在正常操作中會漏掉發(fā)生的故障,成為潛在故障。為了提高設備檢測出這些低位固定型故障的能力,瑞薩 PMIC 設置了自檢功能 (ABIST)。

該過程由圖8所示:

圖像

圖 8:比較器 BIST 架構示例

數(shù)字控制器將輸入切換至比較器以生成強制觸發(fā),正常運作得到確定后,輸入控制再次變?yōu)檎DJ健?/p>

2.1.4 數(shù)字內核(Digital Core)

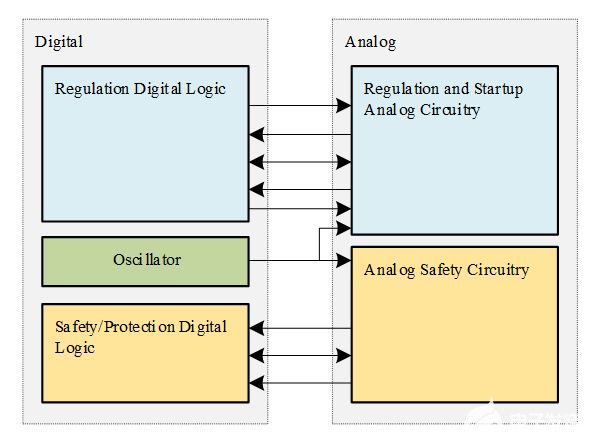

如圖 9 所示,數(shù)字內核位于模擬部分附近,并且通常分為負責功能安全相關控制的部分和負責穩(wěn)壓器啟動和控制的部分。

這種架構通常更適合用于減少 DFA 分析所發(fā)現(xiàn)的相關關系。為了更好地理解數(shù)字內核的結構,請參見圖 9,其中主要功能包括:

功能安全相關控制,通常由狀態(tài)機實現(xiàn)。

圖像

圖 9:模擬和數(shù)字分區(qū)

在這里,針對一次性可編程 (OTP) 熔絲陣列和配置寄存器進行數(shù)據(jù)損壞(Bit Corruption)相關的FMEDA分析后,能夠預想到在啟動或者運行時將會出現(xiàn)芯片配置錯誤的故障。為了防止出現(xiàn)此問題,在啟動時和設備配置中定期執(zhí)行循環(huán)冗余計算 (CRC)。并且將此方法擴展到通信接口。

實現(xiàn)數(shù)字部分的安全機制的方法還有很多,除了 CRC 之外,還有以下列出的安全機制:

必要的冗余邏輯;

時鐘監(jiān)測;

邏輯 BIST (LBIST),與 ABIST 一樣,檢查數(shù)字邏輯是否存在固定型故障。

3. 結論

每個新產品的開發(fā),都會由設計團隊和安全團隊對功能安全機制進行探討研究,然后由營銷團隊將這些新產品的特點進行推廣和普及。本文中介紹的概念性分析旨在為讀者提供一些捷徑,以便于了解瑞薩電子是如何設計 ASIL 級電源管理產品,以及為何我們會在硬件數(shù)據(jù)表中列出各種“安全”相關功能的原因。

審核編輯:郭婷

-

電源

+關注

關注

185文章

17870瀏覽量

252157 -

寄存器

+關注

關注

31文章

5377瀏覽量

121374 -

比較器

+關注

關注

14文章

1660瀏覽量

107501

發(fā)布評論請先 登錄

相關推薦

鴻蒙北向開發(fā)OpenHarmony4.1 DevEco Studio開發(fā)工具安裝與配置

盤點工程師常用的嵌入式開發(fā)工具

最新Simplicity SDK軟件開發(fā)工具包發(fā)布

2024年十款熱門云端開發(fā)工具推薦

雙麒麟系統(tǒng)!迅為RK3588開發(fā)板+銀河麒麟/開放麒麟

字節(jié)跳動發(fā)布豆包MarsCo智能開發(fā)工具

Java語言、idea開發(fā)工具、MYSQL數(shù)據(jù)庫開發(fā)的UWB定位技術系統(tǒng)源碼

用于為ADAS應用開發(fā)的電源系統(tǒng)的功能安全開發(fā)工具和方法

用于為ADAS應用開發(fā)的電源系統(tǒng)的功能安全開發(fā)工具和方法

評論