1. 毛刺的產(chǎn)生原因:冒險(xiǎn)和競爭

使用分立元件設(shè)計(jì)電路時(shí),由于PCB在走線時(shí),存在分布電容和電容,所以在幾ns內(nèi)毛刺被自然濾除,而在PLD內(nèi)部沒有分布電感和電容,所以在PLD/FPGA設(shè)計(jì)中,競爭和冒險(xiǎn)問題比較重要。

信號(hào)在FPGA器件內(nèi)部通過連線和邏輯單元時(shí),都有一定的延時(shí)。延時(shí)的大小與連線的長短和邏輯單元的數(shù)目有關(guān),同時(shí)還受器件的制造工藝、工作電壓、溫度等條件的影響。信號(hào)的高低電平轉(zhuǎn)換也需要一定的過渡時(shí)間。由于存在這兩方面因素,多路信號(hào)的電平值發(fā)生變化時(shí),在信號(hào)變化的瞬間,組合邏輯的輸出有先后順序,并不是同時(shí)變化,往往會(huì)出現(xiàn)一些不正確的尖峰信號(hào),這些尖峰信號(hào)稱為"毛刺"。如果一個(gè)組合邏輯電路中有"毛刺"出現(xiàn),就說明該電路存在"冒險(xiǎn)"。

可以概括的講,只要輸入信號(hào)同時(shí)變化,(經(jīng)過內(nèi)部走線)組合邏輯必將產(chǎn)生毛刺。將它們的輸出直接連接到時(shí)鐘輸入端、清零或置位端口的設(shè)計(jì)方法是錯(cuò)誤的,這可能會(huì)導(dǎo)致嚴(yán)重的后果。所以我們必須檢查設(shè)計(jì)中所有時(shí)鐘、清零和置位等對(duì)毛刺敏感的輸入端口,確保輸入不會(huì)含有任何毛刺。

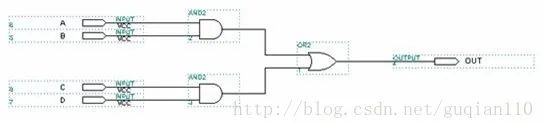

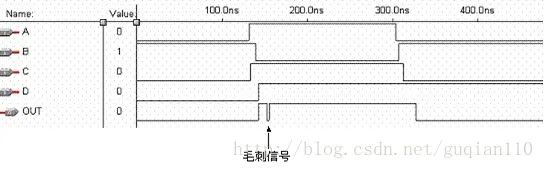

存在邏輯冒險(xiǎn)的電路:

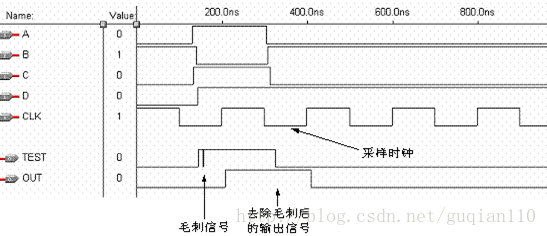

仿真波形:

2. 判斷是否存在冒險(xiǎn)

關(guān)于冒險(xiǎn)的知識(shí),數(shù)電書上有詳細(xì)的說明,當(dāng)時(shí)沒有認(rèn)真學(xué),只了解個(gè)大概,現(xiàn)在又要重新看...還記得當(dāng)年畫卡諾圖時(shí)的痛苦

冒險(xiǎn)按照產(chǎn)生方式分為靜態(tài)冒險(xiǎn)&動(dòng)態(tài)冒險(xiǎn)兩大類。靜態(tài)冒險(xiǎn)指輸入有變化,而輸出不應(yīng)該變化時(shí)產(chǎn)生的窄脈沖;動(dòng)態(tài)冒險(xiǎn)指輸入變化時(shí),輸出也應(yīng)該變化時(shí)產(chǎn)生的冒險(xiǎn)。動(dòng)態(tài)冒險(xiǎn)是由靜態(tài)冒險(xiǎn)引起的,所以,存在動(dòng)態(tài)冒險(xiǎn)的電路也存在靜態(tài)冒險(xiǎn)。

靜態(tài)冒險(xiǎn)根據(jù)產(chǎn)生條件不同,分為功能冒險(xiǎn)和邏輯冒險(xiǎn)兩種。當(dāng)有兩個(gè)或兩個(gè)以上的輸入信號(hào)同時(shí)變化時(shí),在輸出端有毛刺,稱為功能冒險(xiǎn);如果只有一個(gè)輸入變量變化時(shí),出現(xiàn)的冒險(xiǎn)稱為邏輯冒險(xiǎn)。

因?yàn)閯?dòng)態(tài)冒險(xiǎn)是由靜態(tài)冒險(xiǎn)引起的,所以消除了靜態(tài)冒險(xiǎn),也就消除了動(dòng)態(tài)冒險(xiǎn)。功能冒險(xiǎn)是由電路的邏輯功能產(chǎn)生的,只要輸入信號(hào)不是按照循環(huán)碼的方式變化,就會(huì)產(chǎn)生功能冒險(xiǎn),而且不能通過修改設(shè)計(jì)來消除,只能通過對(duì)輸出進(jìn)行采樣來消除。判斷邏輯冒險(xiǎn)的步驟:

判斷信號(hào)是否會(huì)同時(shí)變化

判斷信號(hào)同時(shí)變化時(shí),是否會(huì)發(fā)生冒險(xiǎn)(代數(shù)法 or 卡諾圖

3. 消除毛刺

我們可以通過改變?cè)O(shè)計(jì),破壞毛刺產(chǎn)生的條件,來減少毛刺的發(fā)生。例如,在數(shù)字電路設(shè)計(jì)中,常常采用格雷碼計(jì)數(shù)器取代普通的二進(jìn)制計(jì)數(shù)器,這是因?yàn)楦窭状a計(jì)數(shù)器的輸出每次只有一位跳變,消除了競爭冒險(xiǎn)的發(fā)生條件,避免了毛刺的產(chǎn)生。

毛刺并不是對(duì)所有的輸入都有危害,例如D觸發(fā)器的D輸入端,只要毛刺不出現(xiàn)在時(shí)鐘的上升沿并且滿足數(shù)據(jù)的建立和保持時(shí)間,就不會(huì)對(duì)系統(tǒng)造成危害,我們可以說D觸發(fā)器的D輸入端對(duì)毛刺不敏感。根據(jù)這個(gè)特性,我們應(yīng)當(dāng)在系統(tǒng)中盡可能采用同步電路,這是因?yàn)橥诫娐沸盘?hào)的變化都發(fā)生在時(shí)鐘沿,只要毛刺不出現(xiàn)在時(shí)鐘的沿口并且不滿足數(shù)據(jù)的建立和保持時(shí)間,就不會(huì)對(duì)系統(tǒng)造成危害。(由于毛刺很短,多為幾納秒,基本上都不可能滿足數(shù)據(jù)的建立和保持時(shí)間)

以上方法可以大大減少毛刺,但它并不能完全消除毛刺,有時(shí),我們必須手工修改電路來去除毛刺。一般有兩種方法:

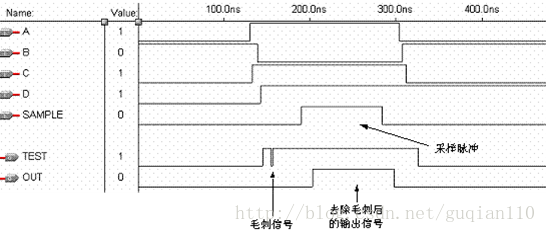

脈沖選擇法

一般說來,冒險(xiǎn)出現(xiàn)在信號(hào)發(fā)生電平轉(zhuǎn)換的時(shí)刻,也就是說在輸出信號(hào)的建立時(shí)間內(nèi)會(huì)發(fā)生冒險(xiǎn),而在輸出信號(hào)的保持時(shí)間內(nèi)是不會(huì)有毛刺信號(hào)出現(xiàn)的。如果在輸出信號(hào)的保持時(shí)間內(nèi)對(duì)其進(jìn)行"采樣",就可以消除毛刺信號(hào)的影響。缺點(diǎn)是必須人為的保證sample信號(hào)必須在合適的時(shí)間中產(chǎn)生

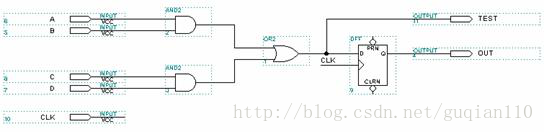

時(shí)序邏輯保持法

利用D觸發(fā)器的D輸入端對(duì)毛刺信號(hào)不敏感的特點(diǎn),在輸出信號(hào)的保持時(shí)間內(nèi),用觸發(fā)器讀取組合邏輯的輸出信號(hào),這種方法類似于將異步電路轉(zhuǎn)化為同步電路。

4. 具體信號(hào)的討論

1. 置位/復(fù)位信號(hào)

清除和置位信號(hào)要求象對(duì)待時(shí)鐘那樣小心地考慮它們,因?yàn)檫@些信號(hào)對(duì)毛刺也是非常敏感的。正如使用時(shí)鐘那樣,最好的清除和置位是從器件的引腳單直接地驅(qū)動(dòng)。有一個(gè)主復(fù)位Reset引腳是常用的最好方法,主復(fù)位引腳給設(shè)計(jì)項(xiàng)目中每個(gè)觸發(fā)器饋送清除或置位信號(hào)。幾乎所有PLD器件都有專門的全局清零腳和全局置位。如果必須從器件內(nèi)產(chǎn)生清除或置位信號(hào),則要按照“門控時(shí)鐘”的設(shè)計(jì)原則去建立這些信號(hào),確保輸入無毛刺。

2. 組合邏輯輸出

當(dāng)PLD輸出引腳給出系統(tǒng)內(nèi)其它部分的邊沿敏感信號(hào)或電平敏感信號(hào)時(shí),這些出信號(hào)必須象內(nèi)部時(shí)鐘、清除和置位信號(hào)一樣小心地對(duì)待。只要可能就應(yīng)在PLD輸出端寄存那些對(duì)險(xiǎn)象敏感的組合輸出。如果你不能寄存險(xiǎn)象敏感的輸出,則應(yīng)符合“門控時(shí)鐘”中討論的門控時(shí)鐘的條件。決不能用多級(jí)邏輯驅(qū)動(dòng)毛刺敏感的輸出。

3. 異步輸入信號(hào)

按照定義,異步輸入不是總能滿足(它們所饋送的觸發(fā)器的)建立和保持時(shí)間的要求。因此,異步輸入常常會(huì)把錯(cuò)誤的數(shù)據(jù)鎖存到觸發(fā)器,或者使觸發(fā)器進(jìn)入亞穩(wěn)定的狀態(tài),在該狀態(tài)下,觸發(fā)器的輸出不能識(shí)別為l或0。如果沒有正確地處理,亞穩(wěn)性會(huì)導(dǎo)致嚴(yán)重的系統(tǒng)可靠性問題。采用附加觸發(fā)器同步使能信號(hào)的方法可保證不違反計(jì)數(shù)器的建立時(shí)間,從而解決可靠性的問題。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618791 -

PLD

+關(guān)注

關(guān)注

6文章

230瀏覽量

60220 -

毛刺

+關(guān)注

關(guān)注

0文章

29瀏覽量

15868

原文標(biāo)題:FPGA學(xué)習(xí)-關(guān)于毛刺

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

鋁鑄件去毛刺加工,用SycoTec浮動(dòng)去毛刺主軸

毛刺的產(chǎn)生原因:冒險(xiǎn)和競爭

毛刺的產(chǎn)生原因:冒險(xiǎn)和競爭

評(píng)論