針對大帶寬采樣需求,設計了基于AD9208的高速采集電路,通過分析時鐘抖動,噪聲等因素對采集電路的影響,設計了相關電路,包括低抖動時鐘電路、模擬信號輸入電路、電源電路,并測試了在不同輸入頻率下,AD9208的無雜散動態范圍。

引言

數字接收機在合成孔徑雷達、無線電通信、以及儀器儀表等場合中占有重要地位。隨著電子產業的發展,數字接收機對采樣率、模擬信號輸入帶寬以及分辨率等要求越來越高,因此對模數轉換電路的設計要求更加嚴格。目前高速采樣系統設計達到Gsps以上,除模數轉換器(ADC)本身性能指標要求外,在外圍電路設計以及印刷電器板(PCB)布線上都有很高的要求,相關芯片大部分由國外制造,國內正處于發展期,相關技術需求越來越高,因此對高帶寬、高分辨率的模數轉換電路研究具有重要的意義。

本文選用ADI公司生產的3Gsps、14BitADC芯片AD9208,分析其性能參數以及相關影響因素,進行了采集電路設計,重點分析設計了時鐘電路、模擬信號輸入電和電源電路,保證時鐘、模擬信號輸入通道和電源滿足設計要求。

1采樣電路影響因素分析

信噪比是采樣電路最關鍵的性能指標,式(1)表示了信噪比與量化噪聲,熱噪聲和時鐘抖動的關系:

式中:tJ-Clock-Input來源于時鐘電路;tJ-Analog-Input來源于模擬信號輸入電路。

通過查詢AD9208技術手冊,tJ-Analog-Input=55fs,tJ-Clock-Input=0,fA =3GHz,將其代入式(4)可得到在3GHz理想模擬信號輸入條件下,理想的采樣電路信噪比σS/Nidea-adc=59.68dB。在采樣電路設計中,為提高信噪比性能,應盡可能減少時鐘抖動tJ-Clock-Input和模擬信號輸入抖動tJ-Analog-Input。

2采集電路分析與設計

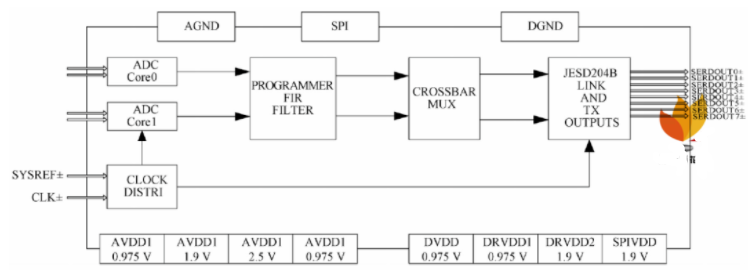

采集電路設計以AD9208為核心,其結構如圖1所示,外部接口主要包括模擬信號輸入,采樣時鐘輸入,電源,以及SERDES傳輸所需要的時鐘和傳輸通道。

圖1AD9208結構示意圖

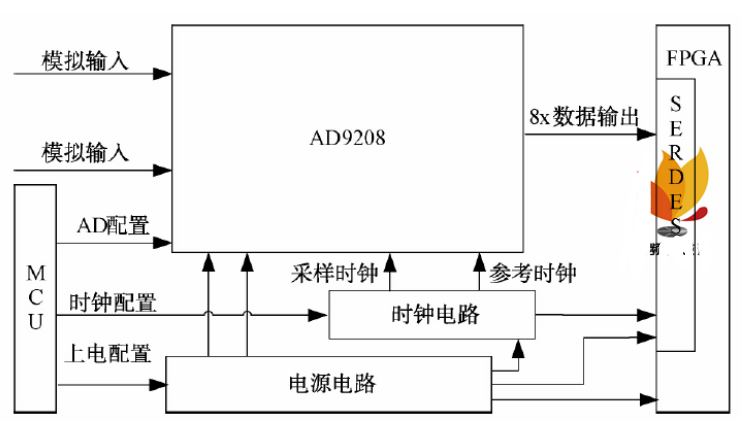

根據AD9208具體設計要求,設計的采集電路主要包括前端模擬輸入電路、時鐘電路、供電電路、數據接收電路和管理配置電路等,如圖2所示。據第1節所述,時鐘電路和模擬信號輸入電路至關重要,同時電源供電是保證電路工作的重要因素,本節將進行詳細分析和設計。

圖2采集電路原理示意圖

2.1時鐘電路分析與設計

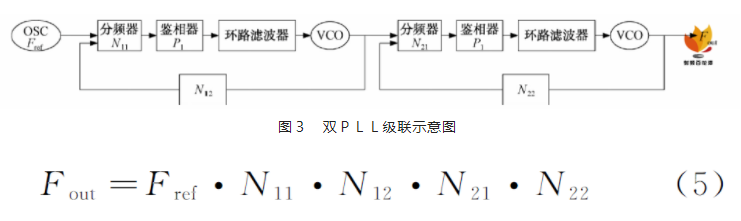

高速ADC需要1個低抖動的高頻采樣時鐘,通常由時鐘源和鎖相環(PLL)電路產生,除選擇良好的時鐘源,PLL電路的設計至關重要,高速ADC需要的采樣時鐘帶寬較高,因此可采用2級PLL結構,第1級PLL環路濾波器帶寬較窄,濾除鑒相器輸出的諧波分量,為PLL2提供了1個高精度、低相噪的參考時鐘,以期PLL2為高速ADC提供大帶寬、低抖動的采樣時鐘。PLL級聯方式如圖3所示.式(5)表示了輸出頻率Fout和時鐘源頻率Fref的關系:

任何時鐘電路均會產生時鐘抖動,時鐘電路總抖動tJ-Clock-Input包括時鐘源、PLL電路、分頻電路等各種級聯電路抖動的均方根。AD9028在3G理性模擬信號下信噪比σS/Nidea-adc =59.68dB,為保證設計要求,最終信噪比應在53dB以上,將σS/N = 53dB,tJ-Analog-Input=55fs,fA =3GHz,tJ-Analog-Input=0,代入式(3)和式(4)可計算出tJ-Clock-Input=95fs。因此在時鐘電路設計時應選擇時鐘抖動在95fs以下的器件。

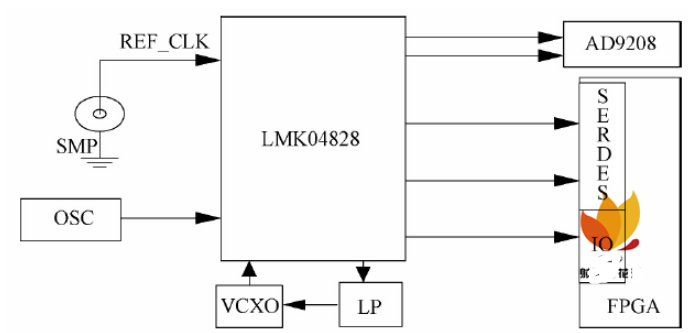

本設計中,為簡化電路,選擇Ti 公司的LMK04828,時鐘抖動為90fs,滿足時鐘抖動要求。支持雙PLL級聯工作模式,且N11、N12、N21、N22可自動配置,鎖定后時可以同時輸出多路時鐘,滿足ADC采樣、數據發送和FPGA 數據接收的時鐘要求,保證時鐘同步。圖4為設計的時鐘電路原理框圖。

圖4時鐘電路原理框圖

2.2模擬信號輸入電路分析與設計

目前,用來驅動ADC 的方案主要有變壓器和差分放大器2種。第一,變壓器是無源器件,不需要消耗功率,且一般認為它引入的噪聲是可忽略的。第二,差分放大器是有源器件,需要消耗能量,具有一定的諧波失真和較寬頻帶內的白噪聲,會降低ADC的信噪比和有效分辨率。

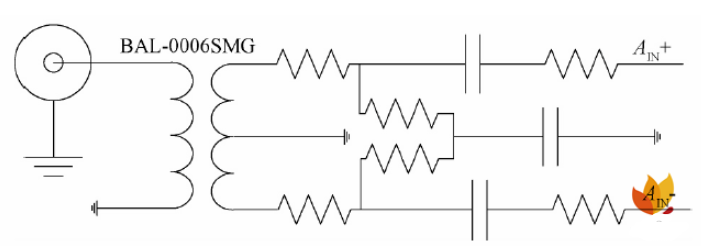

本次設計模擬信號從同軸電纜接插件中輸入為單端信號,AD9208模擬輸入通道為差分形式,雖然放大器也能實現該功能,但變壓器為無源器件,并且具有電流隔離功能,帶寬更寬,功耗低,且不引入噪聲,對SNR沒有影響。為滿足AD9208信號輸入帶寬,選用型號為BAL-0006SMG的BALUN 射頻變壓器,阻抗50Ω。

在將模擬信號轉換為差分信號后,需要進行阻抗匹配,根據AD9208輸入阻抗要求,設計的模擬信號輸入電路原理框圖如圖5所示。

圖5模擬信號調理框圖

2.3電源電路設計

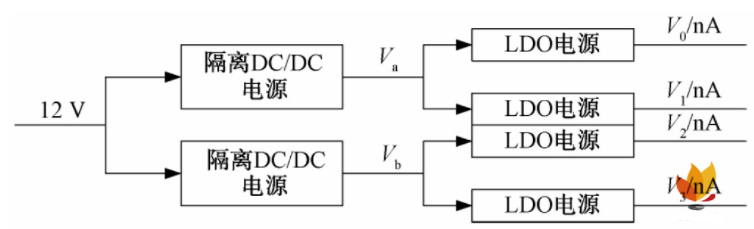

高速ADC電路設計中,要確保電源來源及目的端的電壓及電流滿足需求。一般會涉及多種電源,分布式電源架構往往更適合高速電路設計,即采用2級電源轉換,第1級電源的目的是獲得中間電源,同時為單板提供電源隔離保護,允許輸出較大的紋波和噪聲,第2級電源的目的是輸出器件所需要的電源,重點是限制輸出端的噪聲和紋波。如圖6所示。

圖6分布式電源框圖

通用的電源包括開關型DC-DC和低壓差線性穩壓器(LDO),開關型DC-DC效率高,能實現隔離保護,LDO電源相對于DC-DC電源紋波小、穩定性高,但輸出電流較小。顯然在分布式電源架構中,第1級適合采用開關型DC-DC,以提供隔離保護和更高的轉換效率,第2級電源采用LDO電源,以提供精確的電壓和紋波抑制。在設計時,LDO電源電路為器件直接供電,應注意輸出電壓精度、壓降、延時、散熱、紋波抑制(PSRR)等。以TPS7A91為例,該器件在負載和溫度范圍內精度達1%,LDO功耗為輸出電流與壓降的乘積,在滿足目的器件所需電壓的情況下,應盡可能減少壓降,其中包括合理降低輸入電壓,增加散熱以降低電源溫度,從而減少電源功耗,獲取更高效率。式(6)表示了壓降與額定電流的關系:

顯然降低壓降可以減少功耗,抑制紋波。因此在LDO電源設計時,在滿足輸出電壓的要求下,應盡可能減少輸入電壓。

目前器件集成度越來越高,內部晶體管數量越來越大,受器件電源管腳數目限制,外部電源需給內部電路提供公共的供電節點,此時器件供電處的噪聲會通過內部電路傳播,影響器件內部工作穩定包括晶振、PLL、延時鎖相環(DLL)的抖動特性,AD轉換電路的轉換精度,嚴重時甚至引起邏輯錯誤。器件供電引腳處的噪聲主要來源于電源本身輸出紋波,器件因邏輯轉換產生的瞬態電流,電源無法實時響應目的器件對電流需求的快速變化,信號通過過孔換層引起的電源噪聲。其中包括選用低紋波電源器件,在目的器件管腳處放置旁路電容作為電荷緩沖池以滿足器件對電流需求的快速變化,濾波以消除噪聲。

降低輸出噪聲VOUT(f),需提高電源的紋波抑制和降低輸入噪聲。除選用高紋波抑制電源器件,還需要在電源參考電壓處增加合適的前饋電容。綜上,電容在電源電路中占有十分重要的地位。

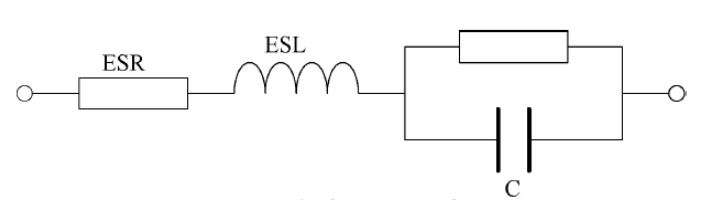

電容的本質是儲存電荷和釋放電荷,因此作為電荷緩沖池容易滿足器件工作電壓不隨電流和功耗的劇烈變化而變化。同時電容阻抗Z =1/(jωC),頻率不同,電容阻抗不同。高速設計中,電源噪聲往往占據不同的頻帶,且電容并不是純粹電容,同時包含電容分量和電阻分量,如圖7所示。

圖7電容分量示意圖

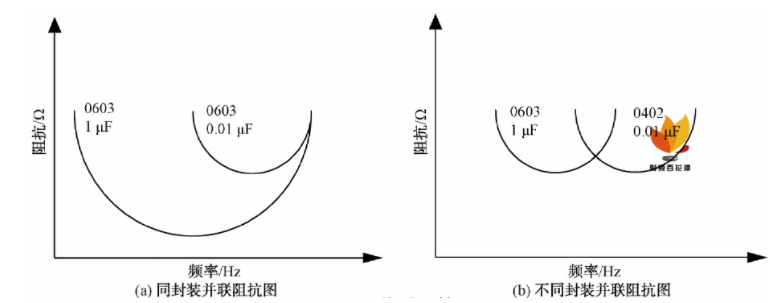

因此在選取不同電容增強濾波特性時,不僅考慮電容值,還應考慮封裝和材料不同影響的其他特性。以某廠家提供的0603封裝1μF,0603封裝0.01μF,0402封裝0.01μF阻抗曲線來分析,如圖8所示,顯然只選用0603封裝1μF和0603封裝0.01μF并未拓寬低阻抗頻帶,選用0603封裝1μF和0402封裝0.01μF可以拓寬低阻抗頻帶,并聯放置相同電容可以獲得更低阻抗。

圖8并聯阻抗圖

3驗證

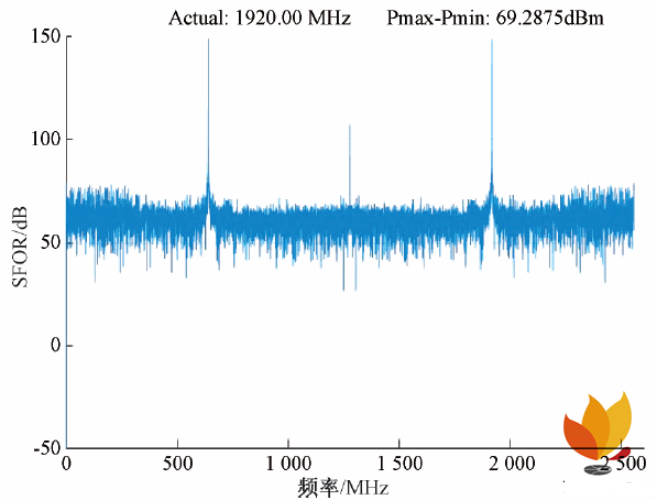

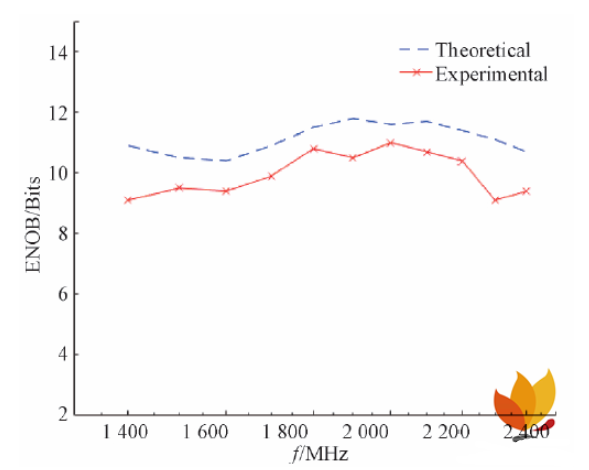

在完成板卡基礎調試后,利用信號源產生步進100MHz的模擬信號,并將采集數據進行快速傅里葉變換(FFT),圖9為1920MHz模擬信號輸入下,計算得到的無雜散動態范圍,圖10將各頻點得到的數據根據式(2)轉換為有效位數曲線,可以驗證電路采樣位數在9.6~12 位,發揮了AD9208性能,滿足設計要求,為后續數據處理提供了良好的平臺。

圖9FFT數據圖

圖10ENOB對照圖

4結束語

本文通過分析ADC信噪比性能影響因素,明確時鐘抖動、信號輸入對提高ADC性能有著重要的影響,詳細分析和設計了時鐘電路、模擬信號輸入電路和電源電路。最后通過輸入各頻點模擬信號測試,對比AD9208手冊提供的數據,驗證了采集電路性能,為后續數據處理打下了基礎。

作者:王德恒,劉文政

來源:艦船電子對抗

-

模擬信號

+關注

關注

8文章

1160瀏覽量

53360

發布評論請先 登錄

請問AD9280做ad轉換非線性很大是正常的嗎?

兩片AD9280能否數據線接在一起靠三態引腳區分讀數

高速模數轉換器MS9280參數和兼容AD9280

高速ADC,MS9280替代AD9280,P=P直接替代

關于AD9280非線性的問題求解

AD9280三態引腳是否只是控制數據輸出端的,和轉換過程沒有關系?

數模模數轉換芯片AD9280

AD9280完整的8位32MSPS,95毫瓦cmos模數轉換器

AD9280 完整8位、32 MSPS AD

基于AD9280的高速采集電路設計方案

基于AD9280的高速采集電路設計方案

評論