將多個數(shù)字信號處理 (DSP) 模塊、寬帶數(shù)模轉(zhuǎn)換器 (DAC) 和寬帶模數(shù)轉(zhuǎn)換器 (ADC) 集成在單個單片芯片中,現(xiàn)在可以將耗電的 FPGA 資源卸載到允許更小尺寸、更低功耗、增加通道數(shù)的平臺,能夠以比以前更高的速率進行采樣。除了這項新功能之外,這些集成電路 (IC) 中還配備了新穎的多芯片同步 (MCS) 算法,允許用戶在為系統(tǒng)供電或以其他方式對系統(tǒng)進行軟件修改時為所有通道實現(xiàn)已知(確定性)相位。因此,這個確定性階段簡化了更廣泛的系統(tǒng)級校準(zhǔn)算法,這些算法需要在連接到這些 IC 的前端網(wǎng)絡(luò)的輸出或輸入處實現(xiàn)所有通道的同步。本文介紹了在使用由多個數(shù)字化儀 IC、時鐘源和數(shù)字接口組成的 16 通道接收器/發(fā)送器平臺時展示這種 MCS 能力的實驗結(jié)果。

高級系統(tǒng)框圖

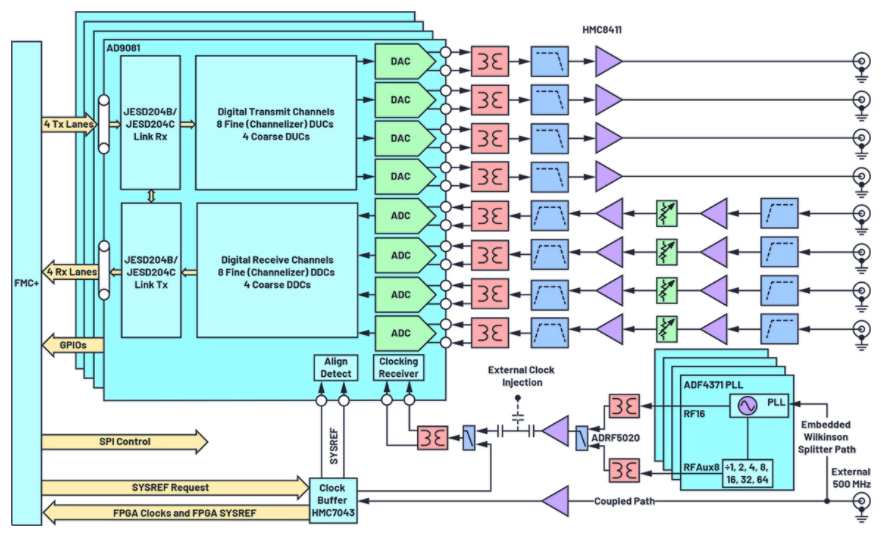

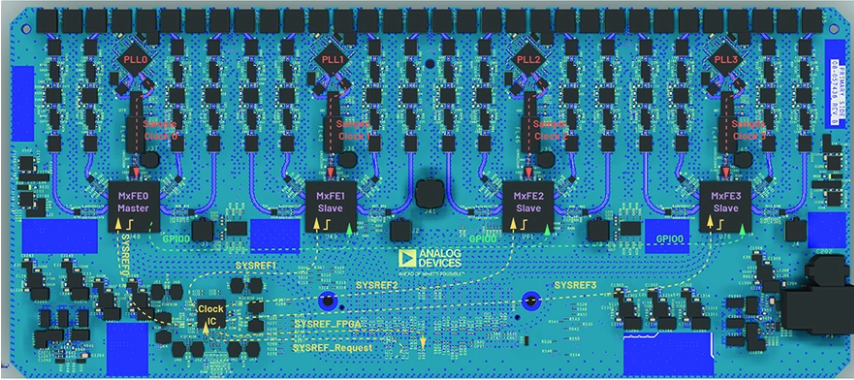

用于該測試的系統(tǒng)框圖如圖 1 所示,由四個集成 DAC/ADC/DSP IC 組成,每個 IC 由四個 12 GSPS DAC、四個 4 GSPS ADC、12 個數(shù)字上變頻器 (DUC) 和 12 個數(shù)字下變頻器 (DDC) 塊。

圖 1. 用于演示 MCS 和多通道校準(zhǔn)算法的系統(tǒng)高級框圖。(來源:ADI)

DUC/DDC 允許在數(shù)字域內(nèi)進行頻率轉(zhuǎn)換和/或插值/抽取。使用注入板上的單個 500 MHz 參考時鐘,然后使用參考鎖定時鐘緩沖器來生成 MCS 所需的系統(tǒng)參考信號以及與基帶處理器 (BBP) 的數(shù)字接口所需的時鐘。該系統(tǒng)還包含四個獨立的鎖相環(huán) (PLL) 合成器,這些合成器生成所需的 12 GHz 信號源,以從公共參考為每個數(shù)字化 IC 提供時鐘。一個射頻前端連接到每個數(shù)字化儀輸出/輸入,它創(chuàng)建一個經(jīng)過濾波和放大的信號到/來自邊緣發(fā)射的射頻連接器。實現(xiàn)了完整的配電解決方案。系統(tǒng)所需的所有電壓均由單個 12 V 電源產(chǎn)生。

子陣列時鐘樹結(jié)構(gòu)

如前所述,子陣列時鐘樹由單個 500 MHz 參考源組成,該參考源被拆分并發(fā)送到四個獨立 PLL 合成器 IC 的參考輸入,如上圖 1 所示。這個 500 MHz 信號也是 10 dB 耦合、放大的,并發(fā)送到另一個時鐘緩沖器 IC,該 IC 負(fù)責(zé)生成數(shù)字接口所需的系統(tǒng)參考 (SYSREF) 和 BBP 時鐘。這個時鐘樹的目標(biāo)是三重的,因為它:

允許單個通道 SYSREF 延遲以糾正 IC 之間的任何走線長度不匹配。

允許單獨的 PLL/合成器相位調(diào)整,因此確保各個數(shù)字化儀 IC 時鐘源之間的同步,以補償系統(tǒng)內(nèi)任何感應(yīng)的熱梯度。

使用戶能夠?qū)崿F(xiàn)數(shù)字化 IC 的必要設(shè)置和保持要求。

選擇時鐘樹 IC 是為了證明可以借助這些芯片中存在的數(shù)字和模擬延遲塊在軟件和/或硬件中糾正各種電路板布局異常。最終結(jié)果是一個時鐘樹,它可以在每個 IC 的相同采樣時鐘周期內(nèi)向所有需要的 IC 提供 SYSREF 脈沖。

帶基帶處理器的數(shù)字接口

四個數(shù)字化 IC 各建立一個與 BBP 的 JESD204B 或 JESD204C 數(shù)字鏈路接口。1,2該接口負(fù)責(zé)通過物理走線 (SERDES) 將 ADC 和 DAC 代碼傳輸?shù)?BBP 和從 BBP 傳輸。此接口中使用的差分 SERDES 跡線數(shù)稱為此鏈路的通道數(shù) (L)。通過鏈路發(fā)送的轉(zhuǎn)換器位分辨率被視為N‘。通道化數(shù)據(jù)路徑(也稱為虛擬轉(zhuǎn)換器)的數(shù)量標(biāo)記為 M。本文中顯示的結(jié)果使用 JESD204C 鏈路,其中 M = 16,N’ = 16,L = 4 用于 DAC 側(cè)鏈路,M = 8 , N‘ = 16, L = 2 用于 ADC 側(cè)鏈路。

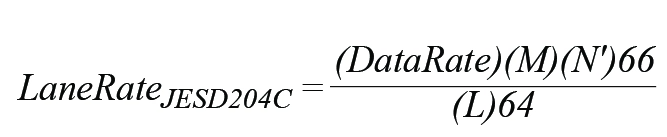

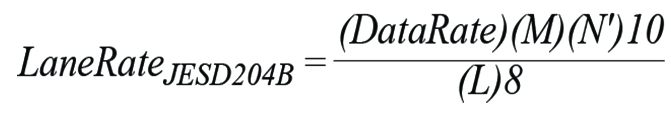

數(shù)字化儀 IC 和 BBP 之間傳輸和接收數(shù)據(jù)的速率稱為通道速率。硅片上的 DSP 模塊(即 DDC/DUC)允許用戶以與通過物理通道發(fā)送的數(shù)據(jù)速率不同的速率對數(shù)字化儀進行采樣。因此,通道速率取決于每個數(shù)據(jù)路徑的數(shù)字抽取/內(nèi)插數(shù)據(jù)速率。對于這項工作,使用了 250 MSPS I/Q 數(shù)據(jù)速率。對于 JESD204C 接口,通道速率定義為:

而對于 JESD204B 接口,通道速率定義為:

本文中顯示的結(jié)果對 ADC 端和 DAC 端 JESD204C 鏈路均使用 16.5 Gbps 的通道速率。

每個 JESD204B/JESD204C 鏈路都可以在不同的子類中建立。這些子類根據(jù)是否需要多芯片同步或確定性延遲進行分離。對于這項工作,顯示的數(shù)據(jù)使用 JESD204C 子類 1 模式,因此利用 SYSREF 信號來對齊通過系統(tǒng)內(nèi)存在的多個鏈路傳輸?shù)牟糠謹(jǐn)?shù)字?jǐn)?shù)據(jù)。具體來說,在此 JESD204C 子類 1 模式中,SYSREF 信號用于對齊本地擴展多塊計數(shù)器 (LEMC),其傳輸速率為:

其中 F 是每個通道每個 JESD 幀的八位字節(jié)數(shù),K 是每個單個多幀的幀數(shù)。對于這項工作,F(xiàn) = 8 和 K = 32,因此使用 7.8125 MSPS 的 LEMC 速率。了解這個 LEMC 速率很重要,因為任何成功的 MCS 例程都需要證明不是 LEMC 速率整數(shù)倍的 RF 頻率能夠?qū)崿F(xiàn)確定性的上電階段。

多芯片同步方式

在該系統(tǒng)中,寬帶集成 ADC/DAC IC 提供 MCS 電路,以允許所有發(fā)射和接收 RF 通道上的上電確定性相位,即使在使用 IC 內(nèi)的 DUC/DDC DSP 模塊時也是如此。此 MCS 功能使用戶能夠在工廠校準(zhǔn)期間填充查找表 (LUT),以最大限度地減少操作停機時間。任何成功的 MCS 演示都必須能夠為每個嘗試的射頻頻率、熱梯度和系統(tǒng)功率循環(huán)提供系統(tǒng)內(nèi)所有通道的確定性相位。

集成的 ADC/DAC IC 包含 12 個 DUC 模塊和 12 個 DDC 模塊,如上圖 1 所示。這些模塊中的每一個都包含一個插值 (DUC) 或抽取 (DDC) 子模塊,用于更改 DAC 數(shù)字輸入信號的數(shù)據(jù)速率或ADC分別數(shù)字化輸出信號。每個 DUC/DDC 中還包含一個復(fù)雜的數(shù)控振蕩器 (NCO),它允許在數(shù)字域內(nèi)進行頻率轉(zhuǎn)換。這些 NCO 中的每一個都能夠進行實時復(fù)雜相位調(diào)整,以便可以修改 DAC/ADC 和 BBP 之間的數(shù)字信號,以補償各種 SERDES 走線長度不匹配。

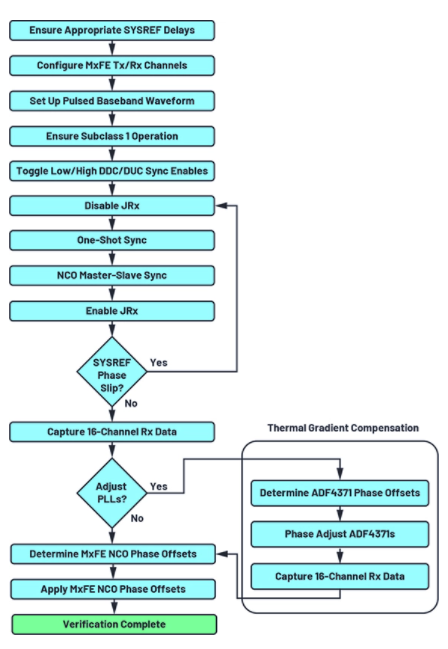

這些 ADC/DAC IC 的 MCS 功能負(fù)責(zé)在數(shù)字化儀 IC 數(shù)據(jù)路徑的所有方面實現(xiàn)相位確定性。實現(xiàn) MCS 的工作流程如圖 2 所示。

圖 2. MCS 工作流程涉及對齊數(shù)據(jù)路徑不同部分的單獨功能。(來源:ADI)

MCS算法可以分為兩個獨立的功能:

一次性同步:此功能負(fù)責(zé)對齊通過子陣列系統(tǒng)內(nèi)所有數(shù)字化儀 IC 的物理通道發(fā)送的基帶數(shù)據(jù)。

NCO 主從同步:此功能負(fù)責(zé)對齊子陣列系統(tǒng)內(nèi)所有不同數(shù)字化儀 IC 中的所有 NCO。

一次性同步功能首先要求用戶定義 JESD 鏈路參數(shù)(例如 M、N’、L 等),然后為任何所需的 SYSREF 平均配置同步邏輯(如果使用連續(xù) SYSREF 脈沖)。此外,可以使用所需的 LEMC 延遲來強制 LEMC 在 SYSREF 邊沿之后的某個延遲處生成。完成此操作后,用戶隨后啟用每個數(shù)字化儀 IC 內(nèi)的一次性同步位,然后請求在同一時鐘周期內(nèi)將 SYSREF 脈沖發(fā)送到每個 IC,如圖 3 所示。

圖 3. MCS 算法使用 SYSREF 信號實現(xiàn) one-shot 同步,使用 GPIO 信號實現(xiàn) NCO 主從同步以實現(xiàn)確定性相位。(來源:ADI)

對于這個系統(tǒng),在時鐘緩沖器 IC 中引入了模擬精細(xì)延遲,以允許同步 SYSREF 到所有數(shù)字化儀 IC。可以通過查詢每個 IC 內(nèi)的寄存器來執(zhí)行后續(xù)檢查,以驗證一次性同步過程是否成功執(zhí)行,這些寄存器提供有關(guān) SYSREF 信號和每個 IC 鏈路的 LEMC 邊界之間的相位關(guān)系的信息。

一旦測量到穩(wěn)定相位(即一旦 SYSREF-LEMC 相位寄存器讀取 0),用戶就知道所有數(shù)字化儀 IC 的 LEMC 已對齊,然后用戶可以繼續(xù)進行 NCO 主從同步過程。對于此活動,為一次性同步描述的子任務(wù)包含在芯片制造商提供的應(yīng)用程序編程接口 (API) 中。

NCO 主從同步功能首先將子陣列中的一個數(shù)字化儀 IC 指定為主芯片,如圖 3 所示。然后,所有其他數(shù)字化儀都被視為從屬 IC。主 IC 的設(shè)置使該設(shè)備的 GPIO0 引腳配置為輸出并路由到三個從屬數(shù)字化儀 IC 的 GPIO0 網(wǎng)絡(luò)。從 GPIO0 網(wǎng)絡(luò)配置為輸入。然后,用戶可以選擇在 SYSREF 脈沖、LEMC 上升沿或 LEMC 下降沿觸發(fā)。對于本文中顯示的數(shù)據(jù),LEMC 上升沿用作 NCO 主從同步觸發(fā)源,GPIO 網(wǎng)絡(luò)通過 BBP 路由,而不是在子陣列上本地路由。接下來,將 DDC 同步位切換為低電平,然后切換為高電平以啟動 ADC 端 NCO 同步算法。同樣地,

當(dāng)請求此觸發(fā)時,在下一個 LEMC 上升沿,主數(shù)字化儀 IC 通過其 GPIO0 網(wǎng)絡(luò)將主輸出信號置為高電平。該信號傳播到每個從設(shè)備的 GPIO0 輸入。在下一個 LEMC 邊緣,所有數(shù)字化儀 IC 都會經(jīng)歷 NCO 復(fù)位算法。此后,對于 NCO 主從同步算法,任何 LEMC 脈沖都將被忽略。與一次性同步一樣,這些 NCO 主從同步子任務(wù)包含在 API 函數(shù)中,以方便用戶使用。

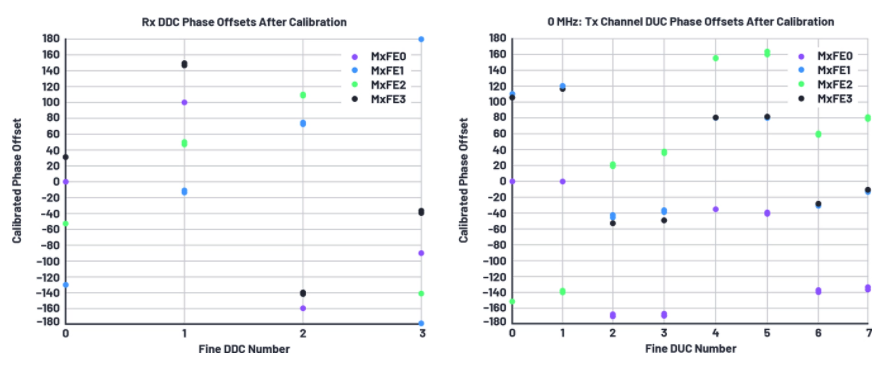

使用一次性同步和 NCO 主從同步功能可將兩個輸入與每個 DDC/DUC 對齊,以便每個接收和發(fā)送通道的輸出相位偏移在多個電源周期后可重復(fù),如圖 4 所示。圖 4 中顯示了在每次重啟期間系統(tǒng)在靜態(tài)熱梯度下運行時,每個接收和發(fā)送信道器在 100 個電源周期(由多個實心點表示)上的校準(zhǔn)相位偏移。

圖 4. 執(zhí)行 MCS 算法時,接收精細(xì) DDC(左)和發(fā)送精細(xì) DUC(右)正確對齊。(來源:ADI)

從該圖中的多個點可以看出,給定 DDC/DUC 的每種顏色的點在電源循環(huán)后都緊密聚集到同一位置,從而描繪了該特定通道的確定性階段。對于本次測試中的數(shù)據(jù),所有八個通道器 DUC 都已用于發(fā)送端,而八個通道器 DDC 中僅使用了四個。然而,已經(jīng)證實確實所有八個信道器 DDC 在使用 MCS 算法的同時也提供確定性相位。

如果 PLL 合成器采樣時鐘和時鐘 IC SYSREF 在啟動時保持相同的相位關(guān)系,則在啟動時發(fā)出此算法將為每個通道建立確定性相位。然而,任何系統(tǒng)都會經(jīng)歷熱梯度,這會導(dǎo)致 PLL 時鐘漂移,如果不進行補償,可能會導(dǎo)致不同的上電階段。為了補償系統(tǒng)內(nèi)的熱梯度漂移,該平臺利用 PLL 合成器相位調(diào)整。

在本系列文章的下一部分中,我們將探討 PLL 合成器相位調(diào)整、多個子陣列的可擴展性以及系統(tǒng)級校準(zhǔn)算法。

參考

1 德爾瓊斯。“ JESD204C 入門:有哪些新內(nèi)容和內(nèi)容適合您——第 1 部分。” 模擬對話,卷。53,第 2 號,2019 年 6 月。

2 德爾瓊斯。“ JESD204C 入門:有哪些新內(nèi)容和內(nèi)容適合您——第 2 部分。” 模擬對話,卷。53,第 3 號,2019 年 7 月。

Mike Jones是 ADI 公司的首席電氣設(shè)計工程師,在北卡羅來納州格林斯伯勒的航空航天和國防業(yè)務(wù)部門工作。他于 2016 年加入 ADI。從 2007 年到 2016 年,他在北卡羅來納州威爾明頓的通用電氣工作,擔(dān)任微波光子設(shè)計工程師,專注于核工業(yè)的微波和光學(xué)解決方案。他于 2004 年獲得北卡羅來納州立大學(xué)的 BSEE 和 BSPE,并于 2006 年獲得北卡羅來納州立大學(xué)的 MSEE。

Michael Hennerich于 2004 年加入 ADI。作為一名系統(tǒng)和應(yīng)用設(shè)計工程師,他從事各種基于 DSP/FPGA 和嵌入式處理器的應(yīng)用和參考設(shè)計。Michael 現(xiàn)在在德國慕尼黑的 System Development Group (SDG) 擔(dān)任開源系統(tǒng)工程經(jīng)理。在這個職位上,他領(lǐng)導(dǎo) ADI 的設(shè)備驅(qū)動程序和內(nèi)核開發(fā)團隊,為各種混合信號 IC 產(chǎn)品和 HDL 接口內(nèi)核開發(fā)設(shè)備驅(qū)動程序。他擁有碩士學(xué)位。計算機工程學(xué)位和Dipl.-Ing。(FH) 羅伊特林根大學(xué)電子和信息技術(shù)學(xué)位。

Peter Delos是位于北卡羅來納州格林斯伯勒的 ADI 公司航空航天和國防事業(yè)部的技術(shù)主管。他于 1990 年獲得弗吉尼亞理工大學(xué)電氣工程學(xué)士學(xué)位,并于 2004 年獲得新澤西理工學(xué)院電氣工程碩士學(xué)位。Peter 擁有超過 25 年的行業(yè)經(jīng)驗。他職業(yè)生涯的大部分時間都花在設(shè)計架構(gòu)級、PWB 級和 IC 級的高級射頻/模擬系統(tǒng)上。他目前專注于小型化用于相控陣應(yīng)用的高性能接收器、波形發(fā)生器和合成器設(shè)計。

-

dsp

+關(guān)注

關(guān)注

556文章

8148瀏覽量

355698 -

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614953 -

基帶處理器

+關(guān)注

關(guān)注

0文章

20瀏覽量

13381 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1055瀏覽量

84023

發(fā)布評論請先 登錄

應(yīng)用分享 | 精準(zhǔn)生成和時序控制!AWG在確定性三量子比特糾纏光子源中的應(yīng)用

解析相位噪聲測試

優(yōu)刻得:與DeepSeek模型適配,業(yè)績貢獻存不確定性

AFE5808A串并變換之后數(shù)據(jù)錯位,輸出結(jié)果具有不確定性,為什么?

多片AFE5818的輸入ADC時鐘為同步時鐘,不同的芯片上LVDS串行數(shù)據(jù)時鐘和幀時鐘是否是同步的?

請問DAC38J84內(nèi)部NCO和基帶信號確定性相位關(guān)系如何配置?

求助,關(guān)于LMX2572LP多片時鐘芯片同步的疑問求解

eeprom芯片型號怎么確定

計及多重不確定性的規(guī)模化電動汽車接入配電網(wǎng)調(diào)度方法及解決方案

中國移動完成業(yè)界首例端到端雙頻5G-A確定性網(wǎng)絡(luò)試點

DP83826確定性、低延遲、低功耗、10/100Mbps工業(yè)以太網(wǎng)PHY數(shù)據(jù)表

上電相位確定性:使用多芯片同步

上電相位確定性:使用多芯片同步

評論