加密的優(yōu)點(diǎn)

xilinx的V6和7全系列FPGA支持AES256加密,加密的好處:

1,可以防止別人回讀或者對(duì)你的程序進(jìn)行逆向;

2,防止更改燒寫(xiě)的bit文件。

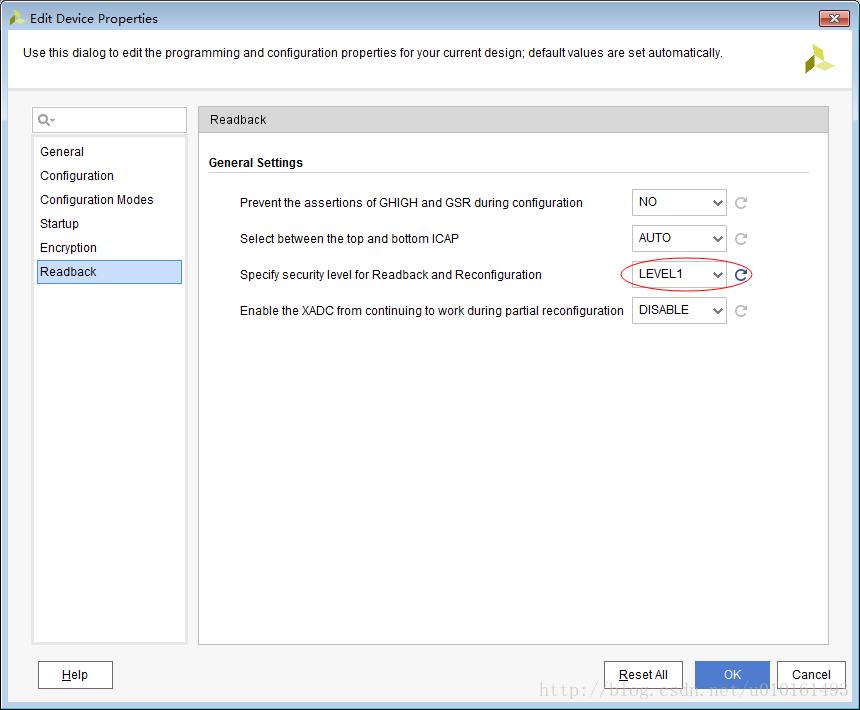

如果僅僅是防止回讀,可以簡(jiǎn)單設(shè)置BITSTREAM.READBACK.SECURITY,其中LEVEL1是禁止回讀,LEVEL2禁止回讀和重新燒寫(xiě)FPGA。

但如果對(duì)手的逆向能力很強(qiáng),比如說(shuō)在FPGA上電加載bit的時(shí)候用邏輯分析儀把用bit文件“讀”出來(lái),這個(gè)簡(jiǎn)單的設(shè)置肯定就不行了。這時(shí)候可以使用AES256加密。

AES算法簡(jiǎn)介:

AES即高級(jí)加密標(biāo)準(zhǔn),是一種區(qū)塊加密,當(dāng)然也是對(duì)稱(chēng)加密。區(qū)塊固定為128bit,秘鑰為128,192或256bit。AES有5種加密模式,xliinx采用的是CBC模式。有一個(gè)128bit初始向量IV(startCBC),先利用初始向量IV與第一組數(shù)據(jù)進(jìn)行異或后再進(jìn)行加密運(yùn)算生成C1。將C1作為初始向量與第二組數(shù)據(jù)進(jìn)行異或后再進(jìn)行加密運(yùn)算生成C2。以此類(lèi)推,當(dāng)最后一組數(shù)據(jù)加密完畢后,將加密結(jié)果拼接為最終結(jié)果,C = C1C2C3……Cn。

所以采用CBC模式的256AES需要兩個(gè)東西,128bit-startCBC和256bit-AES key。

到這里還沒(méi)完,完成了bit加密還沒(méi)有認(rèn)證,萬(wàn)一別人把燒進(jìn)去bit文件篡改了怎么辦?(重新燒了新的bit文件)。所以xilinx又提供了HMAC的認(rèn)證,這個(gè)就跟校驗(yàn)差不多了,檢查消息的完整性。

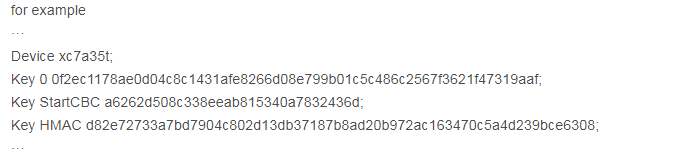

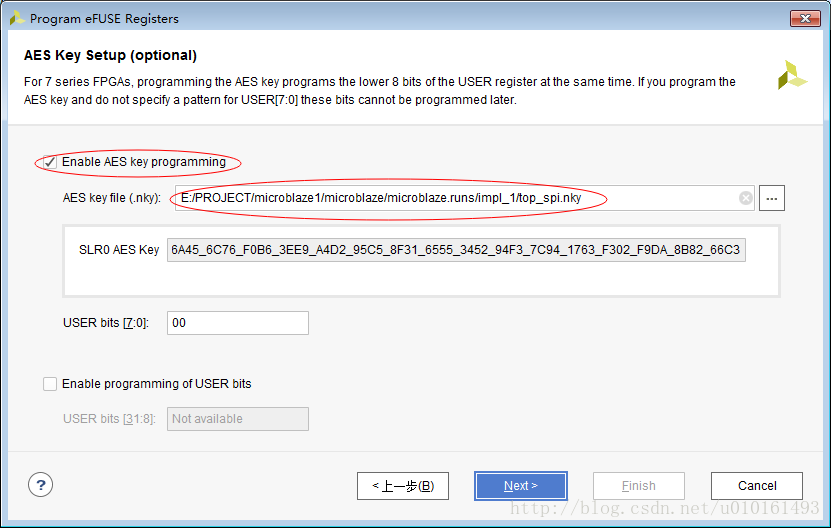

所以還需要提供256bit-HMAC,加上128bit-startCBC和256bit-AES key,一共是三個(gè)。這三個(gè)key可以自己生成,也可以指定空的 .nky文件,由軟件隨機(jī)生成好。

加密的AES key可以存到FPGA內(nèi)部易失性的BBR或只能燒寫(xiě)一次(OTP)的eFUSE中。

BBR需要電池供電,可以多次編程。eFUSE不需要電池,但只能燒寫(xiě)一次。這里使用eFUSE

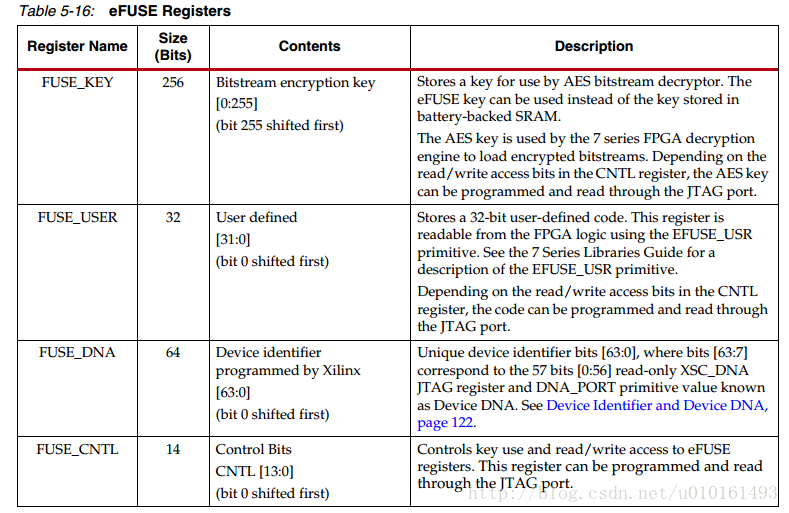

eFUSE寄存器

首先來(lái)看一下eFUSE寄存器:

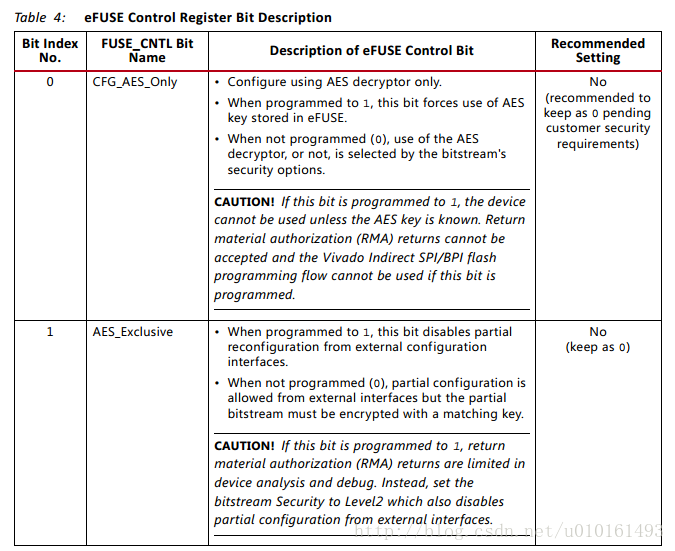

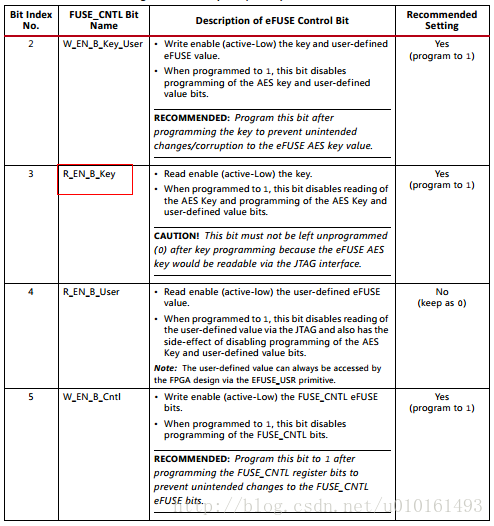

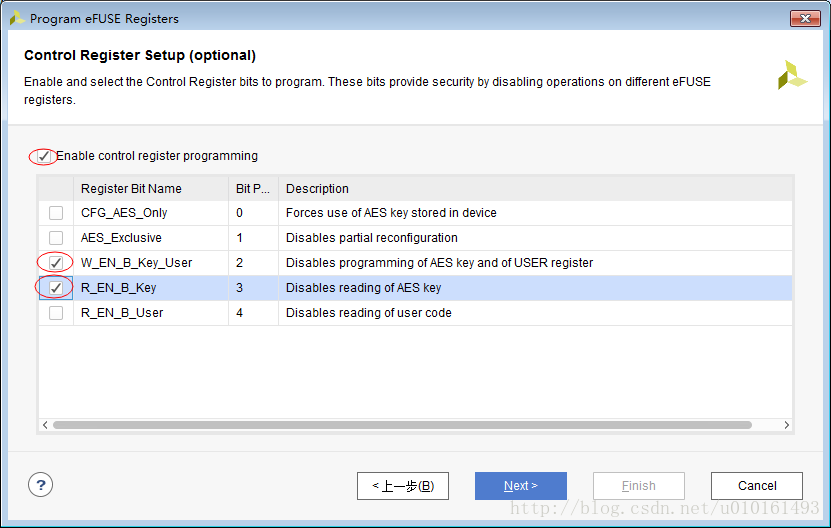

一共有四個(gè)寄存器,分別是存放AES秘鑰,用戶(hù)信息,設(shè)備DNA和eFUSE控制。下面特別關(guān)注一下eFUSE控制寄存器:

一共有6個(gè)bit有用,各種設(shè)置的優(yōu)缺點(diǎn)表里有詳細(xì)說(shuō)明,使用參考設(shè)置101100就行了。

其中bit0很重要,萬(wàn)一置位了,AES的key又搞丟了,F(xiàn)PGA就變磚頭了。

具體的操作步驟如下:

1生成key和加密bit

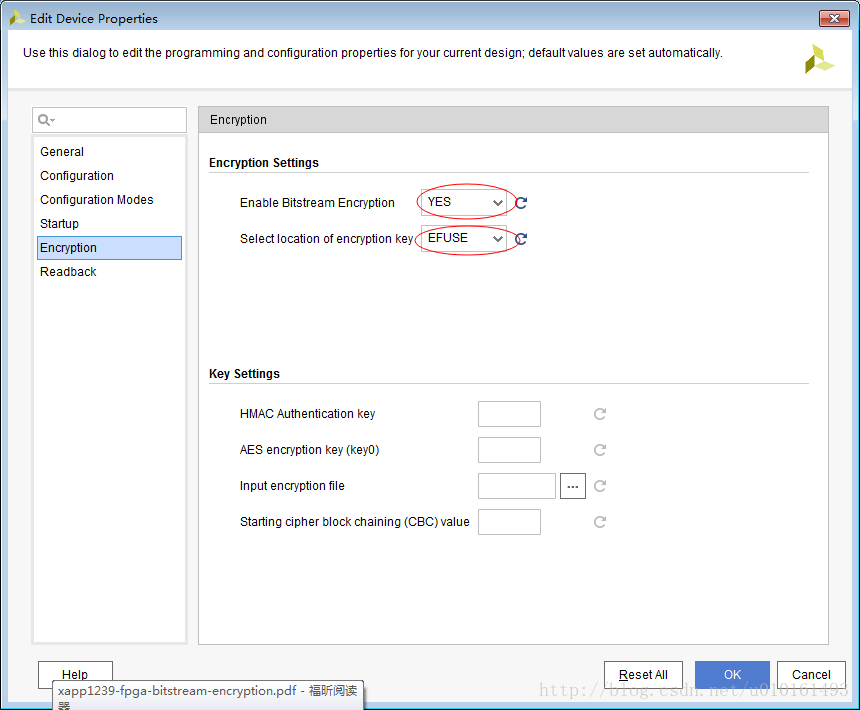

下面三個(gè)key可以自己生成填進(jìn)去,也可以由軟件隨機(jī)生成。

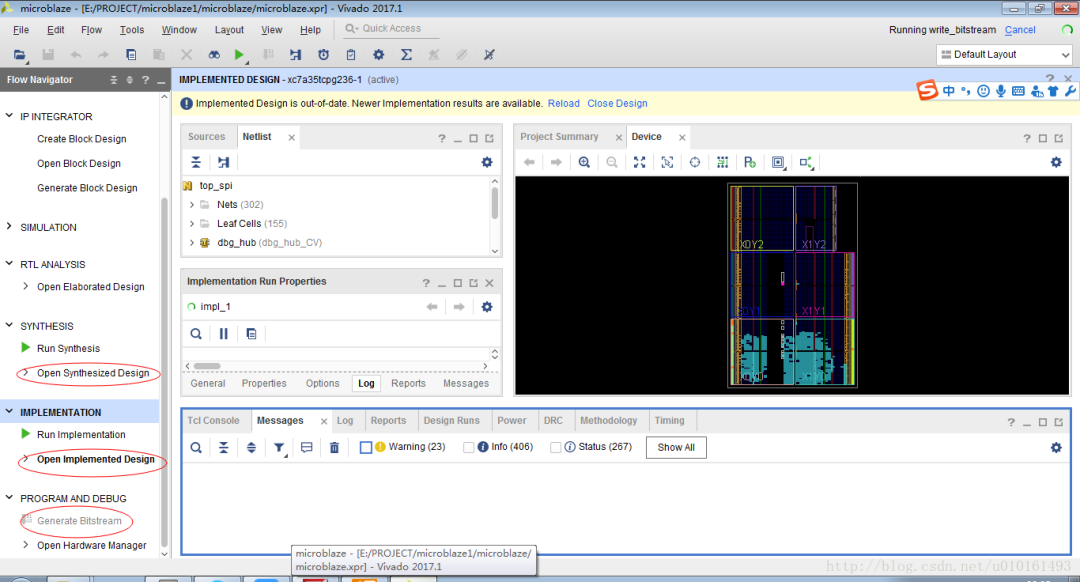

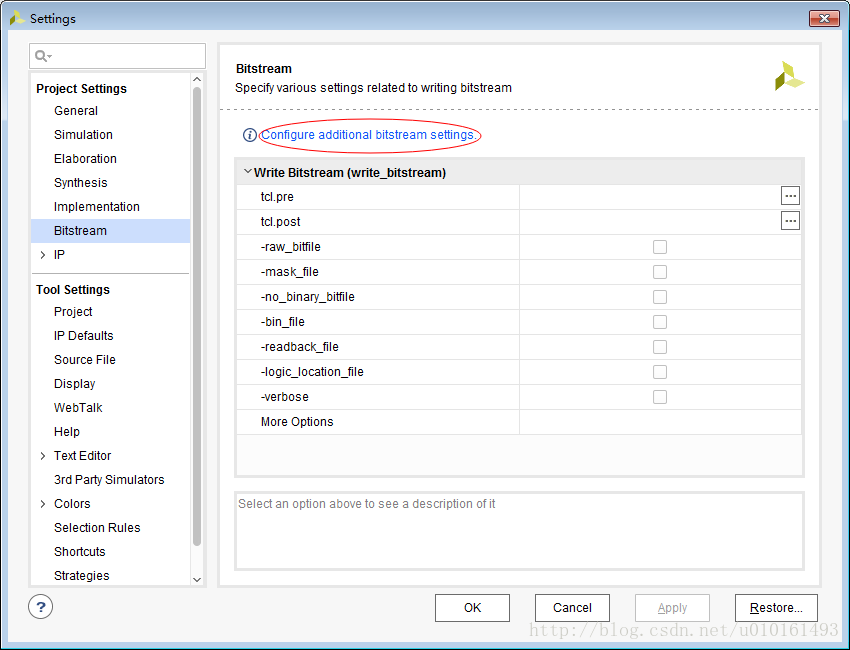

要打開(kāi)edit device properties,先要打開(kāi)sythesized design 或者implement design,然后在generate bitstream右鍵設(shè)置

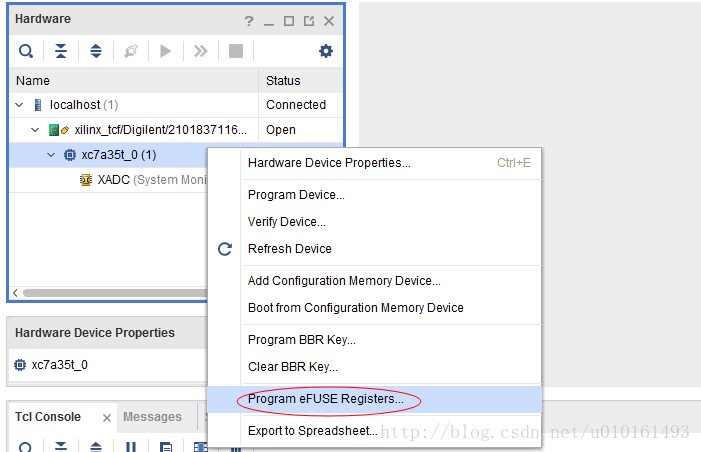

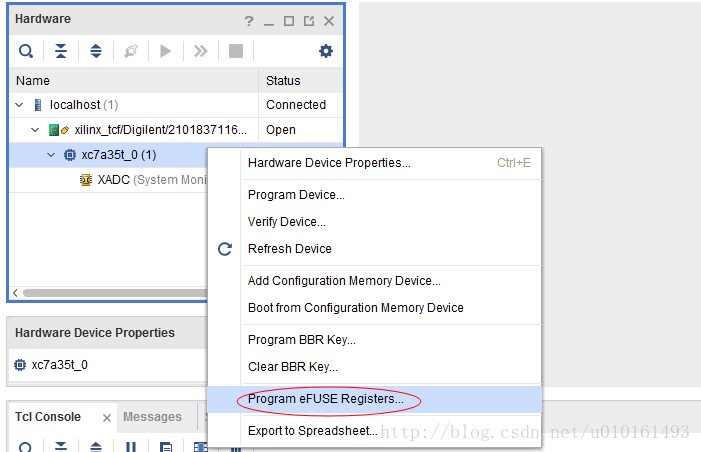

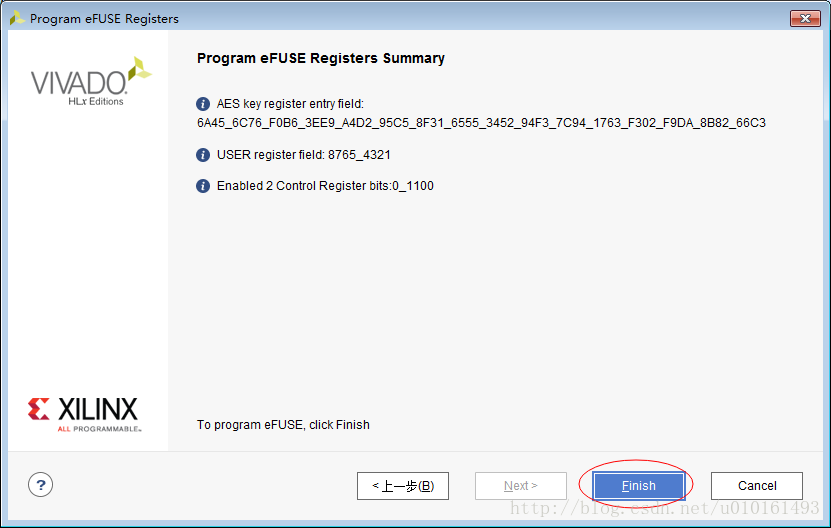

2下載eFUSE

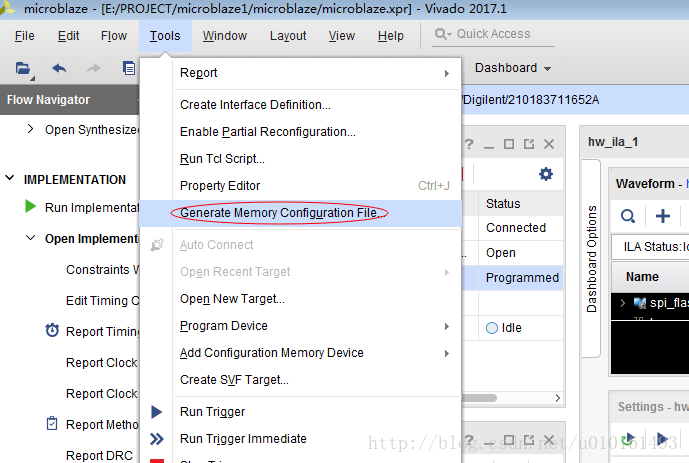

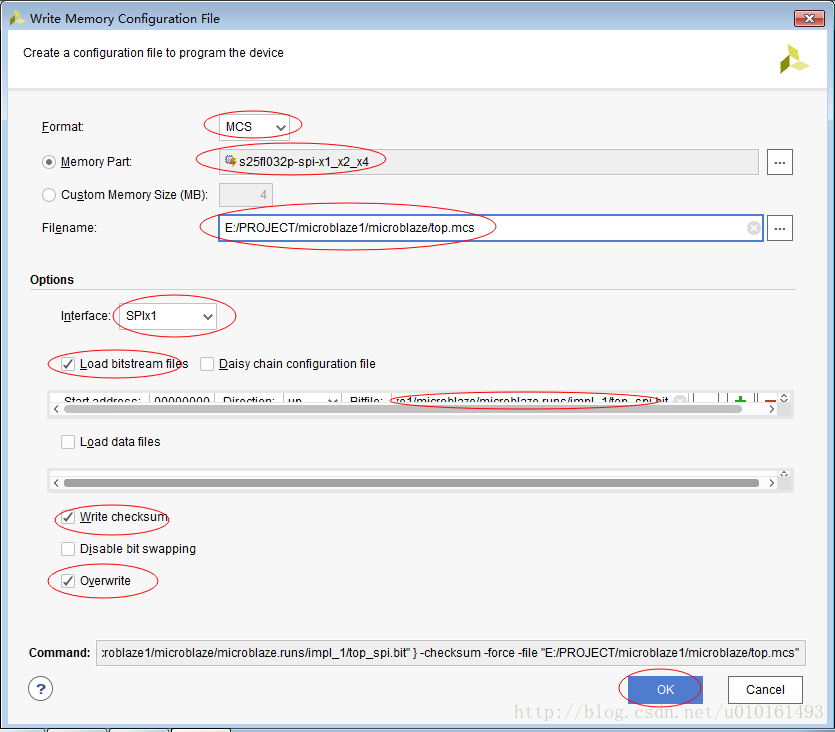

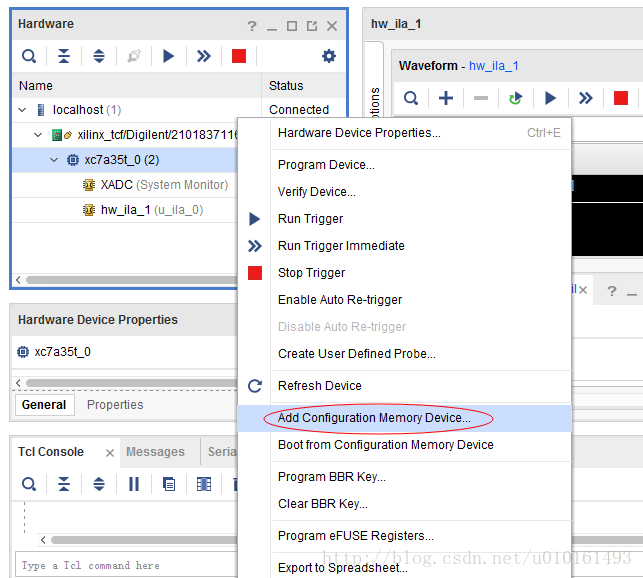

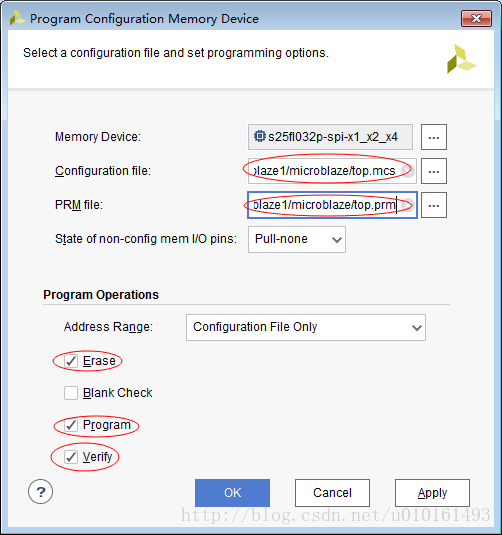

3燒寫(xiě)FPGA程序

program

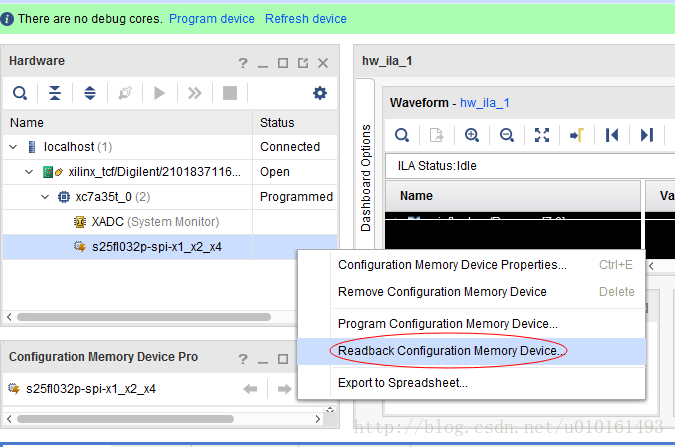

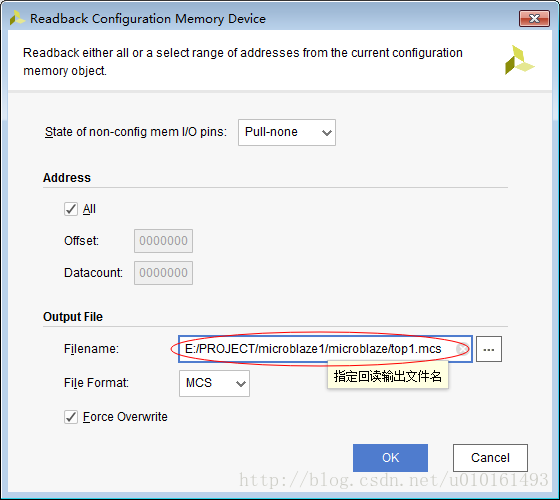

4驗(yàn)證

很簡(jiǎn)單,讀出mcs然后燒到另一個(gè)FPGA里面去,可以看到不能工作。當(dāng)然,也可以在前面eFUSE設(shè)置時(shí)選擇只能加載AES加密的bit文件,這樣換一個(gè)不加密的bit下進(jìn)去也能驗(yàn)證。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615412 -

算法

+關(guān)注

關(guān)注

23文章

4702瀏覽量

94971 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

124593

原文標(biāo)題:FPGA學(xué)習(xí)-如何對(duì)xilinx FPGA進(jìn)行bit文件加密

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA遠(yuǎn)程燒寫(xiě)bit文件和調(diào)試ILA指南

XILINX XCZU67DR FPGA完整原理圖

如何在MBDT中使用S32k344進(jìn)行加密?

xilinx FPGA IOB約束使用以及注意事項(xiàng)

使用xilinx的k7160t對(duì)ads5271的數(shù)字信號(hào)進(jìn)行采集,外部輸入電壓時(shí),FPGA采集到的值比實(shí)際的值大,怎么解決?

基于Xilinx ZYNQ7000 FPGA嵌入式開(kāi)發(fā)實(shí)戰(zhàn)指南

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】測(cè)試一

ADC3583怎么用Xilinx的ISERDESE2采集信號(hào)?

采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+04.SFP之Aurora測(cè)試(zmj)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+03.SFP光口測(cè)試(zmj)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+02.PCIE接口測(cè)試(zmj)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

如何對(duì)xilinx FPGA進(jìn)行bit文件加密

如何對(duì)xilinx FPGA進(jìn)行bit文件加密

評(píng)論