RISC-V 被稱為開放標準指令集架構 (ISA),其基本指令已被凍結以最小化復雜性。但最近它添加了廣泛的自定義擴展和增強功能,使其在構建特定應用系統的 SoC 設計人員中越來越受歡迎。

這些架構中采用的定制功能通常通過硬件/軟件協同設計策略得到增強,該策略優化軟件以最大限度地發揮 RISC-V 處理器 IP 的專業能力。

但無論系統是否在軟硬件協同設計環境中開發,構建穩定的 SoC 設計和驗證流程的過程仍然涉及大量設置和耗時的手動更改。研究估計 SoC 驗證占用了 SoC 總設計時間和成本的 50-80%,而且使用 RISC-V 處理器的驗證工程師的工作量比 Arm SoC 還要多,因為 CPU 本身以及任何定制都必須經過驗證。

RISC-硬件設計驗證提供商 Imperas 最近的一份聲明稱:“開源 IP 的日益普及也促進了將驗證作為進貨質量檢查作為 SoC 項目初始階段的一部分的團隊的增長。” V 處理器模型和用于軟件仿真的虛擬原型,讀取。“此外,修改或擴展基本核心功能的設計選項從一開始就取決于一個有效的設計驗證框架。”

圍繞可定制的 RISC-V IP 規范化驗證

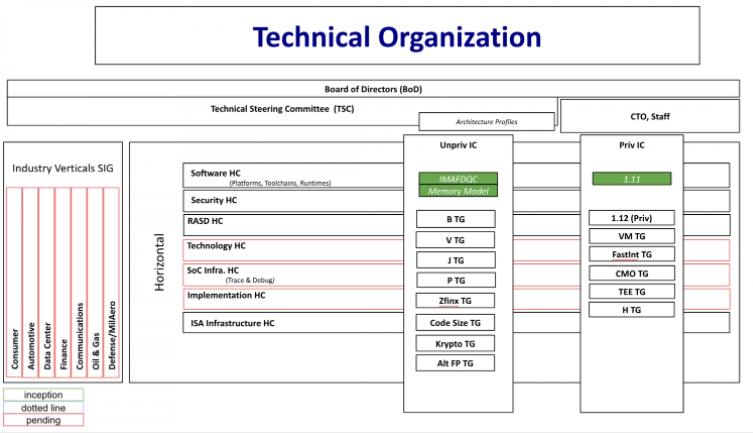

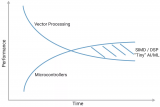

事實上,隨著 RISC-V 的成熟,越來越多的設計團隊選擇“修改或擴展基本核心功能”,以至于 RISC-V 基金會已經組織了特殊興趣小組來規范目標用例的擴展功能集。這些工作組可以在下圖的左側看到,自春季發布該表以來,其中許多已經從待處理轉變為活動。

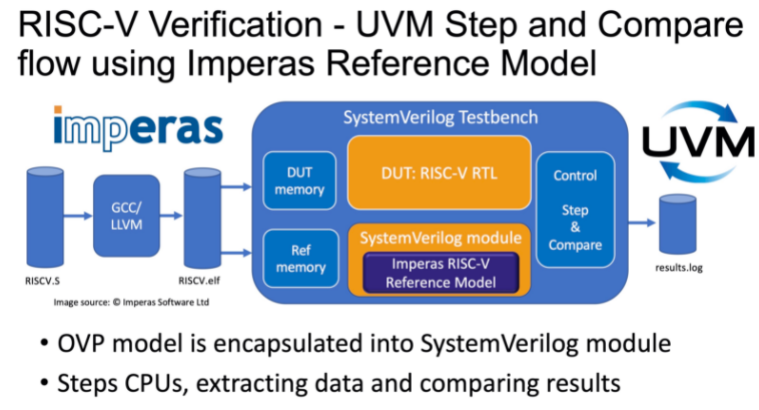

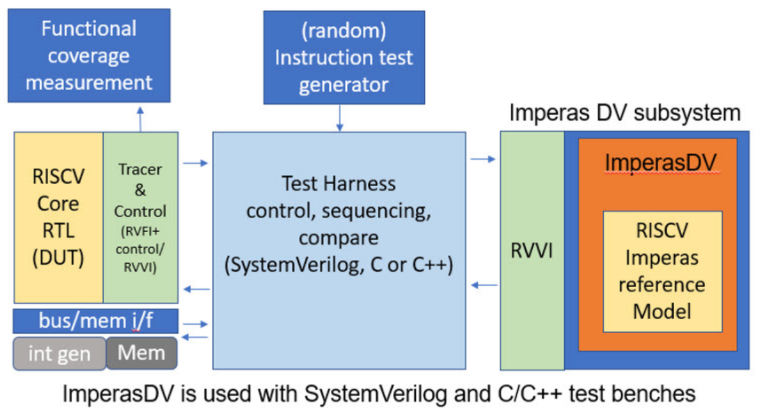

作為回應,ImperasDV 工具正在尋求通過與當前 UVM SystemVerilog 技術兼容的“黃金參考模型”來簡化 RISC-V SoC 設計驗證過程。它的環境采用鎖步比較設計驗證方法,允許在 Verilog 或 SystemVerilog 中編程的被測設備 (DUT) 運行和構建裝配級程序。這有助于解決異步事件,從而在發現錯誤時減少調試分析時間。

該工具的主要組成部分是:

指令測試生成器

RTL DUT 子系統

功能覆蓋測量

測試臺/線束

Imperas DV 子系統

該工具的外殼可容納整個 RISC-V ISA,包括特權操作模式,并與最新的 Vector、DSP/SIMD、Bitmanip 和 Crypto (Scalar) 擴展兼容。從架構的角度來看,ImperasDV 提供了一個支持 RISC-V 驗證接口 (RVVI) 標準的驗證環境。這簡化了客戶 RTL、參考模型和測試平臺之間的集成。

如前所述,該集成有助于復雜超標量流水線的鎖步和比較驗證,并且該平臺可以容納多個硬件線程并完成無序指令。Imperas 的黃金參考模型確保平臺評估的操作數據正確執行,即使跨不同版本,這要歸功于對特定修訂的可配置版本控制支持。

開源協同設計現在開始

ImperasDV RISC-V 驗證工具鏈已被許多半導體行業領先的 RISC-V 供應商采用,其中一些供應商已經擁有可工作的硅原型,目前正致力于第二代設計。其中包括 Codasip、EM Microelectronics (Swatch)、NSITEXE (Denso)、Nvidia Networking (Mellanox)、OpenHW Group、MIPS Technology、Seagate Technology、Silicon Labs 和 Valtrix Systems,以及其他尚未公開的公司。

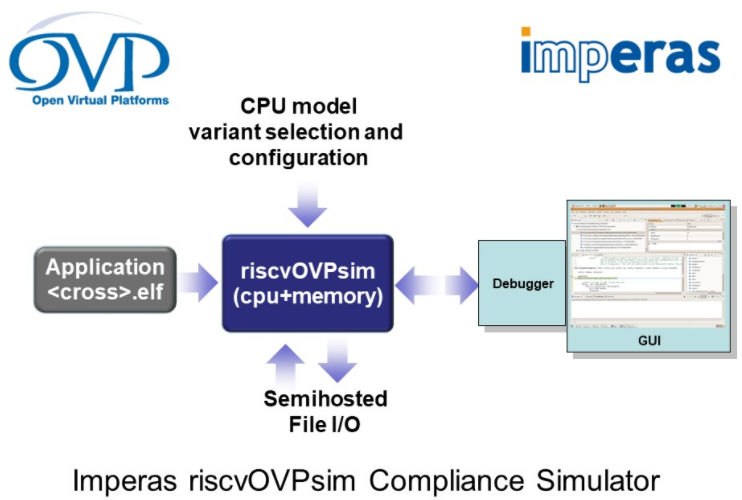

當然,我們還沒有解決硬件/軟件協同設計等式的另一面:嵌入式軟件開發。在這里,Imperas 還通過建模和仿真解決方案加快設計周期,只是這些解決方案基于開源開放虛擬平臺 (OVP) 模型。

該公司的riscvOVPsim 指令集模擬器 (ISS)允許以高達 1,000 MIPS 的速度開發和調試針對 RISC-V 處理器目標的代碼。它利用 Imperas 的 OVP 快速處理器模型庫來提供指令精確的單核 RISC-V 配置和變體,甚至被 RISC-V 基金會的合規性框架和測試套件使用。

最重要的是,可以從 GitHub 免費下載riscvOVPsim,并且可以在www.ovpworld.org/riscvOVPsimPlus找到包含新 RISC-V 矢量擴展的增強測試套件。

riscvOVPsim 的可用升級包括虛擬平臺開發和仿真、多核軟件開發、可擴展平臺套件和多處理器主機 (MPonMP) 加速軟件上的 QuantumLeap 多處理器目標。

Imperas 產品組合以及來自快速發展的 RISC-V 生態系統的其他工具,為您今天開始自己的開放式處理器設計提供了足夠的資源。

作者:Brandon Lewis,Saumitra Jagdale

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19833瀏覽量

233979 -

嵌入式

+關注

關注

5144文章

19578瀏覽量

315879 -

RISC-V

+關注

關注

46文章

2514瀏覽量

48432

發布評論請先 登錄

HPM5E31IGN單核 32 位 RISC-V 處理器

新思科技RISC-V處理器助力低功耗嵌入式應用

Arm與RISC-V架構的優劣勢比較

RISC-V MCU技術

Imagination放棄RISC-V處理器內核開發

Andes晶心科技推出D45-SE RISC-V處理器

Rivos全新產品采用Andes晶心科技NX45 RISC-V處理器

《RISC-V能否復制Linux 的成功?》

什么是RISC-V?以及RISC-V和ARM、X86的區別

RISC-V筆記——基礎

定制RISC-V處理器簡化設計驗證

定制RISC-V處理器簡化設計驗證

評論