加利福尼亞州圣克拉拉——應(yīng)用材料公司宣布推出一種全新系統(tǒng),可改進(jìn)晶體管布線沉積工藝,從而大幅降低電阻,突破了芯片在性能提升和功率降低兩方面所面臨的重大瓶頸。

Endura? Ioniq? PVD系統(tǒng)是應(yīng)用材料公司在解決二維微縮布線電阻難題方面所取得的最新突破。Ioniq系統(tǒng)是一種集成材料解決方案?(IMS?),可將表面制備、PVD和CVD工藝同時(shí)集中到同一個(gè)高真空系統(tǒng)中。

芯片制造商正在利用光刻領(lǐng)域的先進(jìn)技術(shù)將芯片制程縮小至3納米及以下節(jié)點(diǎn)。但隨著互連線變細(xì),電阻呈現(xiàn)指數(shù)級(jí)上升,這不僅降低了芯片性能,還增大了功耗。如果該問(wèn)題無(wú)法得到解決,更為先進(jìn)的晶體管帶來(lái)的益處將被指數(shù)級(jí)上升的布線電阻完全抵消。

芯片布線一般指沉積金屬在介電材料上被刻蝕出的溝槽和通孔內(nèi)的過(guò)程。在傳統(tǒng)工藝中,布線沉積使用的金屬疊層通常由以下幾部分構(gòu)成:阻擋層用于防止金屬與介電材料擴(kuò)散;襯墊層用于提升粘附力;種子層用于促進(jìn)金屬填充;以及導(dǎo)電金屬,例如鎢或鈷用于晶體管觸點(diǎn),銅用于互連線。因?yàn)樽钃鯇雍鸵r墊層很難微縮,所以當(dāng)溝槽和通孔尺寸減小時(shí),可用于導(dǎo)電材料的空間比例隨之降低——互連線越小,電阻越高。

應(yīng)用材料公司Endura? Ioniq? PVD系統(tǒng)

Ioniq PVD system是一種集成材料解決方案?(IMS?),可將表面制備、PVD和CVD工藝同時(shí)集中到同一個(gè)高真空系統(tǒng)中。Ioniq PVD給芯片制造商提供了用低阻值的純鎢PVD膜取代高阻值的氮化鈦襯墊層和阻擋層的方案,配合后續(xù)的純鎢CVD膜制成純鎢的金屬觸點(diǎn)。該方案解決了電阻難題,讓二維微縮得以繼續(xù)作用于3納米及以下節(jié)點(diǎn)。

應(yīng)用材料公司半導(dǎo)體產(chǎn)品事業(yè)部高級(jí)副總裁兼總經(jīng)理珀拉布?拉賈博士表示:“應(yīng)用材料公司在解決電阻難題方面所取得的最新突破,是一個(gè)材料工程創(chuàng)新使得二維微縮得以延續(xù)的絕佳范例。創(chuàng)新的Ioniq PVD系統(tǒng)打破了晶體管性能提升所面臨的一個(gè)重大瓶頸,使其在運(yùn)行速度更快的同時(shí)降低了功率損失。隨著芯片復(fù)雜度的提升,在高真空中集成多個(gè)工藝的能力對(duì)于客戶(hù)改進(jìn)布線以達(dá)到其性能和功率的目標(biāo)來(lái)說(shuō)至關(guān)重要。”

Endura Ioniq PVD系統(tǒng)現(xiàn)已被全球多家行業(yè)領(lǐng)先的客戶(hù)使用。如需了解更多有關(guān)該系統(tǒng)的信息或者其它用于解決關(guān)鍵布線和互連難題的應(yīng)用材料公司解決方案,請(qǐng)關(guān)注應(yīng)用材料公司在美國(guó)時(shí)間5月26日舉辦的“芯片布線和集成的新方法”大師課。

關(guān)于應(yīng)用材料公司

應(yīng)用材料公司(納斯達(dá)克:AMAT)是材料工程解決方案的領(lǐng)導(dǎo)者,全球幾乎每一個(gè)新生產(chǎn)的芯片和先進(jìn)顯示器的背后都有應(yīng)用材料公司的身影。憑借在規(guī)模生產(chǎn)的條件下可以在原子級(jí)層面改變材料的技術(shù),我們助力客戶(hù)實(shí)現(xiàn)可能。應(yīng)用材料公司堅(jiān)信,我們的創(chuàng)新實(shí)現(xiàn)更美好的未來(lái)。欲知詳情,請(qǐng)?jiān)L問(wèn)www.appliedmaterials.com。

近期會(huì)議

2022年7月5日,由ACT雅時(shí)國(guó)際商訊主辦,《半導(dǎo)體芯科技》&CHIP China晶芯研討會(huì)將在蘇州·洲際酒店隆重舉行!屆時(shí)業(yè)內(nèi)專(zhuān)家將齊聚蘇州,與您共探半導(dǎo)體制造業(yè),如何促進(jìn)先進(jìn)制造與封裝技術(shù)的協(xié)同發(fā)展。大會(huì)現(xiàn)已啟動(dòng)預(yù)約登記,報(bào)名請(qǐng)點(diǎn)擊://w.lwc.cn/s/maymIv

2022年7月28日 The12th CHIP China Webinar,誠(chéng)邀您與業(yè)內(nèi)專(zhuān)家學(xué)者共探半導(dǎo)體器件檢測(cè)面臨的挑戰(zhàn)及應(yīng)對(duì)、工藝缺陷故障、光學(xué)檢測(cè)特性分析與挑戰(zhàn)、先進(jìn)封裝半導(dǎo)體檢測(cè)難點(diǎn)及應(yīng)用等熱門(mén)話題,解鎖現(xiàn)代檢測(cè)技術(shù)的創(chuàng)新發(fā)展和機(jī)遇!

關(guān)于我們

《半導(dǎo)體芯科技》(Silicon Semiconductor China, SiSC)是面向中國(guó)半導(dǎo)體行業(yè)的專(zhuān)業(yè)媒體,已獲得全球知名雜志《Silicon Semiconductor》的獨(dú)家授權(quán);本刊針對(duì)中國(guó)半導(dǎo)體市場(chǎng)特點(diǎn)遴選相關(guān)優(yōu)秀文章翻譯,并匯集編輯征稿、國(guó)內(nèi)外半導(dǎo)體行業(yè)新聞、深度分析和權(quán)威評(píng)論、產(chǎn)品聚焦等多方面內(nèi)容。由雅時(shí)國(guó)際商訊(ACT International)以簡(jiǎn)體中文出版、雙月刊發(fā)行一年6期。每期紙質(zhì)書(shū)12,235冊(cè),電子書(shū)發(fā)行15,749,內(nèi)容覆蓋半導(dǎo)體制造工藝技術(shù)、封裝、設(shè)備、材料、測(cè)試、MEMS、IC設(shè)計(jì)、制造等。每年主辦線上/線下 CHIP China晶芯研討會(huì),搭建業(yè)界技術(shù)的有效交流平臺(tái)。

審核編輯:湯梓紅

-

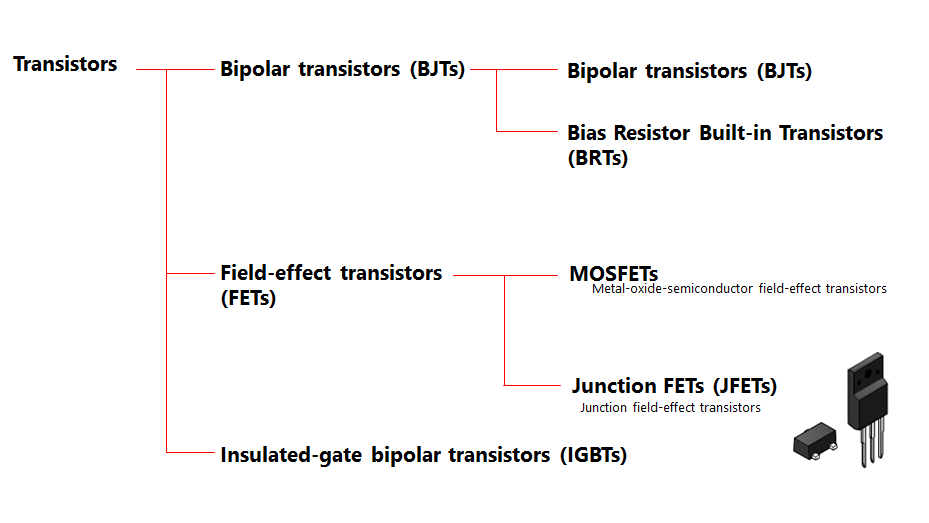

晶體管

+關(guān)注

關(guān)注

77文章

9995瀏覽量

140958 -

PVD

+關(guān)注

關(guān)注

4文章

51瀏覽量

17329 -

應(yīng)用材料公司

+關(guān)注

關(guān)注

0文章

62瀏覽量

16990

發(fā)布評(píng)論請(qǐng)先 登錄

下一代高速芯片晶體管解制造問(wèn)題解決了!

薄膜晶體管技術(shù)架構(gòu)與主流工藝路線

選擇性沉積技術(shù)介紹

晶體管與場(chǎng)效應(yīng)管的區(qū)別 晶體管的封裝類(lèi)型及其特點(diǎn)

慶祝在華四十周年 應(yīng)用材料中國(guó)公司舉辦總部慶典儀式

CMOS晶體管的尺寸規(guī)則

NMOS晶體管和PMOS晶體管的區(qū)別

什么是單極型晶體管?它有哪些優(yōu)勢(shì)?

晶體管的主要材料有哪些

GaN晶體管和SiC晶體管有什么不同

GaN晶體管的基本結(jié)構(gòu)和性能優(yōu)勢(shì)

晶體管電流的關(guān)系有哪些類(lèi)型 晶體管的類(lèi)型

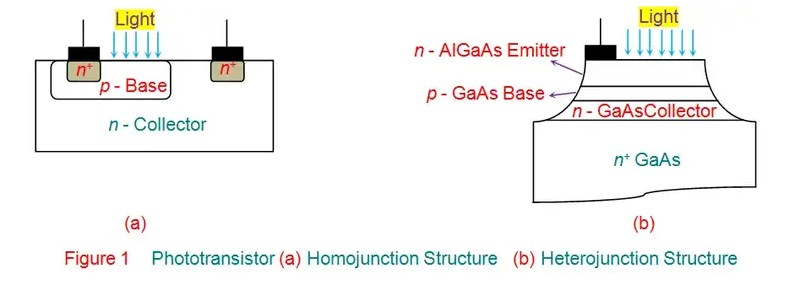

什么是光電晶體管?光電晶體管的工作原理和結(jié)構(gòu)

PNP晶體管符號(hào)和結(jié)構(gòu) 晶體管測(cè)試儀電路圖

應(yīng)用材料公司全新系統(tǒng)可改進(jìn)晶體管布線沉積工藝

應(yīng)用材料公司全新系統(tǒng)可改進(jìn)晶體管布線沉積工藝

評(píng)論