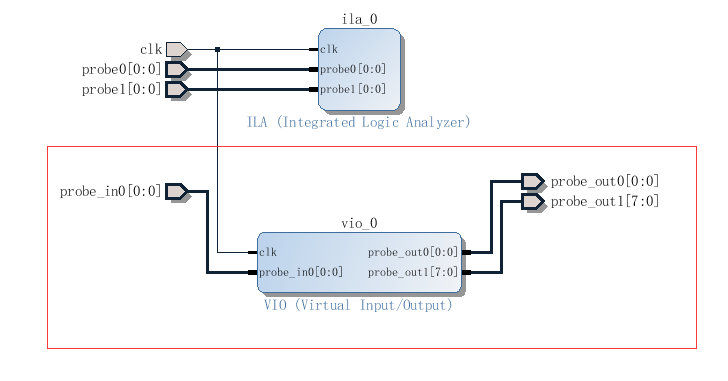

一般情況下ILA和VIO都是用在chipscope上使用,VIO可以作為在chipscope時模擬IO。

譬如:

在使用chipscope時需要使用按鍵出發,但是沒有設計按鍵或者板子不再身邊,所以需要模擬按鍵輸入還有其他信號的輸出。

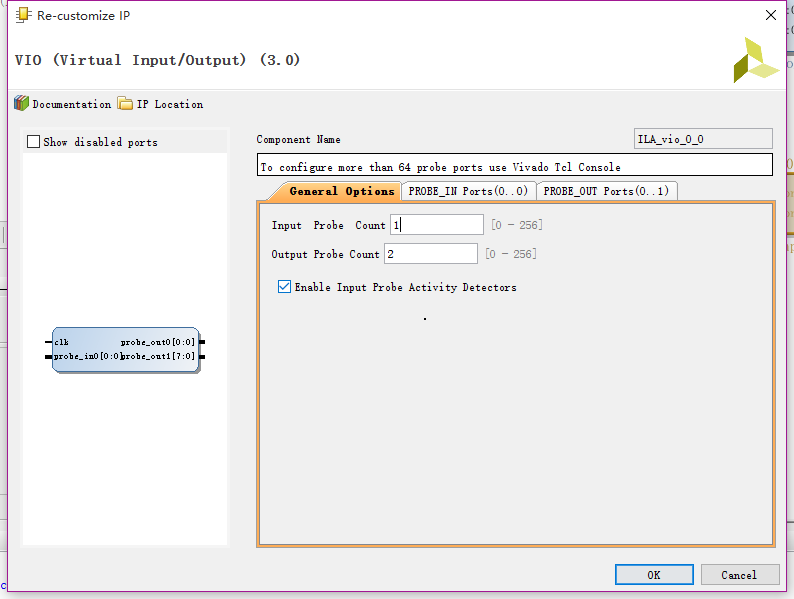

參數配置,配置輸入探針數量和輸出探針數量。分別可以設置0-256個。

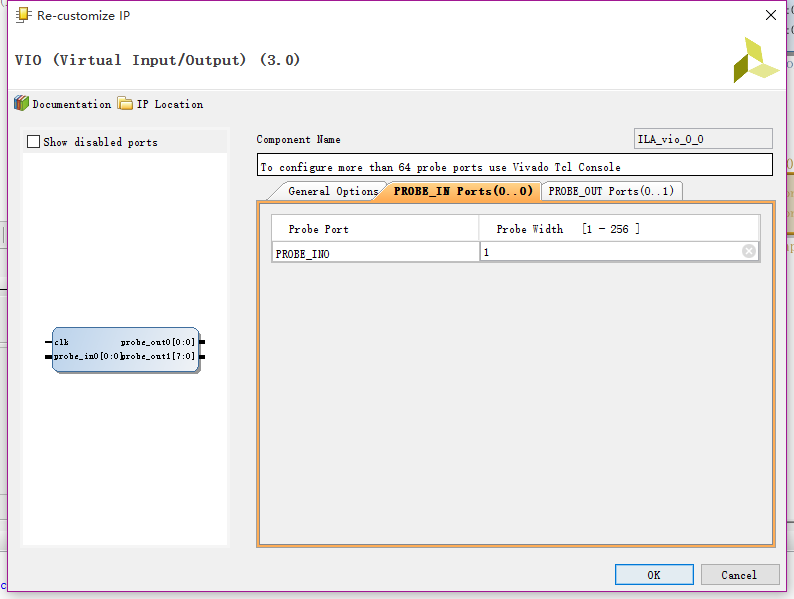

probe in ports參數配置,配置數據探針位寬

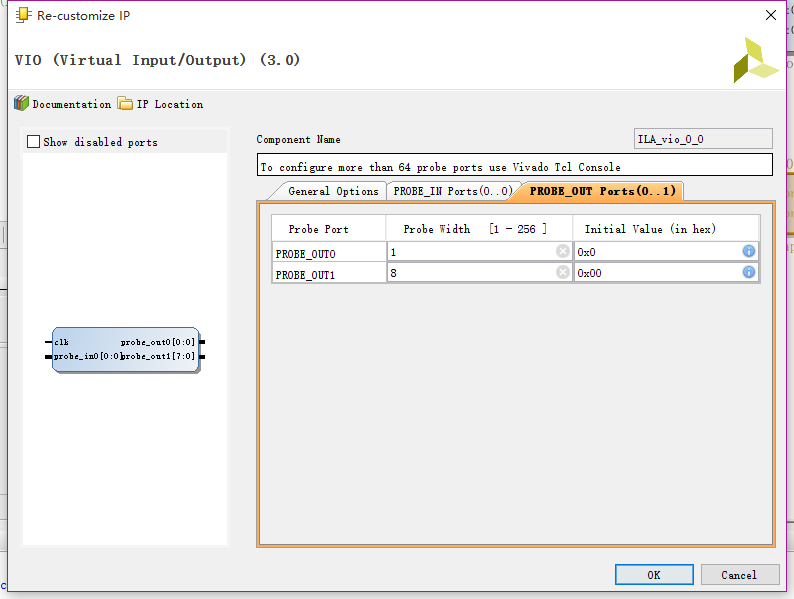

probe out port:參數配置輸出探針的數據位寬,及初始化數據(in hex)

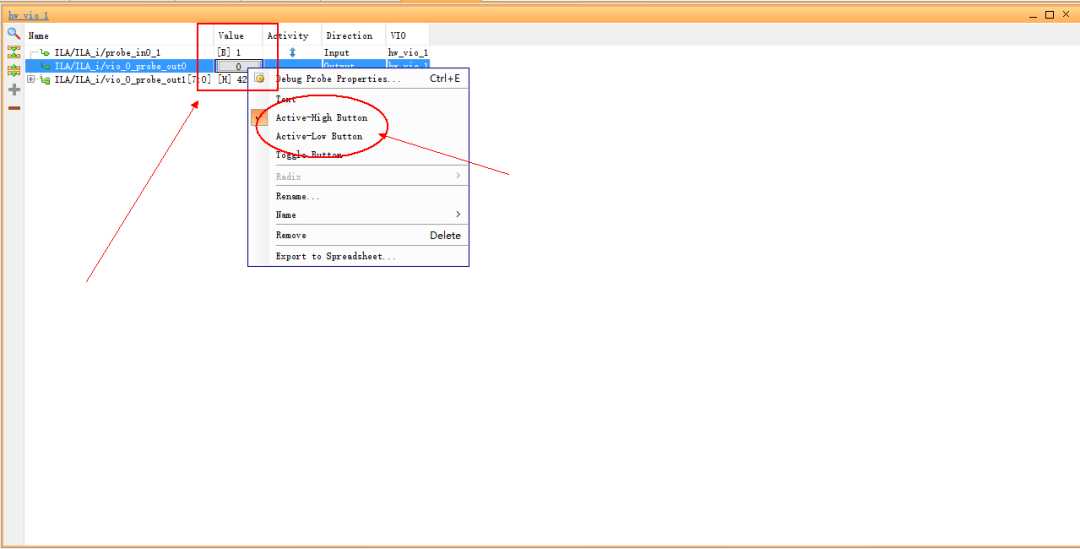

在hw_vio界面加入配置的輸入及輸出探針,并且對應的參數可以設置.

1、模擬的按鍵IO,可以設置成active_high buttom.

2、對于輸出參數,可以設置成text

對于里面設置的值,就是觸發后信號保持的狀態數據

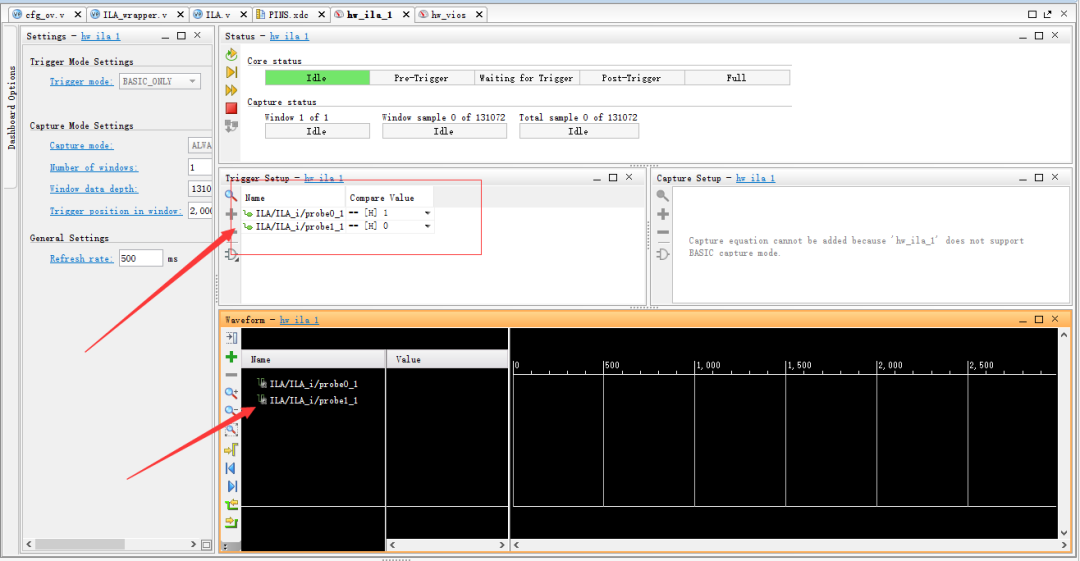

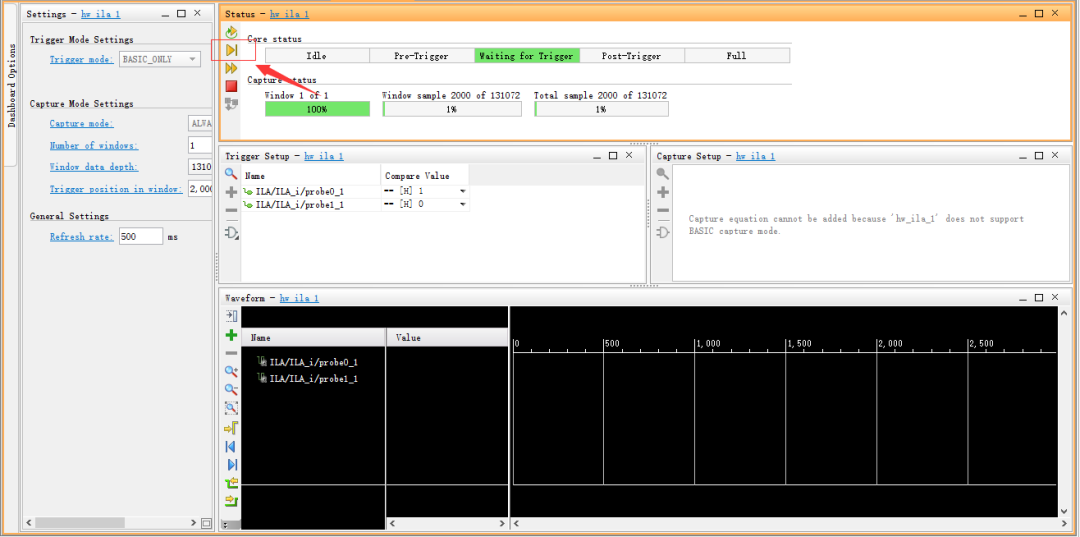

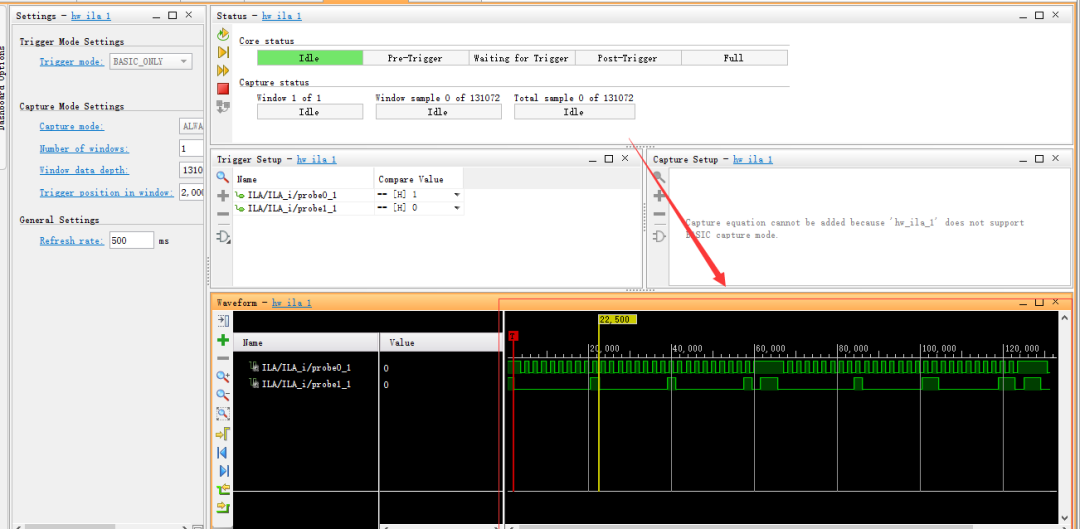

在hw_ILA界面,將ila的信號探針數據加入Trigger setup和waveform中。只要在

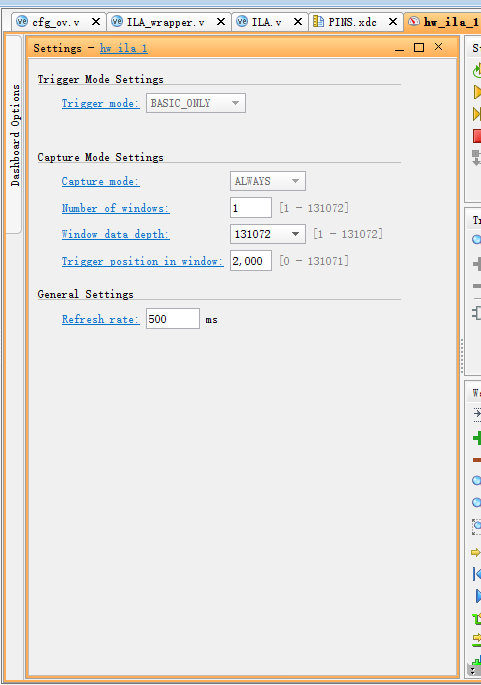

number of windows:指采樣窗口個數。

window data depth:采樣深度,要考慮能完整采樣一幀數據以上,圖上采樣深度是128K = 131072 / 1024

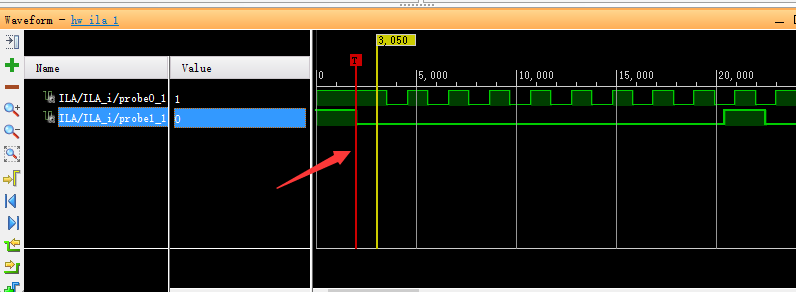

trigger position in window:窗口出發位置就是指紅色那根T線。設置一個參數為的是能正常等待出發。如果設置這個值為0,那么就不需要任何觸發按鍵或者觸發源來觸發。所以需要設定一個值

按啟動運行按鈕,讓ila處于waiting for trigger模式,等待出發,然后再hw_vios上觸發模擬復位按鈕,

就會出發對應的信號。

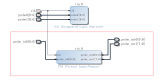

代碼實例化如圖所示。

ILA_wrapper ILA(

.clk ( ),

.probe0 ( ),

.probe1 ( ),

.probe_out0 ( ),

.probe_out1 ( ),

.probe_in0 ( )

)

-

VIO

+關注

關注

0文章

11瀏覽量

10343 -

Chipscope

+關注

關注

0文章

16瀏覽量

12187 -

模擬io

+關注

關注

0文章

5瀏覽量

2485

原文標題:vivado VIO (virtual input output)虛擬IO使用

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

XILINX FPGA Debug with VIO and TCL

求問為什么在使用chipscope的時候時鐘連不上?

使用VIO IP在ISE Design SUite軟件中調試時遇到以下錯誤該怎么辦?

AD7982的VREF與VDD/VIO之間是否有時序要求?

Chipscope學習教程

Xilinx FPGA ChipScope的ICON/ILA/VIO核使用

SDK和ChipScope配合工作

VIO比chipscope有多大優勢?

Vivado之VIO原理及應用

VIO在chipscope上的使用

VIO在chipscope上的使用

評論