成為市場領先產(chǎn)品的新系統(tǒng)設計是創(chuàng)新的結果,不僅是進化和革命性的,而且是優(yōu)雅、易于使用和高質量的系統(tǒng)設計。市場調查、統(tǒng)計數(shù)據(jù)和客戶小組都有精確的進化設計概念的跟蹤記錄;然而,革命性的概念更加難以捉摸,因為進化的客戶傾向于以基于現(xiàn)有事物的線性方式思考。革命性的概念通常來自能夠看得更遠的企業(yè)家或能夠設想更好的前進方向的一小部分客戶。

根據(jù)全球數(shù)百個設計項目的實踐經(jīng)驗,我得出的結論是,革命性和進化性產(chǎn)品都需要強大的系統(tǒng)工程努力。與具有明確定義和嚴格設計工作流程的產(chǎn)品開發(fā)和制造不同,電子和嵌入式實時軟件的系統(tǒng)設計仍處于起步階段。

許多懸而未決的問題已經(jīng)產(chǎn)生了大量的方法和工具來配合這些方法。系統(tǒng)設計師應該使用自上而下還是自下而上的設計風格?集中式或分布式處理方法是最佳方法嗎?是否需要對稱或非對稱拓撲?動力或速度是駕駛標準嗎?這些問題的答案,以及更多,可以導致一個概念框圖,開始設計過程,導致設計規(guī)范。

許多計算機科學家認為,內存帶寬是限制當今處理器性能的主要問題之一,尤其是隨著多核處理器芯片和多執(zhí)行單元 CPU 的發(fā)展。處理器內核和指令流水線經(jīng)常停止等待指令或數(shù)據(jù)緩存訪問。程序員認為,最小化程序變量將減少內存訪問并提高性能,而芯片設計人員通過使用 I1、D1、L2、L3、SDRAM 和磁盤內存結構向處理器內核添加更多內存通道來不斷提高內存帶寬。在許多方面,這是基于原始馮諾依曼計算機架構的線性思維。

可以考慮在兩個處理器內核上運行單線程程序代碼,并在每個內核上使用寄存器。這將從緩存中讀取/寫入的變量數(shù)量減少到 16 個變量,或者緩存訪問減少 66.6%,這會消耗更多功率并需要更多周期。例如,每個內核都需要訪問其他處理器內核的寄存器集。此外,許多程序都有緊密的循環(huán)來處理應用程序關鍵信息,如果一個單線程程序在兩個內核上運行,那么每個內核是否可以同時處理這個應用程序關鍵循環(huán)的偶數(shù)/奇數(shù)流?循環(huán)外的順序單周期指令可以同時在不同的內核上執(zhí)行嗎?雖然這種方法可能存在許多與雙核相關的問題,

一種解決方案是系統(tǒng)級雙核與單核模型,假設每 1,010 條指令有 80% 的整數(shù)指令和 20% 的浮點指令,包括十個循環(huán),每個循環(huán)有 1,000 條指令。為了簡化分析,假設沒有先前的指令依賴;但是,這可以通過額外的一天的努力來添加。

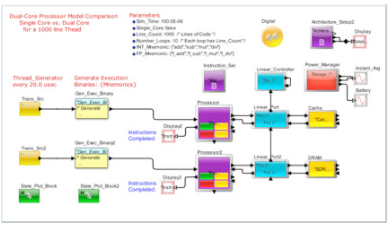

圖 1:雙核與單核模型。

該模型用于確定讓編譯器向雙核配置發(fā)出指令的有效性,并在性能和功耗方面利用每個內核上的額外寄存器。首先,添加兩個塊以根據(jù)執(zhí)行順序以助記指令數(shù)組的形式生成可執(zhí)行二進制文件。接下來,添加了兩個具有四級流水線的標準庫模塊,包括用于設置每條指令周期的通用指令集模塊。Power_Manager 添加了估計的功耗(以毫瓦為單位),基于待機、活動、等待和空閑電源狀態(tài)。

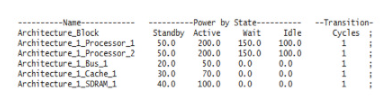

圖 2:電源管理器配置。

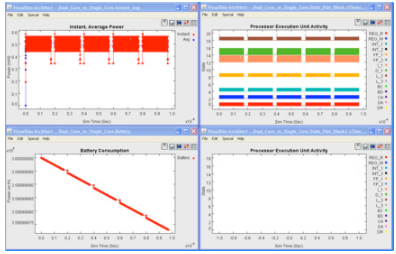

圖 3:單核模型圖。

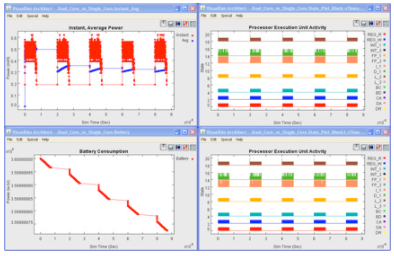

圖 4: ID 雙核模型圖。

雙核與單核模型為許多問題提供了答案,包括這種方法的理論性能/功率改進可能是什么?從結果來看,性能好于預期,即雙核配置需要6370個周期才能完成一個線程,而單核配置需要17160個周期才能完成一個線程。雙核配置完成線程的速度提高了 63%,而常識表明它完成線程的速度可能會提高 50%。在功耗方面,兩種配置大致相同。因此,系統(tǒng)級建模能夠生成結果,表明單線程的雙核指令同步執(zhí)行比相同功率級別的單核快 63%。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19899瀏覽量

235405 -

寄存器

+關注

關注

31文章

5435瀏覽量

124590 -

編譯器

+關注

關注

1文章

1662瀏覽量

50245

發(fā)布評論請先 登錄

雙核工業(yè)網(wǎng)關和單核工業(yè)網(wǎng)關差別大嗎

單核CPU網(wǎng)關和雙核CPU網(wǎng)關有什么區(qū)別

NVIDIA助力圖靈新訊美推出企業(yè)級多模態(tài)視覺大模型融合解決方案

淺談華為Green Core系統(tǒng)級智能網(wǎng)絡云節(jié)能解決方案

請問canmv-k230支持雙核嗎?如何調用另一個核心工作?

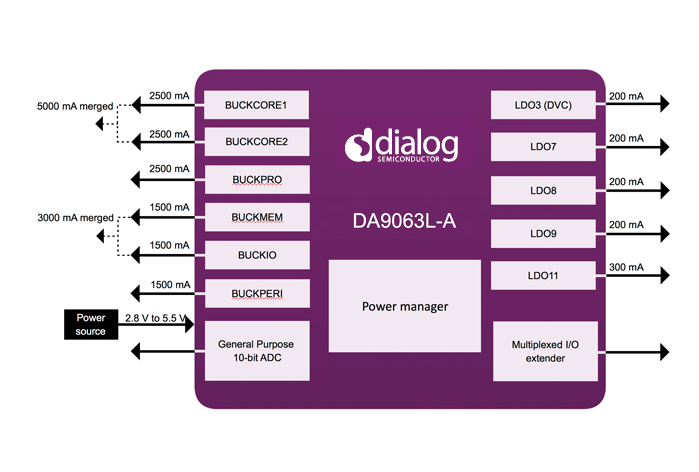

適用于單核、雙核和四核應用處理器的PMIC DA9063L-A數(shù)據(jù)手冊

系統(tǒng)級雙核與單核模型的解決方案

系統(tǒng)級雙核與單核模型的解決方案

評論