微控制器 (MCU) 和相關(guān)設(shè)備的技術(shù)趨勢是更小的幾何尺寸,因此需要更小的工作電壓。電路設(shè)計(jì)人員面臨著將低壓信號(hào)連接到各種其他設(shè)備電壓的挑戰(zhàn)。I2C 總線以其定義的協(xié)議和雙向信號(hào)流對(duì)這些工作提出了獨(dú)特的問題。集成電平轉(zhuǎn)換總線緩沖器應(yīng)用特定標(biāo)準(zhǔn)產(chǎn)品 (ASSP) 可以解決此問題,但也有其自身的障礙。

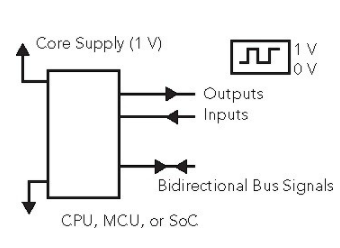

由于半導(dǎo)體制造技術(shù)的進(jìn)步,最新的嵌入式計(jì)算設(shè)備具有較低的電源電壓。這正在創(chuàng)造更小的晶體管幾何形狀,這反過來意味著更低的擊穿電壓。因此,信號(hào)擺幅現(xiàn)在比以前小得多,低至 1 V(圖 1)。

圖 1:縮小的晶體管幾何尺寸導(dǎo)致?lián)舸╇妷汉托盘?hào)擺幅比過去更低。

對(duì)于純數(shù)字信號(hào),有幾種可用的接口設(shè)備可以將較小的信號(hào)轉(zhuǎn)換為 CPU 輸出端口的較高擺幅。同樣,這些相同的器件可用于將現(xiàn)有信號(hào)降壓為更小、更安全的輸入,用于新的低壓內(nèi)核。例如,電壓電平轉(zhuǎn)換器 (VLT) 可以解決信號(hào)工作電壓的任何不匹配問題,但雙向 VLT 的設(shè)計(jì)卻很棘手。特定應(yīng)用標(biāo)準(zhǔn)產(chǎn)品 (ASSP) 解決了這個(gè)問題。

I2C 總線基礎(chǔ)知識(shí)

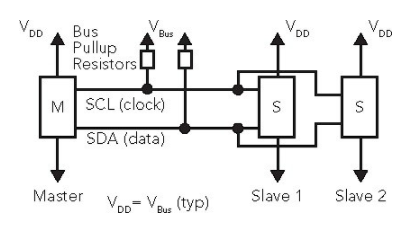

I2C 總線依靠兩個(gè)電氣連接和兩個(gè)外部電阻器來實(shí)現(xiàn)完整的雙向信號(hào)傳輸。該協(xié)議是全面的,允許多個(gè)節(jié)點(diǎn)同時(shí)充當(dāng)發(fā)送器和接收器,同時(shí)由于簡單可靠的多主機(jī)仲裁而避免總線沖突。

I2C 總線上的數(shù)據(jù)流由主機(jī)控制,主機(jī)提供稱為串行時(shí)鐘 (SCL) 的時(shí)鐘信號(hào)。數(shù)據(jù)沿稱為串行數(shù)據(jù) (SDA) 的第二個(gè)電氣連接傳遞,并且 SDA 上的數(shù)據(jù)可能從主機(jī)流向從機(jī),或以另一個(gè)方向流動(dòng)。

I2C 總線的一個(gè)獨(dú)特特性是節(jié)點(diǎn)的線或邏輯連接。當(dāng)總線空閑時(shí),沒有節(jié)點(diǎn)消耗電流,總線信號(hào)被上拉電阻保持在邏輯 1(通常為 +5 V),SCL 和 SDA 各一個(gè)。信號(hào)由一個(gè)節(jié)點(diǎn)通過一個(gè)漏極開路驅(qū)動(dòng)器拉低這些線路來斷言(盡管基于雙極技術(shù)的舊設(shè)備使用開路集電極設(shè)備來實(shí)現(xiàn)相同的結(jié)果)。主機(jī)發(fā)起每個(gè)數(shù)據(jù)事務(wù),響應(yīng)節(jié)點(diǎn)將 SDA 線拉低(響應(yīng)設(shè)備也可能將 SCL 線拉低,但這種稱為“時(shí)鐘拉伸”的模式很少使用)。

雙向電壓電平轉(zhuǎn)換器 (VLT)

I2C 總線協(xié)議中沒有硬件流控制,這使得 VLT 協(xié)議不可知,但也帶來了電路設(shè)計(jì)挑戰(zhàn)(圖 2)。

圖 2: I2C 總線協(xié)議中不存在硬件流控制,這給電路設(shè)計(jì)帶來了挑戰(zhàn)。

I2C 總線上的數(shù)據(jù)流向變化經(jīng)常發(fā)生,實(shí)際上是在每八個(gè)時(shí)鐘周期或傳輸一個(gè)字節(jié)數(shù)據(jù)之后。第 9 個(gè)時(shí)鐘周期讀取從設(shè)備以確認(rèn)發(fā)送的數(shù)據(jù)已被理解。在第 9 個(gè)時(shí)鐘周期期間,主機(jī)在 SDA 線上查找邏輯 0 確認(rèn)(稱為“ACK”)或邏輯 1 未確認(rèn)(稱為“NACK”)。VLT 負(fù)責(zé)可靠地來回傳遞這些信號(hào)。

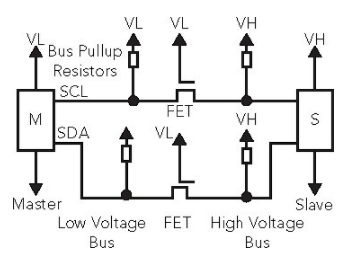

在第一代 VLT 設(shè)計(jì)中,典型的電壓階躍是從高側(cè)的 5 V 到低側(cè)的 3.3 V(通常是采用新技術(shù)的一側(cè))。一種常見的低成本轉(zhuǎn)換解決方案是單個(gè)場效應(yīng)晶體管 (FET) 器件(圖 3)。

圖 3:使用場效應(yīng)晶體管 (FET) 和無源電壓電平轉(zhuǎn)換器 (VLT) 是一種常見的、成本相對(duì)較低的電壓步進(jìn)解決方案,盡管它存在局限性。

限制蔓延到這個(gè)拓?fù)渲小km然單個(gè) FET 可以在兩個(gè)方向上傳遞信號(hào),但使用適當(dāng)?shù)?VLT 就沒有隔離。一側(cè)的負(fù)載必須由另一側(cè)進(jìn)行,從而限制了他們的吸引力。更糟糕的是,現(xiàn)有的低成本 FET 不太適合這些較低的總線電壓。想象一下在 DDR4 RDIMM 設(shè)計(jì)(2.5 V 部件)中看到的將 CPU 內(nèi)核(1 V 信號(hào))連接到控制器所需的 1 V 至 2.5 V 接口的情況。具有較低柵極閾值的 FET 是必要且可用的(價(jià)格合理),但 I2C 總線緩沖器 ASSP 也可以解決這些較低總線電壓的設(shè)計(jì)。I2C 總線緩沖器 ASSP 是基于 FET 的 VLT 的卓越解決方案。

I2C 總線緩沖器專用標(biāo)準(zhǔn)產(chǎn)品 (ASSP)

支持 I2C 擴(kuò)展的 ASSP 已經(jīng)存在了一段時(shí)間,更新的設(shè)計(jì)在一個(gè)令人印象深刻的范圍內(nèi)解決了 VLT,包括僅在 1 V 電源上運(yùn)行的下一代 CPU 和片上系統(tǒng) (SoC)。因?yàn)?ASSP 設(shè)備是緩沖器,所以它們分別加載到 I2C 總線緩沖器的每一側(cè)。這對(duì)于不增加 CPU 或 SoC 的 I/O 引腳的負(fù)擔(dān)很重要,并且允許在緩沖設(shè)備的另一側(cè)連接更多節(jié)點(diǎn);例如,新的智能手機(jī)和個(gè)人電子架構(gòu)具有更多連接到 I2C 總線的傳感器(節(jié)點(diǎn))。

向設(shè)計(jì)中添加任何總線緩沖器時(shí)需要小心,因?yàn)檫@些設(shè)備必須操縱總線電壓電平以避免致命的總線鎖定情況。簡單地說,I2C 總線緩沖器必須確定“A”側(cè)的低電平是來自其自己的輸出(即,“B”側(cè)的緩沖低電平)還是“A”側(cè)總線上的另一個(gè)外部設(shè)備。

總線緩沖器設(shè)計(jì)使用改變總線緩沖器輸出電壓的少數(shù)技術(shù)之一。在一種這樣的方法中,添加了一個(gè)小偏移電壓,該偏移電壓足夠小,不會(huì)干擾總線上的其他設(shè)備,但足以讓總線緩沖器知道來自總線上另一個(gè)節(jié)點(diǎn)的外部(和低得多)信號(hào)之間的差異,以及它自己的邏輯0信號(hào)。典型的靜態(tài)偏移僅為 90 mV。

總線速度改進(jìn)

雖然早期的 I2C 總線以適中的速度移動(dòng)(時(shí)鐘頻率為 100 kHz 或更低)并服務(wù)于當(dāng)時(shí)的應(yīng)用程序,但較新的應(yīng)用程序需要更多的數(shù)據(jù)吞吐量,因此需要更快的時(shí)鐘。當(dāng)前的 I2C 規(guī)范定義了信號(hào)的時(shí)序,增加了幾個(gè)高達(dá)1 MHz的新時(shí)鐘速度。這些時(shí)鐘速度被稱為“Fm+”(快速模式加),比以前的 Fm(快速模式)速度提高了 250%,后者將時(shí)鐘限制為 400 kHz。

請(qǐng)記住,決定總線時(shí)鐘速度的是總線主控器(通常是已內(nèi)置于 MCU、CPU 或 SoC 設(shè)備中的功能)的操作。從設(shè)備和總線緩沖器不產(chǎn)生時(shí)鐘,也不關(guān)心時(shí)鐘精度;一個(gè) 800 kHz 的總線時(shí)鐘實(shí)際上可能以 20% 的容差運(yùn)行。為了提高速度,必須降低總線負(fù)載(電容)。總線緩沖器分離總線并隔離每個(gè)段的電容。

提高時(shí)鐘頻率并非沒有硬件挑戰(zhàn)。無法控制的更快時(shí)鐘和數(shù)據(jù)轉(zhuǎn)換可能會(huì)導(dǎo)致振鈴和下沖,因?yàn)?I2C 總線不是傳輸線,并且沒有足夠小的終端電阻來抑制快速信號(hào)邊沿。I2C 規(guī)范限制了邊沿的上升時(shí)間和下降時(shí)間。總線段的上升時(shí)間由系統(tǒng)負(fù)載電容設(shè)置,該電容是節(jié)點(diǎn)和互連信號(hào)走線電容的總和。板級(jí)電路設(shè)計(jì)人員只能自由選擇 I2C 總線信號(hào)上拉電阻。

當(dāng) I2C 總線由現(xiàn)代高性能數(shù)字設(shè)備(CPU、MCU 和 SoC 類型)驅(qū)動(dòng)時(shí),需要注意減慢這些快如閃電的設(shè)備生成的時(shí)鐘和數(shù)據(jù)總線信號(hào)的下降沿。如有必要,應(yīng)添加一個(gè)外部串聯(lián)電阻與雜散電容一起工作,以創(chuàng)建受控的下降時(shí)間并抑制 I2C 總線段上的任何振鈴。或者,這可以通過添加一個(gè)小電容器來實(shí)現(xiàn)。

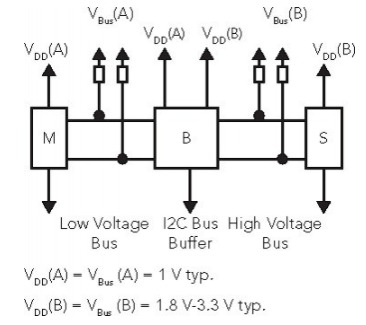

如果設(shè)計(jì)需要更高的數(shù)據(jù)吞吐量和在較低電源電壓下運(yùn)行的更新技術(shù)組件,則希望在您的設(shè)計(jì)中添加一個(gè) I2C 總線緩沖器(圖 4)。將 I2C 總線緩沖器的兩側(cè)視為單獨(dú)的總線,并選擇適合的上拉電阻。

圖 4:需要更高數(shù)據(jù)吞吐量和更新技術(shù)組件的設(shè)計(jì)可能需要集成 I2C 總線緩沖器電壓電平轉(zhuǎn)換器 (VLT)。此處顯示的是 NXP Semiconductors 的 PCA9617A 總線緩沖器,具有 Fm+ 速度和低至 1 V 的 VLT。

審核編輯:郭婷

-

微控制器

+關(guān)注

關(guān)注

48文章

7926瀏覽量

153887 -

mcu

+關(guān)注

關(guān)注

146文章

17893瀏覽量

361899 -

總線

+關(guān)注

關(guān)注

10文章

2956瀏覽量

89471

發(fā)布評(píng)論請(qǐng)先 登錄

PCA9306 I2C緩沖器評(píng)估模塊

實(shí)現(xiàn)下一代具有電壓電平轉(zhuǎn)換功能的處理器、FPGA 和ASSP

解決I2C緩沖器上的靜態(tài)電壓失調(diào)部署不當(dāng)問題

TCA9517-Q1電平轉(zhuǎn)換I2C總線中繼器數(shù)據(jù)表

TCA9803電平轉(zhuǎn)換I2C總線緩沖器/中繼器數(shù)據(jù)表

TCA9511A熱插拔I2C總線和SMBus緩沖器數(shù)據(jù)表

TCA9800電平轉(zhuǎn)換I2C總線緩沖器/中繼器數(shù)據(jù)表

TCA9802電平轉(zhuǎn)換I2C總線緩沖器/中繼器數(shù)據(jù)表

TCA9801電平轉(zhuǎn)換I2C總線緩沖器/中繼器數(shù)據(jù)表

TCA9517電平轉(zhuǎn)換I2C總線中繼器數(shù)據(jù)表

TCA4311熱插拔I2C總線緩沖器數(shù)據(jù)表

PCA9517電平轉(zhuǎn)換I2C總線中繼器數(shù)據(jù)表

具有阻塞總線恢復(fù)功能的TCA4307熱插拔 I2C 總線和 SMBus緩沖器數(shù)據(jù)表

P82B96 I2C兼容雙向總線緩沖器數(shù)據(jù)表

TCA39306雙向I2C總線和SMBus電壓電平轉(zhuǎn)換器數(shù)據(jù)表

I2C總線緩沖器ASSP可處理寬電壓電平轉(zhuǎn)換范圍

I2C總線緩沖器ASSP可處理寬電壓電平轉(zhuǎn)換范圍

評(píng)論