另一組片上系統(tǒng)驗(yàn)證方法依賴于使用經(jīng)過驗(yàn)證的硅片、新的和未經(jīng)測(cè)試(可能尚不可用)硅片的虛擬原型以及 FPGA 原型在硬件上執(zhí)行實(shí)際軟件。正如我們從這個(gè)角度看到的那樣,有時(shí)會(huì)使用所有三種方法。

據(jù)最佳估計(jì),90 nm 芯片設(shè)計(jì)背后的軟件開發(fā)工作已經(jīng)超過了硬件開發(fā)工作。對(duì) 2011 年的預(yù)測(cè)是,不到 40% 的整體芯片開發(fā)成本將用于硬件。軟件現(xiàn)在主導(dǎo)著項(xiàng)目周期,并決定了芯片何時(shí)可以投入批量生產(chǎn)。結(jié)果,軟件驗(yàn)證的重要性增加了,軟件在硬件驗(yàn)證過程中扮演了不可或缺的角色。

將硬件和軟件結(jié)合在一起

今天,工程師使用三種基本技術(shù)在硬件表示上執(zhí)行軟件。在衍生設(shè)計(jì)中,部分軟件可以使用上一代芯片進(jìn)行開發(fā)。這種方法通常最適用于分層軟件架構(gòu)中較高的軟件部分,特別是對(duì)于獨(dú)立于硬件的應(yīng)用程序。

虛擬原型提供了設(shè)計(jì)周期中最早的解決方案,因?yàn)樗鼈兛梢栽诩軜?gòu)確定后立即實(shí)施。這些原型是片上系統(tǒng) (SoC)、電路板、I/O 和用戶界面的預(yù)寄存器傳輸級(jí)別 (RTL)、寄存器精確和功能齊全的軟件模型。它們執(zhí)行未經(jīng)修改的生產(chǎn)代碼,并使用 USB 等外部接口作為虛擬 I/O 近乎實(shí)時(shí)地運(yùn)行。

因?yàn)樘摂M原型本質(zhì)上是軟件,所以它們提供了高度的系統(tǒng)可見性和控制,包括多核調(diào)試。它們還可以作為半導(dǎo)體和系統(tǒng)制造商之間協(xié)作的工具。自 Open SystemC Initiative Transaction Level Model (TLM) 2.0 API 標(biāo)準(zhǔn)化以來,SystemC 已成為使用可互操作的事務(wù)級(jí)模型開發(fā)快速虛擬原型的合適基礎(chǔ)設(shè)施。

在 RTL 完成并使用功能驗(yàn)證技術(shù)達(dá)到穩(wěn)定狀態(tài)后,可以使用 FPGA 原型。原型是 SoC、電路板和 I/O 實(shí)現(xiàn)未修改的 ASIC RTL 代碼的硅前、功能齊全的硬件表示。經(jīng)過優(yōu)化實(shí)施,它們可以在連接外部接口和激勵(lì)的情況下幾乎實(shí)時(shí)運(yùn)行,并結(jié)合 RTL 仿真提供比實(shí)際芯片更高的系統(tǒng)可見性和控制。與傳統(tǒng)的硬件/軟件覆蓋相比,F(xiàn)PGA 原型提供了更高的速度水平,后者將 RTL 仿真與周期精確的處理器模型相結(jié)合。

根據(jù)所需的準(zhǔn)確性、速度和所需的可用時(shí)間,不同的技術(shù)為軟件開發(fā)和軟件驅(qū)動(dòng)的硬件驗(yàn)證提供最合適的解決方案。混合產(chǎn)品通常允許設(shè)計(jì)人員利用多種產(chǎn)品的優(yōu)勢(shì)。例如,可以通過處理器和外圍設(shè)備的快速事務(wù)級(jí)模型來增強(qiáng) RTL 仿真,以提高仿真速度和驗(yàn)證覆蓋率。或者,在混合使用模式下處理設(shè)計(jì)問題的虛擬原型和 FPGA 原型結(jié)合了基于軟件和硬件的執(zhí)行,提供了比單獨(dú)產(chǎn)品更好的解決方案。

從實(shí)際項(xiàng)目中學(xué)習(xí)

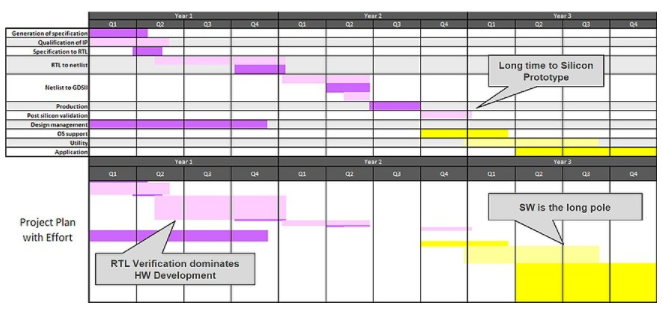

為了更好地理解這個(gè)問題,Synopsys 和 International Business Strategies 分析了包括復(fù)雜硬件和軟件在內(nèi)的 12 個(gè)項(xiàng)目的項(xiàng)目工作量和經(jīng)過的時(shí)間。圖 1 顯示了分析的 12 個(gè)項(xiàng)目的示例。上半部分顯示了不同開發(fā)階段的時(shí)間線;底部顯示了每個(gè)階段的總體項(xiàng)目工作量的百分比。

圖 1:在對(duì) 12 個(gè)項(xiàng)目的分析中,RTL 驗(yàn)證占用了 21% 的硬件/軟件開發(fā)工作量。

RTL 驗(yàn)證平均占整體硬件/軟件工作量的 21%,或僅硬件工作量的 38%。此外,RTL 驗(yàn)證消耗了從需求到 GDSII 所用時(shí)間的大約 55%。驗(yàn)證在流片的整個(gè)流程中以不同的變體繼續(xù)進(jìn)行,而且在 IP 認(rèn)證上花費(fèi)的大部分精力也可以被認(rèn)為是另一種形式的驗(yàn)證。因此,驗(yàn)證很容易達(dá)到硬件開發(fā)中經(jīng)常提到的 70% 的數(shù)字。

從硬件從規(guī)范到流片的開發(fā)時(shí)間來看,移植操作系統(tǒng)平均需要大約三分之一的時(shí)間,開發(fā)實(shí)用軟件大約需要一半時(shí)間,三分之二的時(shí)間用于移植操作系統(tǒng)。開發(fā)應(yīng)用軟件。在工程樣品可用時(shí)開始軟件開發(fā)的全系列開發(fā)過程將使項(xiàng)目進(jìn)度再增加半年到四分之三的時(shí)間。除非項(xiàng)目是并行開發(fā)的,否則軟件開發(fā)會(huì)延遲大量交付硬件的能力。

雖然在項(xiàng)目開始后從需求到流片有 17% 的時(shí)間可以使用穩(wěn)定的規(guī)范(虛擬原型的先決條件),但從需求到流片需要將近 70% 的時(shí)間才能達(dá)到穩(wěn)定的 RTL(先決條件)用于硬件原型。虛擬和硬件原型在非常不同的時(shí)間可用,因此適用于非常不同的開發(fā)階段。

提高驗(yàn)證效率

如果在 SoC 設(shè)計(jì)周期的早期提供虛擬原型用于軟件開發(fā),它可以不斷發(fā)展以滿足不同的需求。軟件驅(qū)動(dòng)驗(yàn)證的三種主要使用模型在 RTL 中利用虛擬原型與信號(hào)級(jí)仿真的集成:

1. 當(dāng)一個(gè) RTL 塊可用時(shí),它可以在虛擬原型中替換它的 TLM。然后可以在此版本的原型上驗(yàn)證軟件,作為驗(yàn)證硬件和軟件的一種方式。知道使用了真實(shí)的系統(tǒng)場(chǎng)景會(huì)增加驗(yàn)證的信心。此外,鑒于盡可能多的系統(tǒng)在事務(wù)級(jí)別進(jìn)行模擬,驗(yàn)證的模擬速度更快。

2. 虛擬原型還可以作為運(yùn)行實(shí)際系統(tǒng)軟件的測(cè)試臺(tái)組件,為 RTL 驗(yàn)證測(cè)試臺(tái)開發(fā)和硅后驗(yàn)證測(cè)試提供先機(jī)。虛擬原型可用于生成系統(tǒng)激勵(lì)來測(cè)試 RTL,然后驗(yàn)證虛擬原型和 RTL 功能是否相同。用戶可以在TLM嵌入式定向軟件測(cè)試上進(jìn)行高效開發(fā),也可以用于系統(tǒng)集成測(cè)試。結(jié)果,驗(yàn)證測(cè)試用例開發(fā)的生產(chǎn)力提高了。

3. 由于虛擬原型的某些部分被驗(yàn)證為等同于它們相應(yīng)的 RTL,虛擬原型可以成為參考可執(zhí)行規(guī)范。因此,用戶獲得了針對(duì)事務(wù)級(jí)別和 RTL 的單一黃金測(cè)試平臺(tái)。

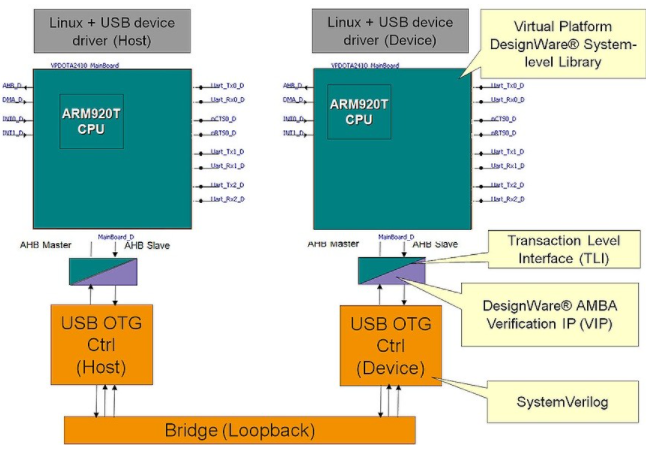

圖 2 顯示了 Synopsys Innovator 虛擬原型開發(fā)環(huán)境中的 USB On-The-Go 示例和分別使用事務(wù)級(jí)處理器模型和嵌入式軟件的 USB 驗(yàn)證環(huán)境。

圖 2:在 USB 驗(yàn)證環(huán)境中,事務(wù)級(jí)處理器模型通過 USB 連接到 RTL。

即使在項(xiàng)目開始時(shí)沒有虛擬原型,硬件組件的虛擬化也可以幫助從 RTL 驗(yàn)證環(huán)境開始逐步提高驗(yàn)證效率。

在事務(wù)級(jí)別用虛擬處理器模型替換系統(tǒng)中片上處理器的 RTL 表示可以顯著提高仿真速度,從而縮短驗(yàn)證周轉(zhuǎn)時(shí)間。在幾個(gè)客戶示例中,更換單個(gè)處理器模型將仿真速度提高了 32 倍。

為了在功能 RTL 驗(yàn)證中加入軟件驅(qū)動(dòng)程序以執(zhí)行實(shí)際產(chǎn)品測(cè)試用例,只需對(duì)適當(dāng)?shù)淖酉到y(tǒng)進(jìn)行建模并將其連接到 RTL 仿真。這可以像從庫(kù)中添加事務(wù)級(jí)處理器模型一樣簡(jiǎn)單,通過簡(jiǎn)單的總線模型將其連接到正在驗(yàn)證的外設(shè)的 TLM,然后將其連接到 RTL,如圖 2 所示。

混合原型

為了通過提高仿真速度和系統(tǒng)中嵌入式軟件的執(zhí)行來進(jìn)一步提高驗(yàn)證效率,可以使用硬件原型。鑒于虛擬原型和硬件原型在項(xiàng)目的根本不同階段都可用,混合原型提供了一個(gè)可行的解決方案,讓開發(fā)人員可以利用這兩個(gè)世界的優(yōu)勢(shì)。

雖然虛擬原型在設(shè)計(jì)流程的早期就可用——通常僅在規(guī)范穩(wěn)定后幾周——它們通常并不代表 FPGA 原型可以展示的完整實(shí)現(xiàn)細(xì)節(jié)。相比之下,F(xiàn)PGA 原型在相當(dāng)高的速度下運(yùn)行完全準(zhǔn)確,但在設(shè)計(jì)流程的后期可用,盡管在硅片從生產(chǎn)中返回之前還很長(zhǎng)時(shí)間。

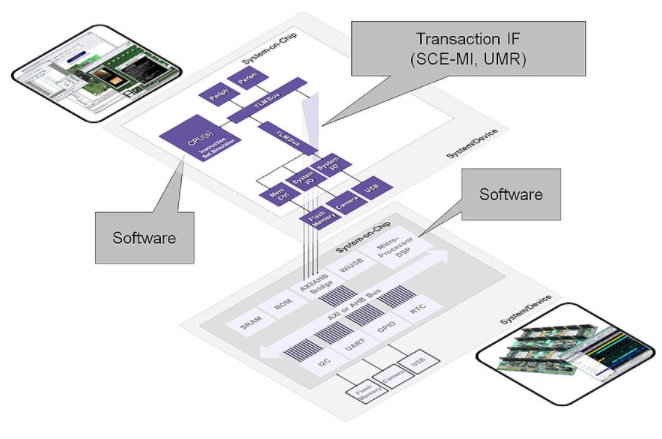

圖 3 顯示了混合 TLM 和硬件原型的原理圖。幾種混合使用模型結(jié)合了虛擬原型和 FPGA 原型的優(yōu)點(diǎn),包括重用實(shí)際 RTL 而不是重新建模和加速硬件和軟件的整體執(zhí)行。

圖 3:虛擬原型和 FPGA 原型的混合使用模型結(jié)合了虛擬原型和 FPGA 原型的優(yōu)點(diǎn)。

未來更智能的驗(yàn)證

由于驗(yàn)證對(duì)項(xiàng)目工作和時(shí)間表以及軟件對(duì)項(xiàng)目成功的影響越來越大,考慮到嵌入式軟件的智能驗(yàn)證變得越來越重要。

使用虛擬原型,無論是自下而上的 RTL 驗(yàn)證,還是自上而下的虛擬原型驗(yàn)證,都可以逐步提高驗(yàn)證效率。通過使用處理器和外圍設(shè)備的虛擬化事務(wù)級(jí)模型增強(qiáng)傳統(tǒng) RTL 仿真,可以提高驗(yàn)證效率。這提高了仿真速度,并允許直接執(zhí)行 TLM 參考模型作為測(cè)試臺(tái)的一部分。在自上而下的流程中,可以通過重用現(xiàn)有的虛擬原型及其模型來提高驗(yàn)證效率,這可以通過簡(jiǎn)單地將正在驗(yàn)證的 RTL 替換為 TLM 直到 RTL 可用,從而為驗(yàn)證場(chǎng)景開發(fā)提供先機(jī)。虛擬原型隨后成為 RTL 驗(yàn)證的參考。

虛擬原型和 FPGA 原型的混合以及 RTL 仿真和事務(wù)級(jí)模型的混合允許開發(fā)人員利用各個(gè)解決方案的綜合優(yōu)勢(shì)。對(duì)驗(yàn)證效率的直接影響很大程度上源于更快的模擬執(zhí)行,這反過來又可以加快驗(yàn)證周轉(zhuǎn)速度。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19882瀏覽量

234932 -

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617888 -

嵌入式

+關(guān)注

關(guān)注

5149文章

19651瀏覽量

317148

發(fā)布評(píng)論請(qǐng)先 登錄

嵌入式軟件開發(fā)常用的軟件有哪些?

Linux嵌入式和單片機(jī)嵌入式的區(qū)別?

嵌入式開發(fā)入門指南:從零開始學(xué)習(xí)嵌入式

嵌入式軟件行業(yè)增長(zhǎng)驅(qū)動(dòng)因素

如何成為一名嵌入式軟件工程師?

嵌入式軟件單元測(cè)試的必要性、核心方法及工具深度解析

如何提高嵌入式代碼質(zhì)量?

為什么嵌入式驅(qū)動(dòng)開發(fā)工程師可以拿高薪?

嵌入式系統(tǒng)開發(fā)與硬件的關(guān)系 嵌入式系統(tǒng)開發(fā)常見問題解決

嵌入式學(xué)習(xí)建議

什么是嵌入式?一文讀懂嵌入式主板

嵌入式主板是什么意思?嵌入式主板全面解析

嵌入式linux開發(fā)的基本步驟有哪些?

嵌入式系統(tǒng)中的實(shí)時(shí)操作系統(tǒng)

嵌入式軟件開發(fā)與AI整合

嵌入式軟件驅(qū)動(dòng)的硬件驗(yàn)證

嵌入式軟件驅(qū)動(dòng)的硬件驗(yàn)證

評(píng)論