嵌入式 CPU 幾乎無處不在,因為它們提供了靈活性以及相當好的性能和低功耗,而且通常成本更低。與需要將單獨的微處理器或微控制器耦合到您的定制硬件的解決方案相比,切換到基于嵌入式 CPU 的設計是輕而易舉的事。但是任何類型的 CPU 都有限制。即使我們可以將我們的算法轉移到軟件中,算法的潛在復雜性是無限的。我們可以編寫程序并且它們會運行,但不一定在可接受的時間或合理的功率預算內。

這就是為什么微處理器制造商很快提出了硬件加速器的概念——硬件功能可以執行通常需要的任務,例如浮點運算,比在 CPU 上運行的軟件要快得多。這個想法很快就流行起來,其他加速器開始出現,對于密碼學、正則表達式處理和圖形功能只是幾個例子。

所有這些都非常有效,但犧牲了基于軟件的解決方案的一個重要優勢:因為實現大多是硬編碼的,所以很難修改。加速器可能允許通過寄存器控制進行一些有限級別的調整,但是如果您需要修復錯誤或更改算法,則必須重新設計硬件。響應現場故障和不斷變化的市場需求變得更加昂貴。

您真正想要的是兩全其美——一種在加速算法的同時仍然能夠在軟件中定義這些算法的方法。當然,所有可能算法的范圍是無限的,因此不可能對所有情況都有一個解決方案。但是對于大量非常常用的功能,DSP 正好可以提供這種解決方案。

考慮幾乎所有必須處理流數據的操作。在音頻處理中可以找到明顯的例子,從濾波到 PDM-PCM 轉換再到聲學回聲消除。或者考慮基于流的密碼,例如 SNOW 和 ZUC(用于 LTE)。在信號處理環境中,考慮基站和手機之間的信道估計。這旨在優化當前條件下的傳輸以獲得最大的可靠性,并且需要對接收到的信號進行復雜的矩陣計算。更一般地說,考慮任何可以從非常廣泛的并行性中受益的應用程序,例如 AES 加密。

流計算、復雜數學(矩陣、浮點)和/或高級并行性都是 DSP 大放異彩的領域,應該認真考慮作為硬件加速器的替代品。在許多情況下,實現也將小于硬編碼加速器,從而降低產品的單位成本。至于功耗,也許加速器會比 DSP 實現略低,但 DSP 功耗仍將遠低于基于 CPU 的同等產品。更好的是,如果這些加速不需要同時運行,您可以將多個加速功能整合到一個 DSP 上,從而消除對多個加速器的需求。為了獲得更大的處理能力,您可以使用多核 DSP,就像您可以使用多核 CPU 一樣。

最重要的是,DSP 實現是可編程的,用 C 語言編寫,就像您的 CPU 內核一樣。您需要做一些稍微不同的事情——例如優化并行性——但是一個好的 DSP 編譯器和建模模擬器應該會讓這相對容易。因此,您無需更改底層硬件即可獲得錯誤修復和產品升級的所有優勢。提高客戶滿意度并改善收入來源。不錯。

還有另一個優勢:作為處理器,它可以支持多種功能。考慮一下全球定位標準 GNSS,以及從基于 DSP 的計算中顯著受益的功能。這當然是移動設備中的一個很好的功能,但現在固定設備的 GNSS 也出現了繁榮,以簡化配置、更新和維護。如果您的設備已經啟用了 DSP,則 GNSS 可能是某些供應商的軟件插件,并且可以在其他功能處于休眠狀態時在安靜時期運行。如果您已經擁有基于硬件的 GNSS 或計劃添加一個,您可以節省空間和電力。

我并不是說 DSP 實現一定可以取代你所有的硬件加速器。某些加速器功能可能不適合 DSP 的優勢。有些可能適合某個范圍,但不能超出該范圍;例如,對于非常大的過濾器,您唯一的選擇可能仍然是硬連線實現。但這留下了許多功能,其中 DSP 在性能和功率上接近等效的硬件加速器,實際上可能在成本上更好,并且比硬件版本具有無限更多的靈活性。值得考慮。

本博客是系列文章中的第二篇,該系列以“為什么 DSP 突然無處不在”開始,并以第三篇博客結尾:“決策,決策:硬件加速器還是 DSP?”。

審核編輯 黃昊宇

-

dsp

+關注

關注

556文章

8148瀏覽量

355703 -

硬件加速器

+關注

關注

0文章

43瀏覽量

13004

發布評論請先 登錄

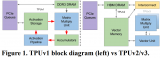

TPU處理器的特性和工作原理

小型加速器中子源監測系統解決方案

數據中心中的FPGA硬件加速器

磁調制式電流傳感器在粒子加速器中的應用

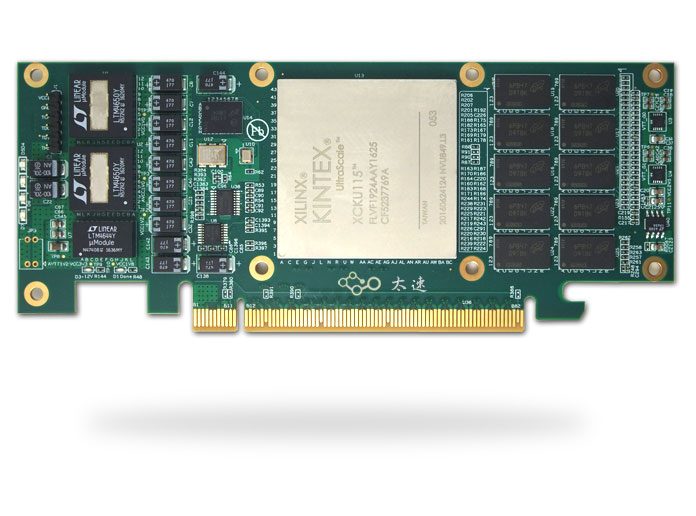

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡

AMD Alveo V80計算加速器網絡研討會

基于 DSP5509 進行數字圖像處理中 Sobel 算子邊緣檢測的硬件連接電路圖

適用于數據中心應用中的硬件加速器的直流/直流轉換器解決方案

圖形圖像硬件加速器卡設計原理圖:270-VC709E 基于FMC接口的Virtex7 XC7VX690T PCIeX8 接口卡

當 DSP 擊敗硬件加速器時

當 DSP 擊敗硬件加速器時

評論