通信、工業(yè)甚至嵌入式設(shè)計(jì)越來(lái)越需要更高性能的接口。諸如 DDR4 內(nèi)存、10 Gigabit 以太網(wǎng)、PCIe、串行 ADC 和 DAC 接口等協(xié)議正在變得司空見(jiàn)慣。雖然這些高速接口通常出現(xiàn)在高端 FPGA 上,但對(duì)于大多數(shù)應(yīng)用來(lái)說(shuō),這通常是一種過(guò)度殺傷的方法并且成本過(guò)高。使用低端 FPGA 也不是一種選擇,因?yàn)樗鼈儾荒芴峁┍匾男阅堋?/p>

現(xiàn)在,部署這些接口的成本可以通過(guò)使用新型節(jié)能、中等密度的 FPGA 顯著降低,這些 FPGA 經(jīng)過(guò)成本優(yōu)化,功耗更低,提供比更昂貴的 FPGA 更小的外形尺寸,同時(shí)仍然提供大量高- 速度接口選項(xiàng)。

應(yīng)對(duì)新的市場(chǎng)動(dòng)態(tài)

盡管各個(gè)細(xì)分市場(chǎng)是獨(dú)一無(wú)二的,但它們也有幾個(gè)共同點(diǎn)。對(duì)更高價(jià)值和更低成本的需求正在成為所有應(yīng)用和細(xì)分市場(chǎng)的增長(zhǎng)動(dòng)力。此外,隨著物聯(lián)網(wǎng) (IoT) 的出現(xiàn),速度更快、數(shù)量更多的網(wǎng)絡(luò)接口現(xiàn)在變得更加普遍。最后,大多數(shù)嵌入式設(shè)計(jì)中的高速處理是一種新規(guī)范。

這些因素要求架構(gòu)包含千兆以太網(wǎng)等接口,以及足夠快的收發(fā)器以支持 10 GbE、JESD204B ADC/DAC、PCIe 接口、HDMI 2.0b 和 DDR4 等內(nèi)存總線,僅舉幾例。

既然這些類型的接口可用于成本優(yōu)化、低功耗的中檔 FPGA,設(shè)計(jì)工程師就有了重要的新選擇來(lái)應(yīng)對(duì)其產(chǎn)品的最新市場(chǎng)動(dòng)態(tài)。其中最有價(jià)值的選項(xiàng)之一是能夠在 FPGA 的通用輸入輸出 (GPIO) 引腳上使用串行千兆位媒體獨(dú)立接口 (SGMII),而不必使用高速收發(fā)器。

在 GPIO 上利用 SGMII

在許多通信和工業(yè)設(shè)計(jì)中最常用的接口是千兆以太網(wǎng) (GbE)。最常見(jiàn)的是,F(xiàn)PGA 通過(guò)串行 SGMII 接口連接到 PHY。過(guò)去,使用 FPGA 實(shí)現(xiàn) SGMII 接口也需要使用高速收發(fā)器。這一切都隨著新的成本優(yōu)化的中檔 FPGA 的出現(xiàn)而改變,這使得 SGMII 接口可以在通用 GPIO 引腳上使用,以實(shí)現(xiàn) GbE 到 FPGA 鏈接的最低功耗實(shí)現(xiàn)。

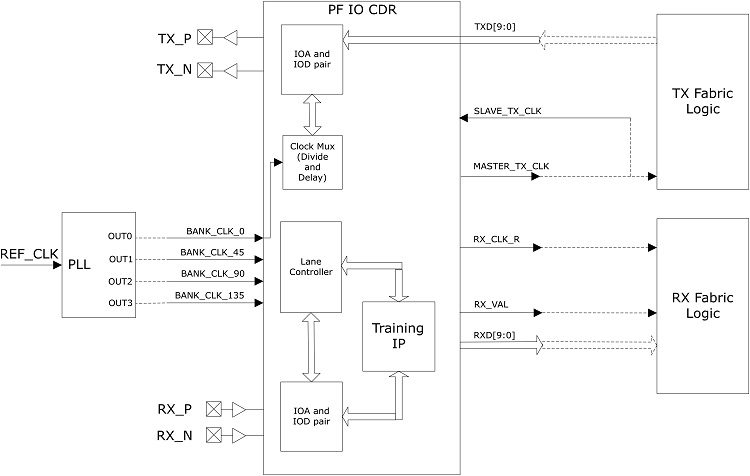

許多嵌入式產(chǎn)品開(kāi)發(fā)人員使用 GbE 來(lái)實(shí)現(xiàn)越來(lái)越多的連接。這些鏈接不再僅適用于數(shù)據(jù)有效負(fù)載,而且在控制、管理、狀態(tài)等方面變得無(wú)處不在。雖然低端和傳統(tǒng)中端 FPGA 都可以支持這些 1-Gbps 速度,但它們需要收發(fā)器來(lái)實(shí)現(xiàn) 1.25-Gbps SGMII 接口以及其他高速接口。理想情況下,設(shè)備應(yīng)具有專門分配的通用 I/O 引腳以支持 SGMII(圖 1)。

圖 1:傳統(tǒng)和中檔 FPGA 可以支持 1-Gbps 速度,但它們需要收發(fā)器來(lái)實(shí)現(xiàn) 1.25-Gbps SGMII 接口。

低端 FPGA 和傳統(tǒng)中端 FPGA 沒(méi)有這個(gè)特性,所以它們必須依賴收發(fā)器。以這種方式實(shí)現(xiàn)接口可能具有挑戰(zhàn)性,因?yàn)檫@些收發(fā)器接口非常珍貴且經(jīng)常稀缺。為了有足夠的它們來(lái)滿足更高性能的接口要求,設(shè)計(jì)人員以前必須選擇更昂貴、更高密度的 FPGA 架構(gòu)。

工業(yè)設(shè)計(jì)中通常不需要這些大型 FPGA 結(jié)構(gòu),但設(shè)計(jì)人員無(wú)論如何都被迫選擇它們,只是為了擁有足夠的額外收發(fā)器。此外,這些更大的設(shè)備意味著需要更大的封裝尺寸。結(jié)果是工業(yè)市場(chǎng)需要相反的更高的功耗和成本。

當(dāng)今的低功耗、成本優(yōu)化的中檔密度 FPGA 逆勢(shì)而上,提供了一種通過(guò) GPIO 上的 SGMII 滿足眾多千兆以太網(wǎng)鏈路要求的新方法。一些解決方案更進(jìn)一步,將時(shí)鐘和數(shù)據(jù)恢復(fù) (CDR) 電路集成到可支持 1.25 Gbps 的高速 LVDS I/O 中。這些特性使器件能夠在眾多 GPIO 引腳上支持 SGMII 接口。與使用傳統(tǒng)中端或高端 FPGA 創(chuàng)建的設(shè)計(jì)相比,使用這種架構(gòu),設(shè)計(jì)人員可以降低其設(shè)計(jì)的成本、尺寸和功耗。

平衡速度、成本和功耗

并非每個(gè)帶有通信接口的設(shè)計(jì)都需要極高的性能,但在整個(gè)市場(chǎng)中,處理需求都在增加,而接口卻越來(lái)越快。這些因素要求 FPGA 支持高達(dá) 12.5 Gbps 的串行接口,以實(shí)現(xiàn)以下越來(lái)越常見(jiàn)的選項(xiàng):

PCIe Gen2 需要 5 Gbps

HDMI 2.0b,需要 6 Gbps

10 GbE 需要 10 Gbps

JESD204B,最高可運(yùn)行 12.5 Gbps

這些高速串行接口要求收發(fā)器以上述速度運(yùn)行,但功耗也應(yīng)優(yōu)化。對(duì)于基于高端架構(gòu)的高端 FPGA 或中端 FPGA,這些速率的性能微不足道。不幸的是,這些設(shè)備也消耗非常高的功率,需要很大的外形尺寸,并且通常超出許多設(shè)計(jì)的預(yù)算。

另一方面,低密度 FPGA 通常沒(méi)有收發(fā)器,并且包含它們的那些不支持列出的性能速率。平衡收發(fā)器速度、低成本和功率效率的答案是使用具有邏輯元件 (LE) 和收發(fā)器的正確組合的中等密度 FPGA,以支持所需的數(shù)據(jù)速率。

通過(guò)這些選項(xiàng),工業(yè)架構(gòu)師可以支持最新的高速串行接口,同時(shí)還擁有足夠的片上 LE 來(lái)實(shí)現(xiàn)必要的電路板功能。此外,在 GPIO 和收發(fā)器上實(shí)現(xiàn) SGMII 的能力通常使設(shè)計(jì)人員能夠選擇更小的封裝尺寸和密度。這降低了系統(tǒng)成本并降低了 FPGA 功能所需的功率。

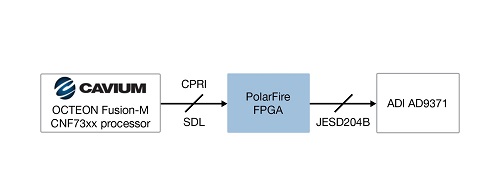

需要串行接口的一個(gè)例子是無(wú)線微蜂窩。這些設(shè)計(jì)通常使用處理器來(lái)處理大部分信號(hào)處理,同時(shí)利用 FPGA 進(jìn)行自定義信號(hào)調(diào)節(jié)并連接到 ADC 和 DAC,如圖2 所示。

圖 2:串行接口設(shè)計(jì)示例。

在此示例中,F(xiàn)PGA 使用收發(fā)器實(shí)現(xiàn) CPRI 或?qū)S写袛?shù)字鏈路 (SDL) 到 Cavium 處理器,并通過(guò) JESD204B 實(shí)現(xiàn)到 Analog Devices ADC/DAC 的串行鏈路。除了執(zhí)行串行橋接功能外,F(xiàn)PGA 的結(jié)構(gòu)還可以實(shí)現(xiàn)信號(hào)調(diào)理算法,例如波峰因數(shù)降低 (CFR) 和其他功能。該實(shí)施方案為小型蜂窩和微蜂窩應(yīng)用提供了更低功耗的解決方案和更小的占位面積。

實(shí)現(xiàn) DDR4 接口 的新方法

工程師傾向于連接到 FPGA 的最常見(jiàn)存儲(chǔ)器是基于 DDR DRAM 的設(shè)備。有幾代可供選擇,最好的選擇通常是使用已經(jīng)出貨一段時(shí)間且不是絕對(duì)最新標(biāo)準(zhǔn)的內(nèi)存。

對(duì)于 DRAM,DDR4 提供最佳的每比特成本,并且其架構(gòu)將被支持多年。盡管 DDR3 仍然是設(shè)計(jì)的可行選擇,但大多數(shù)新設(shè)計(jì)都選擇 DDR4,因?yàn)樗鼘⒃谖磥?lái)提供更低的價(jià)格、更快的性能和更寬的單芯片數(shù)據(jù)總線。

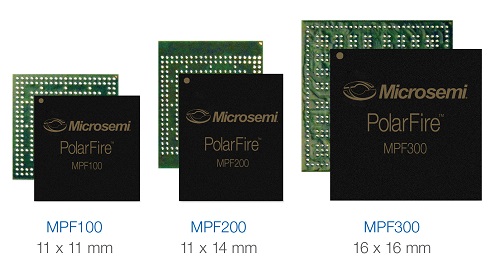

沒(méi)有支持 DDR4 存儲(chǔ)器接口的低密度 FPGA,因此設(shè)計(jì)人員必須使用基于高端架構(gòu)構(gòu)建的中等密度 FPGA 來(lái)實(shí)現(xiàn)這些接口。相比之下,當(dāng)今最新的中端 FPGA 專為這些接口而構(gòu)建,以顯著降低的成本和功耗提供所需的 DDR4 性能,同時(shí)實(shí)現(xiàn)嵌入式設(shè)計(jì)所需的更小尺寸(圖 3)。這些器件的封裝尺寸范圍從 16 x 16 mm 到 11 x 11 mm。

圖 3:多種密度和外形尺寸的 FPGA。

隨著通信、工業(yè)和嵌入式設(shè)計(jì)對(duì)更高性能接口、更多連接和更低成本的需求不斷增長(zhǎng),系統(tǒng)架構(gòu)師和工程師需要尋找新的解決方案。當(dāng)今的低功耗、中等密度 FPGA 解決了這些設(shè)計(jì)挑戰(zhàn),將更大的價(jià)值與更低的功耗相結(jié)合,同時(shí)仍提供現(xiàn)代設(shè)計(jì)所需的接口選項(xiàng)和其他功能。

-

FPGA

+關(guān)注

關(guān)注

1631文章

21806瀏覽量

606573 -

接口

+關(guān)注

關(guān)注

33文章

8726瀏覽量

152067 -

GPIO

+關(guān)注

關(guān)注

16文章

1217瀏覽量

52469

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用FPGA對(duì)40G以太網(wǎng)接口芯片Serdes進(jìn)行測(cè)試的方法

AMD成本優(yōu)化型產(chǎn)品的創(chuàng)新之處

高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時(shí)序誤差的設(shè)計(jì)考慮

高速數(shù)據(jù)接口適用于半導(dǎo)體測(cè)試中的精密高速ADC

FPGA高速收發(fā)器的特點(diǎn)和應(yīng)用

談一談FPGA設(shè)計(jì)中的功率計(jì)算

FPGA的sata接口設(shè)計(jì)時(shí)需要注意哪些問(wèn)題

FPGA的PCIE接口應(yīng)用需要注意哪些問(wèn)題

FPGA的高速接口應(yīng)用注意事項(xiàng)

FPGA開(kāi)發(fā)如何降低成本,比如利用免費(fèi)的IP內(nèi)核

能源管理系統(tǒng)如何降低運(yùn)維成本?

中端FPGA成為主戰(zhàn)場(chǎng),Altera獨(dú)立后的市場(chǎng)格局

中端FPGA如何降低高速接口的成本

中端FPGA如何降低高速接口的成本

評(píng)論