功耗是芯片中比較重要的一個(gè)性能指標(biāo),有時(shí)甚至可以決定一個(gè)芯片的成敗。眾所周知,前段時(shí)間鬧得沸沸揚(yáng)揚(yáng)的“驍龍火龍”事件,就大大影響了這款芯片的市占率。對(duì)于工業(yè)級(jí)和車(chē)規(guī)級(jí)的芯片,功耗的高低體現(xiàn)的不是很明顯。對(duì)于消費(fèi)級(jí)芯片(如手機(jī)CPU,IoT芯片等),由于往往應(yīng)用在小型移動(dòng)設(shè)備中,低功耗設(shè)計(jì)就顯得尤為重要。

有業(yè)內(nèi)專家曾經(jīng)指出,在不同的設(shè)計(jì)層次,進(jìn)行功耗優(yōu)化的效果也不同。下表顯示了在一個(gè)產(chǎn)品的不同周期,可以減少功耗的百分比。

| 設(shè)計(jì)層次 | 降低功耗百分比 |

| 版圖級(jí) | <5% |

| 晶體管級(jí) | 5% |

| 門(mén)級(jí) | 10% |

| RTL級(jí) | 20% |

| 系統(tǒng)級(jí) | >50% |

門(mén)控時(shí)鐘介紹

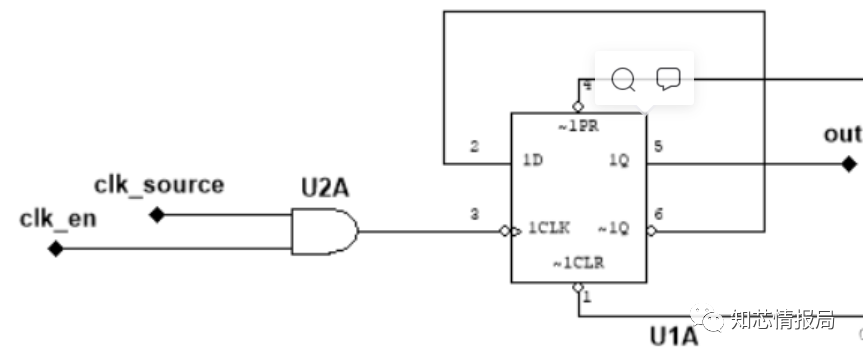

一般來(lái)講,時(shí)鐘樹(shù)貫穿于整個(gè)芯片內(nèi)部,由大量的buffer和反相器組成。時(shí)鐘信號(hào)作為芯片中toggle率最高的信號(hào),功耗可高達(dá)整個(gè)芯片功耗的30%,甚至更高。加入門(mén)控時(shí)鐘(clock gating,cg)電路,可大大降低時(shí)鐘樹(shù)的toggle行為,從而降低開(kāi)關(guān)功耗。此外,時(shí)鐘引腳開(kāi)關(guān)行為的減少,寄存器的內(nèi)部功耗也會(huì)減少。門(mén)控時(shí)鐘是減少功耗的有力手段,在時(shí)鐘被門(mén)控關(guān)閉后,該時(shí)鐘網(wǎng)絡(luò)和其中的寄存器都會(huì)停止翻轉(zhuǎn),因此功耗會(huì)顯著減低。一個(gè)典型的門(mén)控時(shí)鐘設(shè)計(jì)如下圖所示:

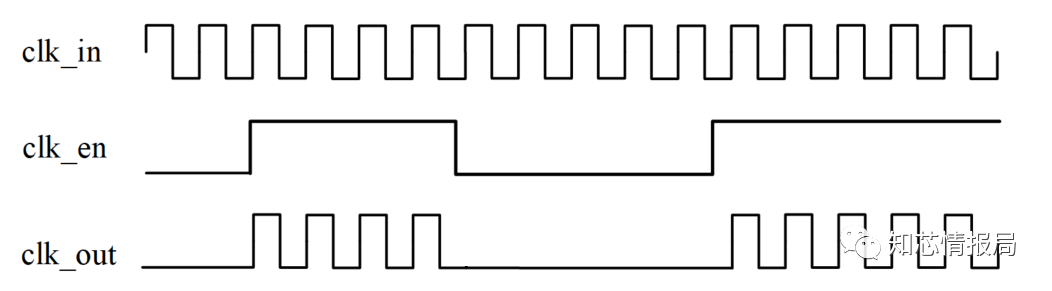

對(duì)于時(shí)鐘源clk_source經(jīng)過(guò)一個(gè)額外的與門(mén)U2A,當(dāng)clk_en為高時(shí),clk_source能過(guò)通過(guò)到達(dá)U1A觸發(fā)器,當(dāng)clk_en為低時(shí)clk_source無(wú)法到達(dá)觸發(fā)器。當(dāng)clk_en為低時(shí),觸發(fā)器及其時(shí)鐘網(wǎng)絡(luò)中的所有組合邏輯停止翻轉(zhuǎn),out端保持不變。由于clk_source經(jīng)過(guò)了U2A與門(mén),所有會(huì)產(chǎn)生一定的時(shí)鐘偏移。在波形分析上,下面這個(gè)圖可以比較好的理解門(mén)控時(shí)鐘的概念,只有當(dāng)clk_en為高的時(shí)候,clk_out=clk_in,否則,clk_out=0。

cg方法1:使用與邏輯

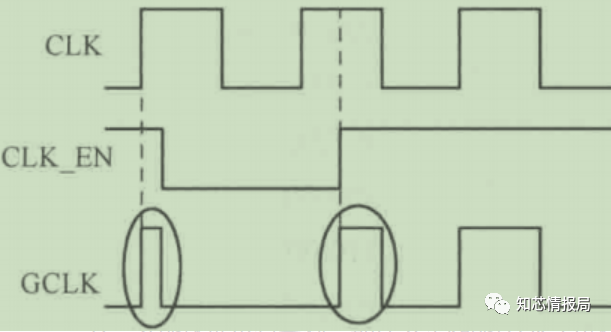

這個(gè)也是最簡(jiǎn)單的方法,直接將時(shí)鐘使能控制(門(mén)控)信號(hào)與時(shí)鐘做"與"邏輯。這個(gè)辦法簡(jiǎn)單粗暴,但是也有一個(gè)嚴(yán)重的缺點(diǎn):會(huì)有毛刺。當(dāng)clk為低的時(shí)候,clk_en可任意變化,gclk都是低。但當(dāng)clk為高的時(shí)候,clk_en必須保持不變,才能保證沒(méi)有毛刺,那什么東西能讓clk_en保持不變呢?答案就是:鎖存器

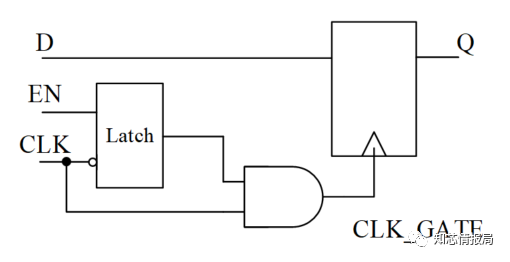

cg方法2:加入鎖存器

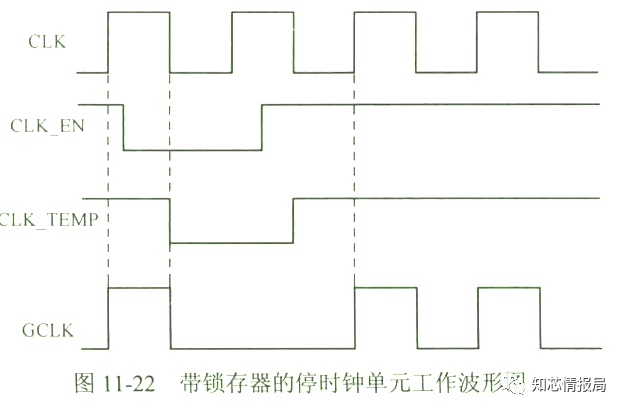

在clk為低時(shí)鎖存器連通、clk為高時(shí)鎖存器鎖住,如下圖:

波形圖如下,可見(jiàn)當(dāng)clk為低的時(shí)候gclk為低沒(méi)跑,但clk為高的時(shí)候,gclk的值可看作是clk上升沿采樣的clk_en的值。所以使用Latch可以有效地鎖存clk_en值,同時(shí)不影響clk的周期性。Latch門(mén)控時(shí)鐘的本質(zhì)是clk上升沿鎖住了clk_en值,讓clk為高時(shí)clk_temp不會(huì)翻轉(zhuǎn),所以消除了毛刺。

其RTL代碼如下:

always@(*) beginif(clk)clk_temp = clk_en;elseclk_temp = clk_en;endassign gclk = clk & clk_temp;

cg方法3:使用標(biāo)準(zhǔn)單元庫(kù)

雖然使用 latch 可以解決門(mén)控時(shí)鐘毛刺的出現(xiàn),但是時(shí)序也需要嚴(yán)格的約束。FPGA 或 IC 設(shè)計(jì)時(shí),綜合庫(kù)中往往會(huì)有集成門(mén)控邏輯單元。此類門(mén)控邏輯單元經(jīng)過(guò)了大量的更新迭代和驗(yàn)證,使用起來(lái)更加的方便、安全。因此一般情況下,門(mén)控時(shí)鐘的設(shè)計(jì)也都會(huì)直接調(diào)用專用的集成門(mén)控邏輯單元。調(diào)用方式和基本的與門(mén)、緩沖器等基本單元類似,直接例化即可。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

460文章

52529瀏覽量

441340 -

低功耗

+關(guān)注

關(guān)注

11文章

2810瀏覽量

104967 -

門(mén)控時(shí)鐘

+關(guān)注

關(guān)注

0文章

27瀏覽量

9122

原文標(biāo)題:數(shù)字芯片中的低功耗設(shè)計(jì)

文章出處:【微信號(hào):IP與SoC設(shè)計(jì),微信公眾號(hào):IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

降低電路漏電功耗的低功耗設(shè)計(jì)方法

cogobuy降低功耗的措施

降低低功耗藍(lán)牙的功耗

CC2530 如何降低ZC發(fā)現(xiàn)網(wǎng)絡(luò)的頻次以降低功耗?

vs1053如何降低功耗

IC芯片功耗有哪些降低方法?

請(qǐng)問(wèn)stm32不進(jìn)入低功耗模式怎么降低功耗?

如何利用FPGA滿足電信應(yīng)用中的降低功耗要求?

如何降低ZC發(fā)現(xiàn)網(wǎng)絡(luò)的頻次以降低功耗?

提高功率降低功耗的方法

寄存器傳輸級(jí)低功耗設(shè)計(jì)方法

芯片設(shè)計(jì)降低功耗的方法

芯片設(shè)計(jì)降低功耗的方法

評(píng)論