在過去的 50 年中,影響最深遠的技術成就可能是晶體管一如既往地穩步向更小邁進,使它們更緊密地結合在一起,并降低了它們的功耗。然而,自從 20 多年前筆者在英特爾開始職業生涯以來,我們就一直在聽到警報——晶體管下降到無窮小的狀態即將結束。然而,年復一年,出色的新創新繼續推動半導體行業進一步發展。

在此過程中,我們的工程師不得不改變晶體管的架構,以便我們能在提高芯片性能的同時繼續縮小面積和功耗。這也是推動我們將在20 世紀下半葉流行的“平面”晶體管設計在 2010 年代上半替換為3D 鰭形器件的原因。現在,FinFET也有一個結束日期,一個新的全方位 (GAA) 結構很快就會投入生產。

但我們必須看得更遠,因為即使是這種新的晶體管架構(英特爾稱之為 RibbonFET),我們縮小尺寸的能力也有其局限性。

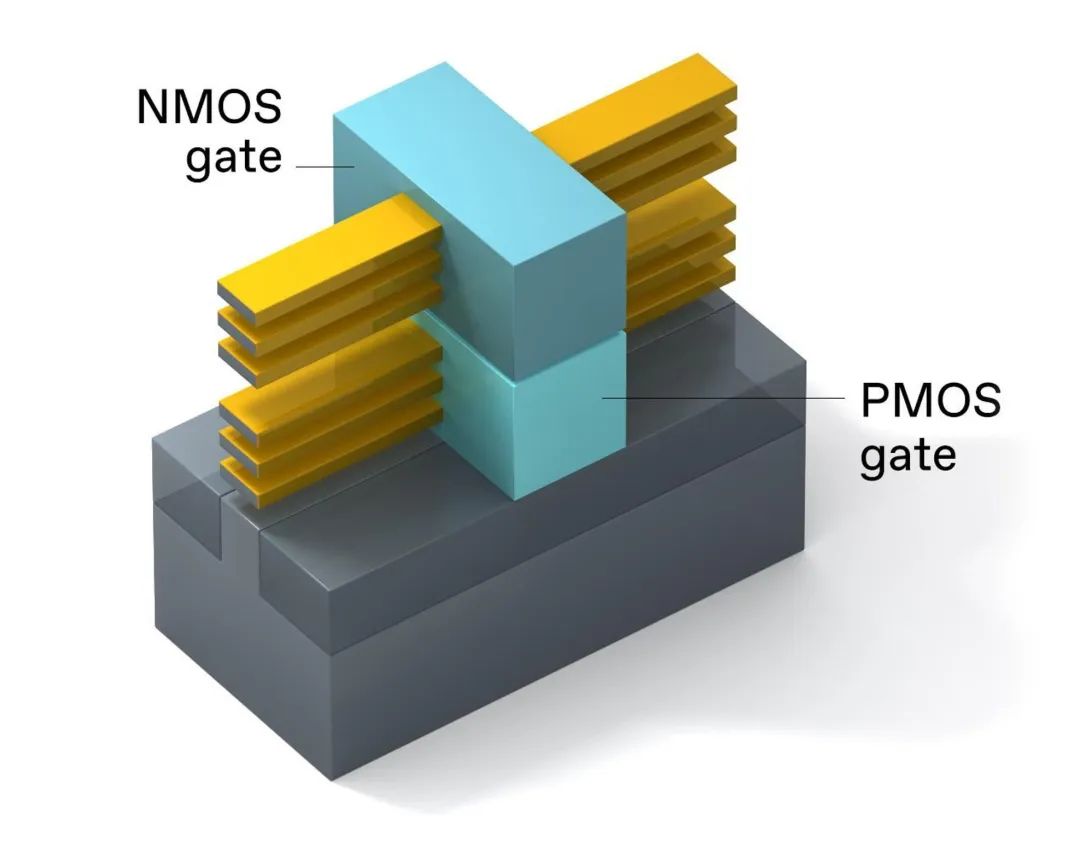

那么,我們將在何時轉向未來的縮放方式?我們將繼續關注第三維度。我們已經創建了相互堆疊的實驗設備,其提供的邏輯縮小了 30% 到 50%。至關重要的是,頂部和底部器件是兩種互補類型,NMOS 和 PMOS,它們是過去幾十年所有邏輯電路的基礎。我們相信這種 3D 堆疊的互補金屬氧化物半導體 (CMOS) 或 CFET(互補場效應晶體管)將是將摩爾定律延伸到下一個十年的關鍵。

晶體管的演變

持續創新是摩爾定律的重要基礎,但每次改進都需要權衡取舍。要了解這些權衡以及它們如何不可避免地將我們引向 3D 堆疊 CMOS,您需要一些有關晶體管運作的背景知識。

每個金屬氧化物半導體場效應晶體管或 MOSFET 都具有相同的一組基本部件:柵極疊層(gate stack)、溝道區(channel region)、源極(source)和漏極(drain)。源極和漏極經過化學摻雜,使它們要么富含移動電子(n型),要么缺乏它們(p型)。溝道區具有與源極和漏極相反的摻雜。

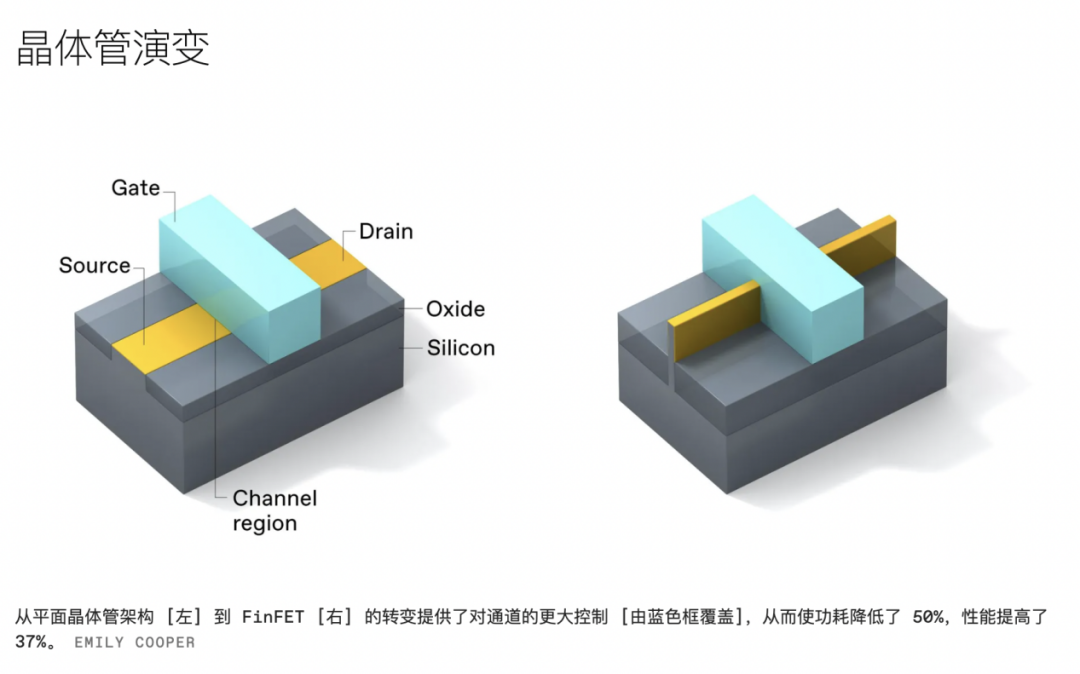

在 2011 年之前用于先進微處理器的平面版本晶體管中,MOSFET 的柵極堆疊位于溝道區正上方,旨在將電場投射到溝道區。向柵極(相對于源極)施加足夠大的電壓會在溝道區域中形成一層移動電荷載流子,從而允許電流在源極和漏極之間流動。

當我們縮小經典的平面晶體管時,一個被設備物理學家稱之為“短溝道效應”的東西引起了大家的廣泛關注。從基本上說,這是因為源極和漏極之間的距離變得如此之小,以至于電流會在不應該的情況下通過溝道泄漏,這主要歸因于柵電極難以耗盡電荷載流子的溝道。為了解決這個問題,業界轉向了一種完全不同的晶體管架構—— FinFET。它將柵極包裹在三個側面的溝道周圍,以提供更好的靜電控制。

英特爾于 2011 年推出的22 納米節點上引進了其 FinFET,并將其用于第三代酷睿處理器的生產,從那時起,該晶體管架構一直是摩爾定律的主力。使用 FinFET,我們還可以在更低的電壓下運行,并且仍然具有更少的泄漏,在與上一代平面架構相同的性能水平下將功耗降低了約 50%。FinFET 的切換速度也更快,性能提升了 37%。而且由于“Fin”的兩個垂直側都發生了傳導,因此與僅沿一個表面傳導的平面器件相比,該器件可以通過給定的硅區域驅動更多的電流。

然而,我們在轉向 FinFET 時確實失去了一些東西。在平面器件中,晶體管的寬度由光刻定義,因此它是一個高度靈活的參數。但在 FinFET 中,晶體管寬度以離散增量(discrete increments)的形式出現——一次添加一個鰭——這一特性通常被稱為鰭量化(fin quantization)。盡管 FinFET 可能很靈活,但鰭量化仍然是一個重要的設計約束。圍繞它的設計規則以及增加更多鰭片以提高性能的愿望增加了邏輯單元的整體面積,并使將單個晶體管變成完整邏輯電路的互連堆棧復雜化。它還增加了晶體管的電容,從而降低了它的一些開關速度。因此,雖然 FinFET 作為行業主力為我們提供了很好的服務,但仍需要一種新的、更精細的方法。

在 RibbonFET 中,柵極環繞晶體管溝道區域以增強對電荷載流子的控制。新結構還可以實現更好的性能和更精細的優化。

上述需求就推動了FinFET面世11年后,新晶體管架構RibbonFET的產生。在其中,柵極完全圍繞溝道,對溝道內的電荷載流子提供更嚴格的控制,這些溝道現在由納米級硅帶形成。使用這些納米帶(也稱為納米片),我們可以再次使用光刻技術根據需要改變晶體管的寬度。

去除量化約束后,我們可以為應用生成適當大小的寬度。這讓我們能夠平衡功率、性能和成本。更重要的是,通過堆疊和并行操作的Ribbon,該設備可以驅動更多電流,在不增加設備面積的情況下提高性能。

英特爾認為 RibbonFET 是在合理功率下實現更高性能的最佳選擇,他們將在 2024 年推出的Intel 20A制造工藝上引入這個晶體管架構,伴隨而來的還有如英特爾的背面供電技術 PowerVia等創新。

堆疊式 CMOS

平面、FinFET 和 RibbonFET 晶體管的一個共同點是它們都使用 CMOS 技術,如上所述,該技術由n型 (NMOS) 和p型 (PMOS) 晶體管組成。CMOS 邏輯在 1980 年代成為主流,因為它消耗的電流明顯少于替代技術,特別是僅 NMOS 電路。更少的電流也導致更高的工作頻率和更高的晶體管密度。

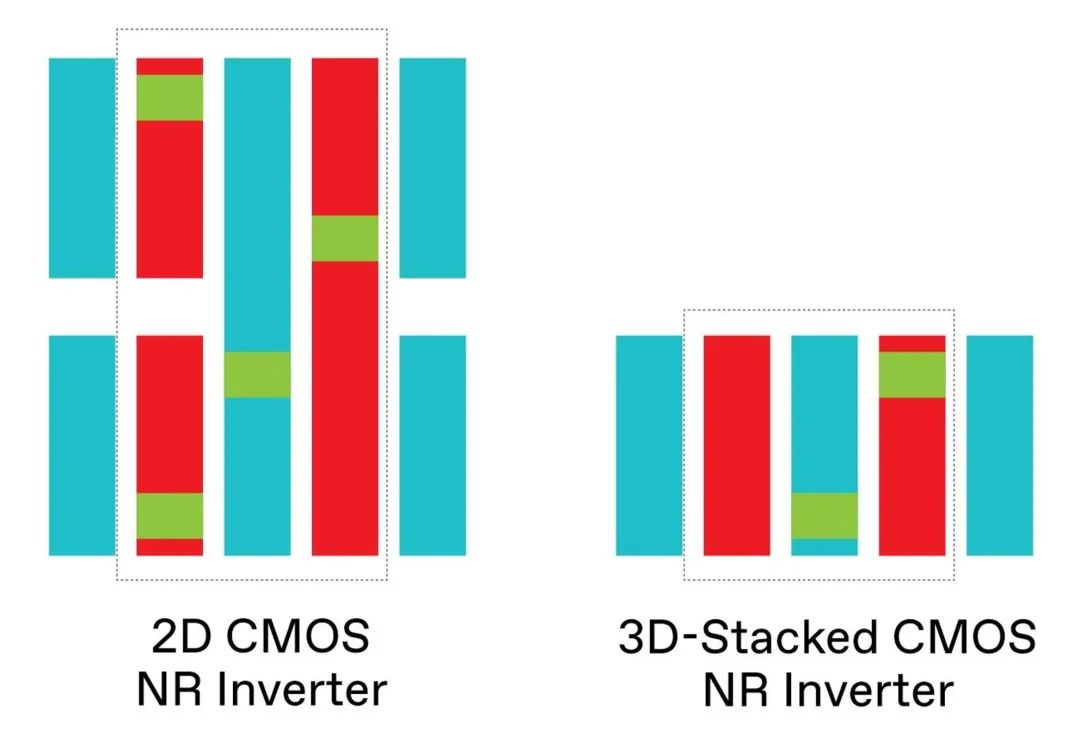

迄今為止,所有 CMOS 技術都將標準 NMOS 和 PMOS 晶體管對并排放置。但在 2019 年 IEEE 國際電子器件會議 (IEDM)的主題演講中,英特爾介紹了將 NMOS 晶體管置于 PMOS 晶體管之上的 3D 堆疊晶體管的概念。次年,在 IEDM 2020 上,英特爾展示了第一個使用這種 3D 技術的邏輯電路的設計—— inverter。結合適當的互連,3D 堆疊 CMOS 方法有效地將 inverter占位面積減半,使面積密度增加一倍,進一步突破摩爾定律的極限。

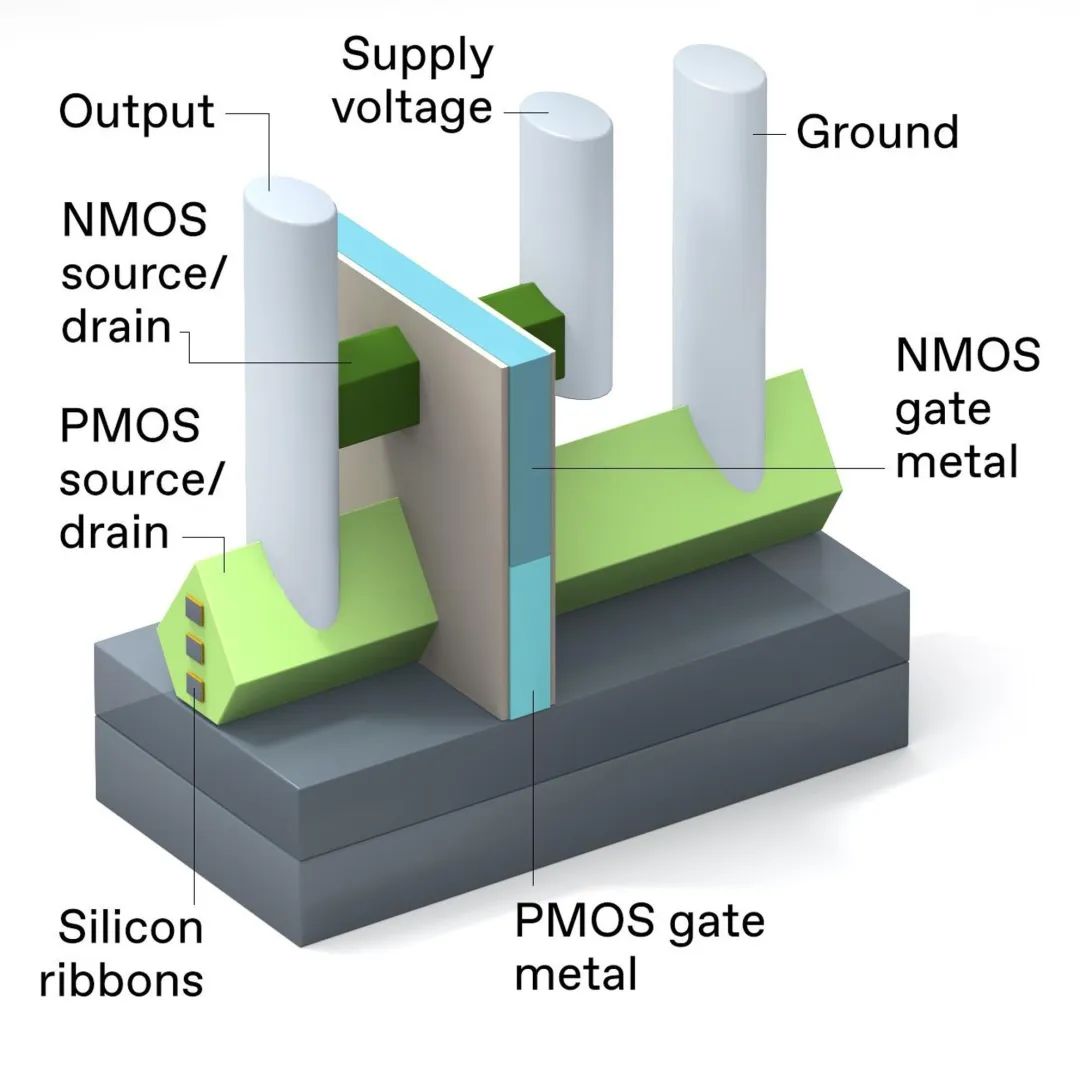

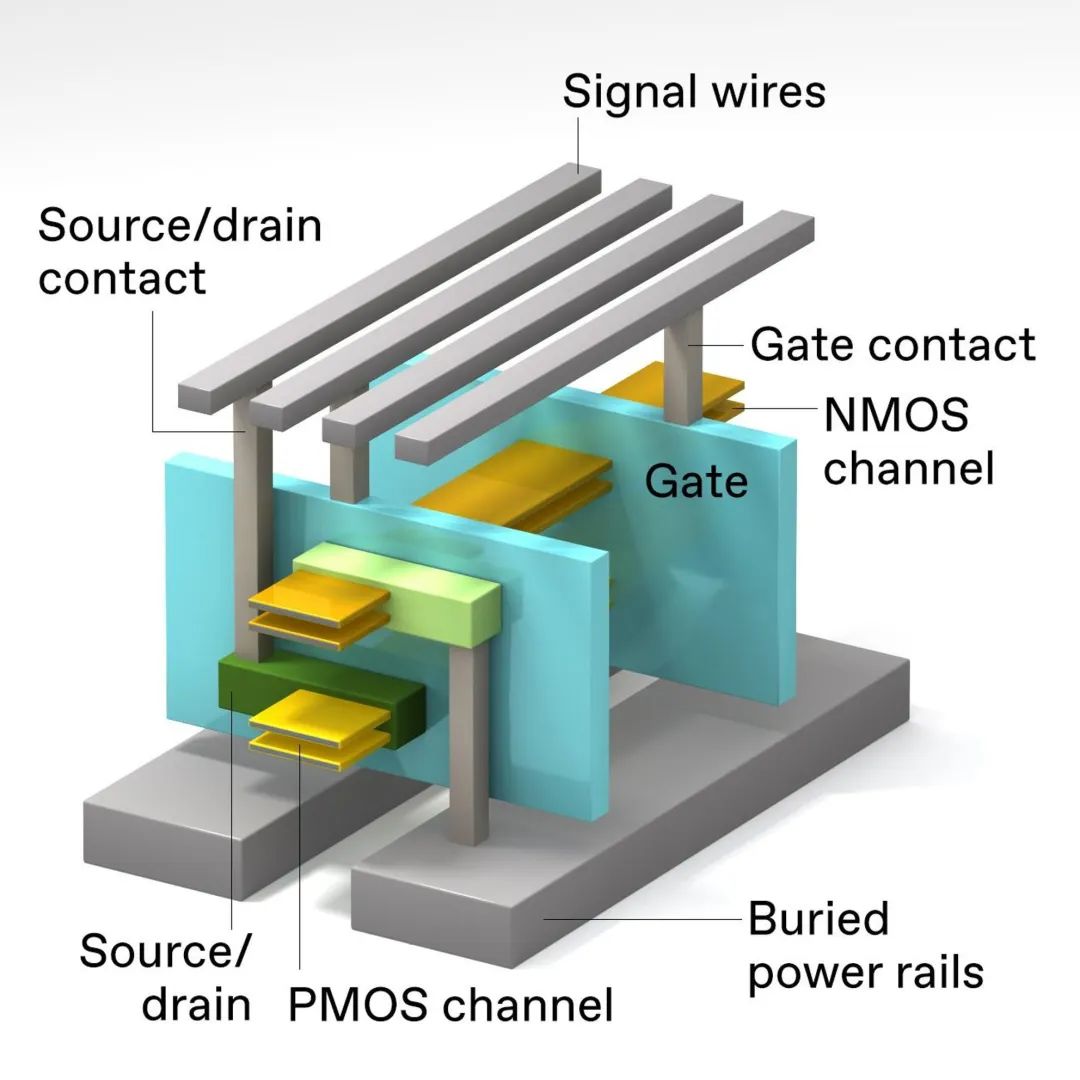

3D 堆疊 CMOS 將 PMOS 器件置于 NMOS 器件之上,其占用空間與單個 RibbonFET 相同。NMOS 和 PMOS 柵極使用不同的金屬。

利用 3D 堆疊的潛在優勢意味著解決許多工藝集成挑戰,其中一些挑戰將擴展 CMOS 制造的極限。

英特爾使用所謂的自對準工藝(self-aligned )構建了 3D 堆疊 CMOS inverter,其中兩個晶體管都在一個制造步驟中構建。這意味著通過外延(晶體沉積)構建 n型和p型源極和漏極,并為兩個晶體管添加不同的金屬柵極。通過結合源漏和雙金屬柵工藝,英特爾能夠創建不同導電類型的硅納米帶(p型和n型)來組成堆疊的 CMOS 晶體管對。該設計還讓我們可以調整器件的閾值電壓——晶體管開始開關的電壓——分別針對頂部和底部納米帶。

在 CMOS 邏輯中,NMOS 和 PMOS 器件通常并排放置在芯片上。早期的原型將 NMOS 器件堆疊在 PMOS 器件之上,從而壓縮了電路尺寸

英特爾是如何做到這一切的?

自對準 3D CMOS 制造始于硅晶片。在這個晶圓上,英特爾沉積了硅和硅鍺的重復層,這種結構稱為超晶格(superlattice)。然后,英特爾使用光刻圖案切割部分超晶格并留下鰭狀結構。超晶格晶體為后來發生的事情提供了強大的支撐結構。

接下來,英特爾將一塊“虛擬”(dummy)多晶硅沉積在器件柵極將進入的超晶格部分的頂部,以保護它們免受該制程的下一步影響。該步驟稱為垂直堆疊雙源/漏極工藝(vertically stacked dual source/drain process),在頂部納米帶(未來的 NMOS 器件)的兩端生長摻磷硅( phosphorous-doped silicon),同時在底部納米帶(未來的 PMOS 器件)上選擇性地生長摻硼硅鍺(boron-doped silicon germanium)。在這個步驟之后,英特爾在源極和漏極周圍沉積電介質,以將它們彼此電隔離,然后將晶圓拋光至完美的平整度。

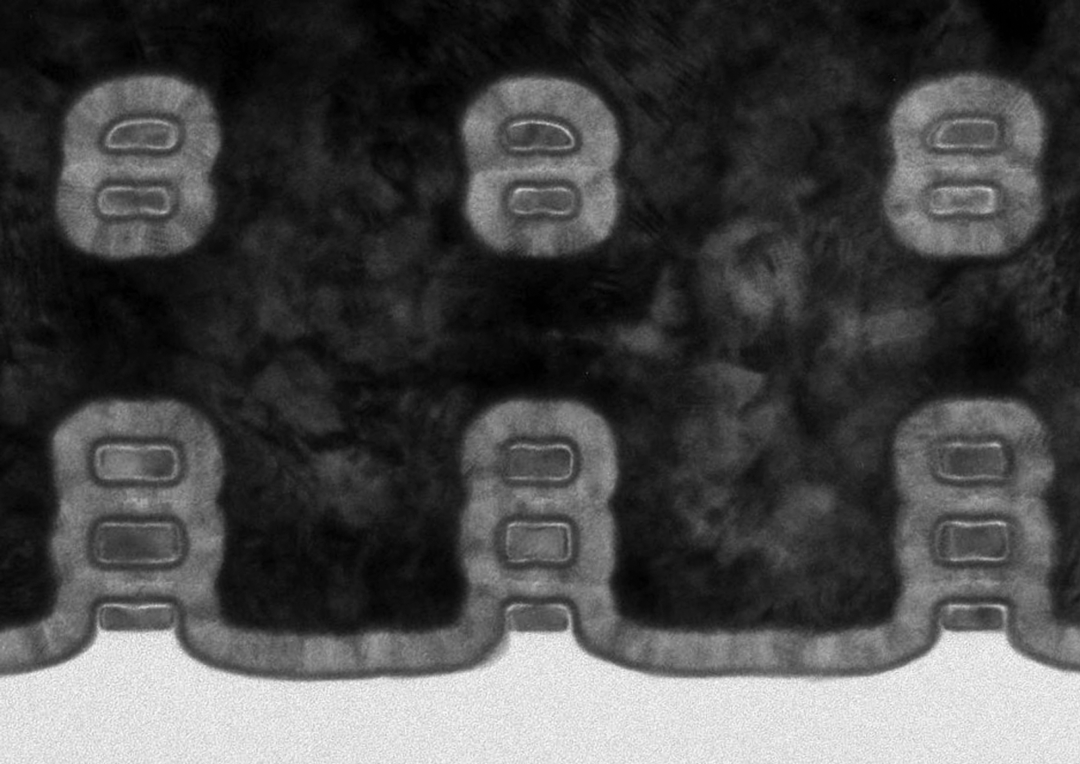

3D堆疊inverter的側視圖顯示了其連接的復雜性

最后,構建柵極。

首先,我們移除我們之前放置的那個虛擬門,露出硅納米帶。接下來我們只蝕刻掉硅鍺,釋放出一疊平行的硅納米帶,這將是晶體管的溝道區。然后,我們在納米帶的所有側面涂上一層薄薄的絕緣體,該絕緣體具有高介電常數。納米帶溝道是如此之小,并且以這樣一種方式定位,以至于我們無法像使用平面晶體管那樣有效地化學摻雜它們。相反,我們使用稱為功函數(work function)的金屬柵極(metal gates)特性來賦予相同的效果。我們用一種金屬圍繞底部納米帶以形成 p摻雜通道,用另一種金屬圍繞頂部納米帶形成n-摻雜通道。這樣,柵疊層就完成了,兩個晶體管也完成了。

這個過程可能看起來很復雜,但它比替代技術更好——一種稱為順序 3D 堆疊(sequential 3D stacking )CMOS 的技術。采用這種方法,NMOS 器件和 PMOS 器件構建在不同的晶圓上,將兩者粘合,然后將 PMOS 層轉移到 NMOS 晶圓上。相比之下,自對準 3D 工藝需要更少的制造步驟并更嚴格地控制制造成本,這是英特爾在研究中展示并在 IEDM 2019 上報告的技術。

通過在 PMOS 晶體管上堆疊 NMOS,3D 堆疊有效地將每平方毫米的 CMOS 晶體管密度翻倍,盡管實際密度取決于所涉及的邏輯單元的復雜性。inverter單元從上方顯示,指示源極和漏極互連 [紅色]、柵極互連 [藍色] 和垂直連接 [綠色]

重要的是,自對準方法還避免了鍵合兩個硅片時可能發生的未對準問題。盡管如此,正在探索順序 3D 堆疊以促進硅與非硅溝道材料(例如鍺和 III-V 半導體材料)的集成。當英特爾希望能將光電子和其他功能緊密集成在單個芯片上時,這些方法和材料可能會變得相關。

新的自對準 CMOS 工藝及其創建的 3D 堆疊 CMOS 運行良好,似乎有很大的進一步小型化空間。在這個早期階段,這是非常令人鼓舞的。具有 75 nm 柵極長度的器件展示了具有出色器件可擴展性和高導通電流的低泄漏。另一個有希望的跡象:英特爾已經制造出兩組堆疊器件之間的最小距離僅為 55 nm的晶圓。雖然其獲得的器件性能結果本身并沒有記錄,但它們確實與構建在相同硅片上且具有相同處理的單個非堆疊控制器件相比較。

對 3D 堆疊 CMOS 進行所有需要的連接是一項挑戰。需要從設備堆棧下方進行電源連接。在此設計中,NMOS 器件 [頂部] 和 PMOS 器件 [底部] 具有單獨的源極/漏極觸點,但兩個器件都有一個共同的柵極

在工藝集成和實驗工作的同時,英特爾正在進行許多理論、模擬和設計研究,以期深入了解如何最好地使用 3D CMOS。通過這些,英特爾發現了晶體管設計中的一些關鍵考慮因素。值得注意的是,我們現在知道我們需要優化 NMOS 和 PMOS 之間的垂直間距——因為如果太短會增加寄生電容,但如果太長會增加兩個器件之間互連的電阻。任何一種極端都會導致更慢的電路消耗更多功率。

許多設計研究(例如美國 TEL 研究中心在 IEDM 2021上提出的一項研究)專注于在 3D CMOS 的有限空間內提供所有必要的互連,并且這樣做不會顯著增加它們構成的邏輯單元的面積。TEL 研究表明,在尋找最佳互連選項方面存在許多創新機會。該研究還強調,3D 堆疊 CMOS 將需要在設備上方和下方都有互連。這種方案,稱為埋地電源軌,采用為邏輯單元供電但不傳輸數據的互連,并將它們移至晶體管下方的硅片上。英特爾的 PowerVIA 技術正是這樣做的,計劃于 2024 年推出,因此將在使 3D 堆疊 CMOS 商業化方面發揮關鍵作用。

摩爾定律的未來

借助 RibbonFET 和 3D CMOS,英特爾有一條將摩爾定律延伸到 2024 年之后的清晰道路。在2005 年的一次采訪中,在被要求反思什么成就了他的定律的時候,戈登摩爾承認“不時驚訝于我們如何能夠取得進展。在此過程中,有好幾次,我以為我們已經走到了終點,事情逐漸減少,但我們的創意工程師想出了解決辦法。”

隨著向 FinFET 的轉變、隨之而來的優化,以及現在 RibbonFET 的發展以及最終 3D 堆疊 CMOS 的發展,以及圍繞它們的無數封裝改進的支持,我們認為 Moore 先生會再次感到驚訝。

審核編輯 :李倩

-

CMOS

+關注

關注

58文章

6011瀏覽量

238722 -

摩爾定律

+關注

關注

4文章

639瀏覽量

79838 -

晶體管

+關注

關注

77文章

10013瀏覽量

141465

原文標題:3D堆疊CMOS,晶體管的未來

文章出處:【微信號:AMTBBS,微信公眾號:世界先進制造技術論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

有關晶體管運作的背景知識

有關晶體管運作的背景知識

評論