在流片前驗證中如何測量功耗?

一般來說,功耗測量是在門級進行,通過由回歸向量組成的驗證平臺執行 DUT,然后跟蹤 DUT 的開關活動來完成。該方法有兩個問題。

首先,測試發生在設計周期的晚期。雖然與實際芯片的差異在 5% 以內,但沒有足夠的靈活性來糾正設計中的問題。更好的折中方法是在 RTL 評估動態功耗,這會導致與芯片的偏差較大(在15% 范圍內),但能提供更大的靈活性來支持設計修改。

其次,驗證平臺向量不能很好地代表設計將來的使用方式。為了實現準確的功耗估算,必須在運行實際工作負載和性能/功率基準測試的目標系統上盡可能準確地捕獲開關活動。

執行功耗分析的步驟是什么?如何完成?

顯然,RTL 仿真再也無法勝任這一要求苛刻的任務。需要一種層次化方法,從高級別的設計抽象開始,直到RTL 和門級。再也沒有任何單一工具能夠完成全部任務。相反,讓各種特性實現最佳平衡的多種工具可以加速功耗估算和優化(表 1)。

第一步,整個 DUT 用 C/C++ 做高級抽象,根據硬件/軟件規格進行快速驗證,并非常粗略地估算功耗。

接下來,在一個混合設置中驗證功耗,該混合設置包含高級別抽象描述的設計部分(通常包括處理內核和存儲器,例如 Arm 快速模型))和 RTL 的其他設計部分。高級別抽象部分在主機服務器上運行,RTL 在硬件加速器上執行,二者通過基于事務的接口連接。

表 1. 需要采用一種層次化方法來加速功耗估算和分析過程。(信息來源:Lauro Rizzatti)

雖然硬件加速器以幾 MHz 的速度運行,但混合配置可以實現 50 MHz 左右的速度,足以快速啟動 Android、Linux 和其下的所有內核,以及執行基準測試和實際應用。

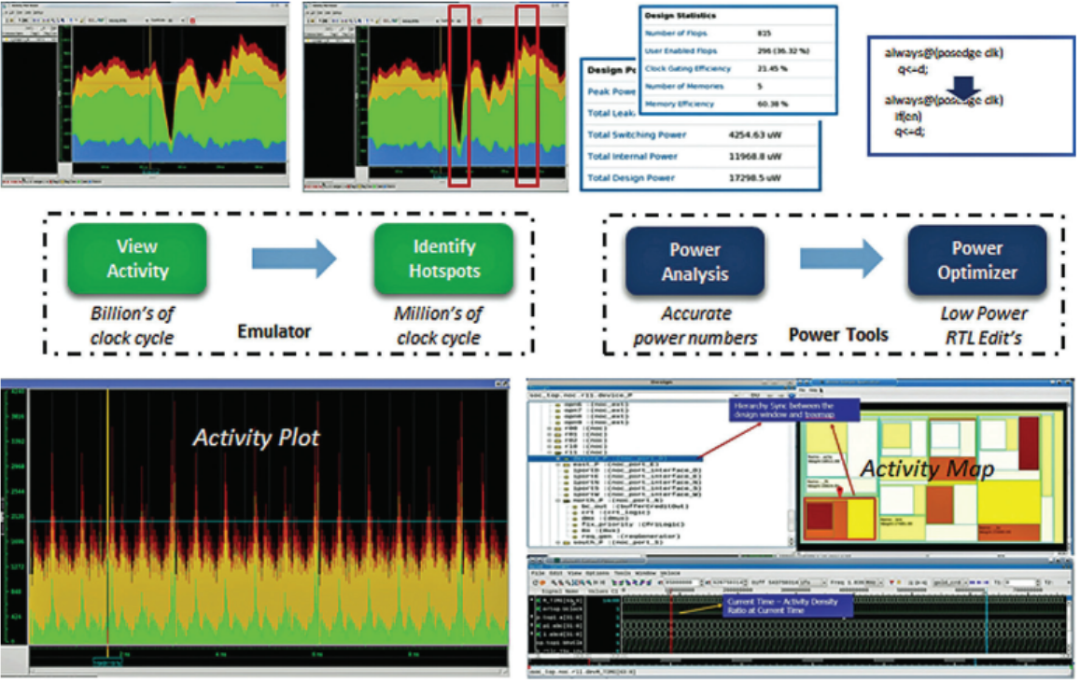

該設置提供了一個很好的基礎,支持在相對較短的時間內對整個設計的功耗進行分析。通過在數十億個時鐘周期的長期運行中繪制開關活動,設計團隊可以識別幾百萬時鐘周期范圍內的高功耗和低功耗熱點。同樣,通過在活動分布圖中拼貼功耗區域,團隊便可直觀地識別高低功耗的設計部分。

一旦確定熱點和關鍵區塊,團隊就可以切換到全 RTL,獲得對各設計網絡的準確詳細可見性。通過將活動繪圖與嵌入式軟件代碼相關聯,并將活動分布圖與RTL 代碼相關聯,團隊可以迅速聚焦于有潛在功耗問題的區域。

捕獲整個工作負載處理的完整設計活動,是非常重要的(圖 2),避免僅僅是采樣(通常利用 FPGA 平臺完成,缺乏完全的內部可見性)。

圖 2. 功耗工具可以利用活動分布圖和活動繪圖來跟蹤功耗趨勢分析。(信息來源:西門子 EDA)

審核編輯:湯梓紅

-

西門子

+關注

關注

98文章

3168瀏覽量

118183 -

功耗

+關注

關注

1文章

836瀏覽量

32649 -

RTL

+關注

關注

1文章

389瀏覽量

61030 -

DUT

+關注

關注

0文章

190瀏覽量

12943

原文標題:白皮書下載 | 片上系統設計中利用硬件加速器進行功耗分析

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【RA4L1-SENSOR】07 低功耗待機模式及功耗實測

Nordic功耗詳解

測試與測量 | 基于Enclustra FPGA開發低功耗頻譜分析儀

ARM開發板的功耗分析與優化

噪聲測量步驟有哪些

物聯網系統中TCP低功耗產品長連接狀態下降低功耗功能的實現方案

使用MSP430FR4xx和MSP430FR2xx MCU的片上VREF和10位ADC進行低功耗電池電壓測量

在流片前驗證中如何測量功耗 執行功耗分析的步驟是什么

在流片前驗證中如何測量功耗 執行功耗分析的步驟是什么

評論