多bit跨時鐘域

(大疆2020數字芯片)下列關于多bit數據跨時鐘域的處理思路,錯誤的有()

A. 發送方給出數據,接收方用本地時鐘同步兩拍再使用;

B. 發送方把數據寫到異步fifo,接收方從異步fifo里讀出;

C. 對于連續變化的信號,發送方轉為格雷碼發送,接收方收到后再轉為二進制;

D. 發送方給出數據,發送方給出握手請求,接收方收到后回復,發送方撤銷數據。

答案:A

解析:多bit跨時鐘域不能簡單使用打兩拍,打拍后可能數據錯亂;

CDC(Clock Domain Conversion)跨時鐘域分單bit和多bit傳輸,其中:

1. 單bit(慢時鐘域到快時鐘域):用快時鐘打兩拍,直接采一拍大概率也是沒問題的,兩拍的主要目的是消除亞穩態;

其中:

(1)為了更長的平均無故障時間 MTBF( Mean Time Between Failures),需要配合一個 ASYNC_REG 的約束,把用作簡單同步器的多個寄存器放入同一個 SLICE,以降低走線延時的不一致和不確定性。

(* ASYNC_REG = "TRUE" *) reg rst_reg_0;

(* ASYNC_REG = "TRUE" *) reg rst_reg_1;

(2)或者:直接在約束文件里進行約束

set_propertyASYNC_REGTRUE[get_cells[listrst_reg_0rst_reg_1]]

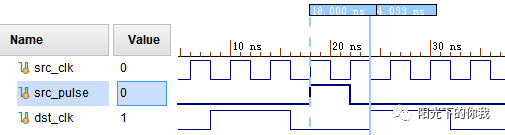

2. 單bit(快時鐘域到慢時鐘域):握手(脈沖展寬)、異步FIFO、異步雙口RAM;快時鐘域的信號脈寬較窄,慢時鐘域不一定能采到,可以通過握手機制讓窄脈沖展寬,慢時鐘域采集到信號后再“告訴”快時鐘域已經采集到信號,確保能采集到;

3. 多bit跨時鐘域:異步FIFO、異步雙口RAM、握手、格雷碼;

(1)使用異步FIFO的IP

實際上是用 FPGA 內部的 BRAM 來搭建,所有的控制邏輯都在 BRAM 內部,是推薦的 FIFO 實現方式。

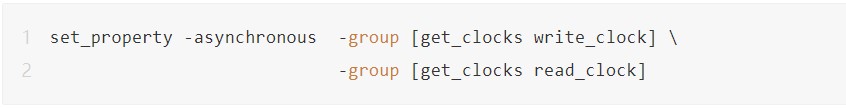

時序約束簡單,進行時序例外約束,只需要 set_clock_groups 將讀寫時鐘約束為異步時鐘組即可,簡單高效。

set_property -asynchronous -group [get_clocks write_clock] \ -group [get_clocks read_clock]

(2)自己寫外部控制邏輯的FIFO

格雷碼做異步 FIFO 的跨時鐘域處理,計數器和讀寫控制邏輯在 BRAM 或者 RAM 的外部,除了代碼的合理設計以外,還需要進行額外的時序例外約束,不能簡單使用 set_clock_groups 約束異步時鐘組,還需要考慮外部的讀寫邏輯的約束。

Xilinx建議這里設置set_max_delay來約束跨時鐘域路徑,約束的原則是:最大路徑延時等于或者略小于目的時鐘的一個周期。

寫邏輯從cell1到cell2的約束中,cell2的驅動時鐘周期為5,如下所示,讀邏輯約束進行相應約束。

多bit中,強烈推薦使用異步FIFO的IP來實現,我在實際工程中使用多次,簡單方便。

set_propertyASYNC_REGTRUE[get_cells[listrst_reg_0rst_reg_1]]

審核編輯:劉清

-

RAM

+關注

關注

8文章

1391瀏覽量

116964 -

fifo

+關注

關注

3文章

400瀏覽量

44670 -

時鐘

+關注

關注

11文章

1887瀏覽量

132939 -

CDC

+關注

關注

0文章

57瀏覽量

18155

原文標題:CDC跨時鐘域處理及相應的時序約束【set_clock_groups】【set_max_delay】

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CDC跨時鐘域分單bit和多bit傳輸介紹

CDC跨時鐘域分單bit和多bit傳輸介紹

評論