異步FIFO常用于跨時鐘域之間的數據傳輸,其可以實現數據的存儲,也可以處理異步時鐘數據傳輸的亞穩態問題。異步FIFO的設計其關鍵點:通過格雷碼對內部讀寫指針進行編碼,然后比較產生空滿標志,以維護FIFO的正常工作。

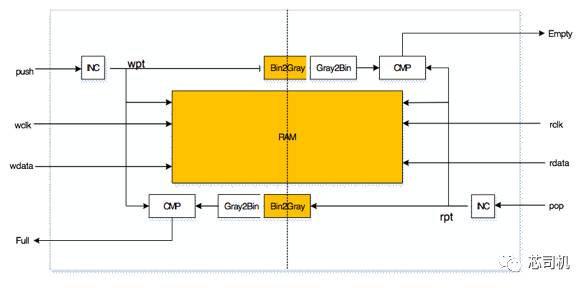

很多人在面試時被問到為什么異步FIFO中需要用到格雷碼,可能大部分的答案是格雷碼可以消除亞穩態。這種回答比較模糊,今天我們就針對這個來深入探討一下。如下圖所示:

Push信息產生的連續寫指針wpt, 通過同步后,在rclk域與rpt進行比較,以產生rclk域的Empty信號。Empty信號用于控制讀操作,以避免在FIFO為空時仍然進行讀操作而導致的錯誤,并影響后續所有的FIFO讀操作。

Pop 信息產生的連續讀指針rpt, 通過同步后,在wclk域與wpt進行比較,以產生wclk域的Full信號。Full信號用于控制寫操作,以避免在FIFO為滿時仍然進行寫操作而導致的錯誤,并影響后續的所有的FIFO寫操作。

異步時鐘產生的亞穩態發生在不同時鐘域信號wpt和rpt的比較上。對于多bit的讀寫指針信號,在跨時鐘域傳輸時會存在bit之前不同延時導致的毛刺,比如寫地址在從0111到1000轉換時4條地址線都會跳變,這樣在寫地址同步到讀時鐘域后得到的寫地址可能是0000-1111的某個值,因此本來wpt = rpt的情況變成了wpt > rpt的情況,本來應該出現空狀態,因為亞穩態導致未被發現,讀操作繼續進行,從而影響了整個FIFO的功能。

我們知道,格雷碼編碼的連續數值之間只有1bit會發生變化,這種特性其實不能消除異步時鐘數據傳輸出現的亞穩態。假設格雷碼編碼的寫地址從001(2)->011(3),讀時鐘域同步出錯,寫地址為001->001,也就是地址沒有跳變,此時用這個錯誤的寫地址與讀地址進行比較,出現虛假的空標志,但這種虛空只是提前阻止了后續的讀操作,不會發生讀空的情況,因此不會影響后續的操作及整個FIFO的功能。

同樣對于讀地址同步到寫時鐘域時也會出現虛滿的情況,這種虛空和虛滿,不會影響FIFO的功能,因此gray碼保證的是在出現亞穩態的情形下,FIFO依然能夠正常的工作。

審核編輯:劉清

-

數據傳輸

+關注

關注

9文章

2010瀏覽量

65855 -

fifo

+關注

關注

3文章

400瀏覽量

44706 -

編碼

+關注

關注

6文章

967瀏覽量

55615

原文標題:異步FIFO-格雷碼

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如果需要使用DMD進行成像控制,需要用到哪些部件?

使用MSVC編譯器重新生成了DLP_SDK,執行Prepare DLP LightCrafter 4500時,生成的兩張格雷碼編碼圖片有問題,為什么?

dlp4500模式序列投射格雷碼,當設置pattern exposure:8333,pattern period為9000時其投射出來的圖案就亂了,為什么?

使用DLPC350投射格雷碼時,當切換pattern頻率>10frame/s,出現了圖像重疊的問題怎么解決?

閘壩工程安全監測中需要用到哪些振弦式傳感器

做的一個系統需要用到4片ADS1298,在多器件聯接方式中,標準模式和菊鏈模式,哪個更換好一些?

如果用ADS129X采集EEG信號,需要用到右腿驅動嗎?

n型焊接頭需要用到哪些材料

ADS9234R這個AD的寄存器如何配置,需要用到哪幾個引腳?

調試音頻放大倍數時,需要用到1khz 0db的正弦波測試音源,請問下這個0db對應的電壓峰峰值的幅度是多少?

在進行高速信號放大設計時,往往需要用到反饋電路,是否反饋電路越短越好?

選擇ths4631后需不需要用jfet呀?

射頻連接器mcx需要用到護線套嗎

為什么異步FIFO中需要用到格雷碼

為什么異步FIFO中需要用到格雷碼

評論