PLC 與“軟件PLC“

早期的PLC 是使用繼電器實(shí)現(xiàn)邏輯控制的。也就是說(shuō),它們完全是硬件實(shí)現(xiàn)的。當(dāng)微處理器出現(xiàn)之后,PLC 內(nèi)部使用了CPU和程序來(lái)實(shí)現(xiàn)控制邏輯。現(xiàn)代PLC中也使用了實(shí)時(shí)操作系統(tǒng)以及各種網(wǎng)絡(luò)協(xié)議。自動(dòng)控制行業(yè)的專(zhuān)家總是將在通用操作系統(tǒng)上運(yùn)行的PLC控制程序成為“軟件PLC”,普遍認(rèn)為軟件PLC 沒(méi)有PLC 設(shè)備可靠,實(shí)時(shí)性沒(méi)有PLC設(shè)備強(qiáng)。

這其實(shí)是一種誤解。某種意義上講,現(xiàn)代的PLC 都是軟件PLC。它們之間的唯一差別是PLC設(shè)備是在特定硬件平臺(tái)上實(shí)現(xiàn)的實(shí)時(shí)操作系統(tǒng)和程序具有更高的實(shí)時(shí)性,確定性和穩(wěn)定性。它們經(jīng)過(guò)了廠(chǎng)商預(yù)先反復(fù)的測(cè)試。確保了軟硬件匹配的的更好。如果重視軟硬件的相互匹配,在通用硬件平臺(tái)上,同樣能夠?qū)崿F(xiàn)可靠運(yùn)行的PLC 系統(tǒng)。比如倍福公司的工業(yè)電腦就是在微軟公司為其定制的windows 下運(yùn)行。同樣非常的可靠。

在實(shí)時(shí)性方面,大多數(shù)PLC 使用實(shí)時(shí)操作系統(tǒng)(RTOS),比如VxWorks OS。這是一個(gè)可靠性,實(shí)時(shí)性極強(qiáng)的實(shí)時(shí)操作系統(tǒng)。不過(guò),RTOS的處理能力也是有限的,設(shè)想編寫(xiě)一個(gè)“巨大”的程序在PLC上運(yùn)行, 也會(huì)出現(xiàn)性能下降問(wèn)題。只是PLC 設(shè)備預(yù)留了足夠的資源來(lái)保證在特定的應(yīng)用中的需要,通俗地講,“就是殺雞用牛刀”。

實(shí)時(shí)操作系統(tǒng)本質(zhì)上是操作系統(tǒng),只是內(nèi)部調(diào)度算法上考慮了對(duì)外部事件的響應(yīng)事件而已。但是令人遺憾的是,幾乎所有的OS 調(diào)度算法都只是“盡力而為”。PLC 的做法是預(yù)留了足夠的硬件算力,來(lái)確保應(yīng)用程序滿(mǎn)足實(shí)時(shí)性的要求。為了提高PLC 的算力,高性能的PLC內(nèi)部采用了FPGA 來(lái)實(shí)現(xiàn)實(shí)時(shí)性要求高的功能,例如產(chǎn)生高速PWM 和脈沖輸出,運(yùn)動(dòng)控制模塊,脈沖計(jì)數(shù),電機(jī)編解碼器等。

開(kāi)放性的挑戰(zhàn)

現(xiàn)代控制系統(tǒng)對(duì)PLC 提出了越來(lái)越高的要求,例如導(dǎo)入更復(fù)雜的控制算法,AI模塊和云端交互功能,它們對(duì)PLC 內(nèi)部CPU/FPGA 提出更高的算力需求,另一方面,控制系統(tǒng)朝著開(kāi)放性方向發(fā)展。第三方開(kāi)發(fā)者和最終用戶(hù)參與PLC 功能塊的開(kāi)發(fā)。在PLC 的生命周期內(nèi)會(huì)變更程序和功能塊升級(jí)。如此一來(lái),PLC廠(chǎng)商其實(shí)能難預(yù)估應(yīng)用程序?qū)λ懔Φ念A(yù)估。并且難以承諾產(chǎn)品的實(shí)時(shí)性。而是又第三方開(kāi)發(fā)者和用戶(hù)能夠更高效地方式來(lái)保證系統(tǒng)的實(shí)時(shí)性能。

IEC61499 的實(shí)時(shí)性

目前大多數(shù)的IEC61499 功能塊和運(yùn)行時(shí)是軟件實(shí)現(xiàn),并且在PC或者Linux 設(shè)備上運(yùn)行。因此IEC61499 目前是一個(gè)典型的“軟”控制器。

問(wèn)題的確是存在的,IEC61499 運(yùn)行時(shí)的實(shí)時(shí)性和確定性的確令人擔(dān)心的。為了解決這個(gè)問(wèn)題,可以吸取PLC 的方式

提高設(shè)備內(nèi)部的SOC算力的富余量

采取FPGA 對(duì)功能塊加速

硬件實(shí)現(xiàn)實(shí)時(shí)功能塊網(wǎng)絡(luò)。

采取FPGA 對(duì)功能塊加速

通過(guò)對(duì)一些對(duì)算力比較大的功能塊使用FPGA 實(shí)現(xiàn),能夠縮短功能塊的執(zhí)行時(shí)間。提高功能塊網(wǎng)絡(luò)的實(shí)時(shí)性。

功能塊內(nèi)部的算法由FPGA IP來(lái)實(shí)現(xiàn)。FB實(shí)現(xiàn)PS/PL 之間的數(shù)據(jù)交換。類(lèi)似的FB包括:

高速PWM 發(fā)生器

高速脈沖計(jì)數(shù)器

FFT 快速傅里葉

數(shù)字濾波器

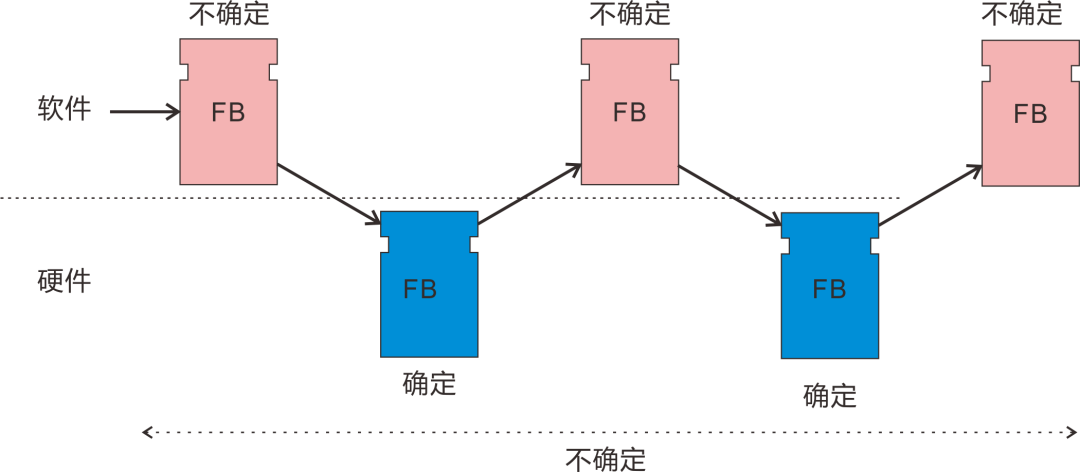

不過(guò)這種方式具有局限性,功能塊之間的數(shù)據(jù)和事件的傳遞和功能塊的調(diào)度仍然是由軟件實(shí)現(xiàn)的,存在著非確定性。對(duì)于像高速電機(jī)控制中,控制環(huán)由多個(gè)功能塊構(gòu)造而成,如果由軟件實(shí)現(xiàn)功能塊之間的數(shù)據(jù)傳遞,整個(gè)系統(tǒng)的實(shí)時(shí)性,確定性難以保證。

硬件實(shí)現(xiàn)實(shí)時(shí)功能塊網(wǎng)絡(luò)

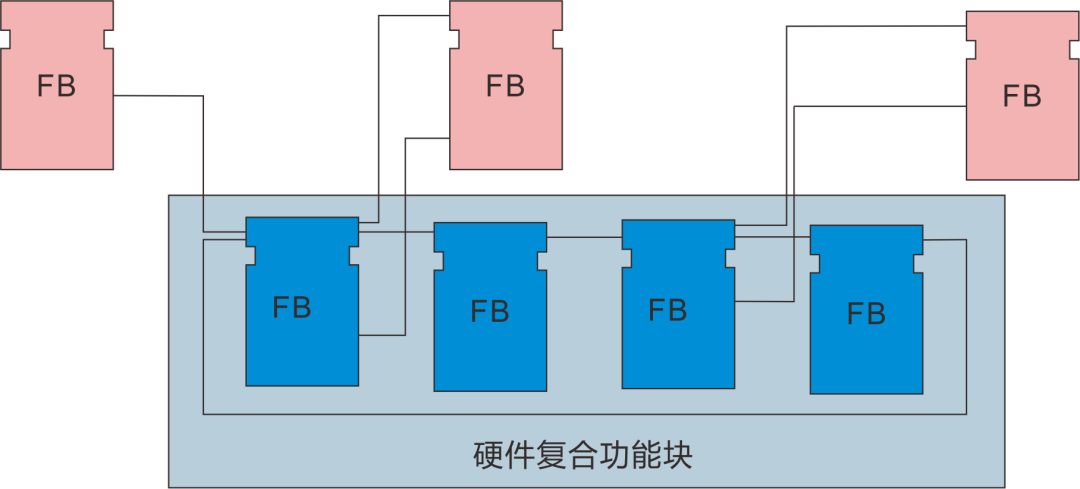

將實(shí)時(shí)處理要求高的一端功能塊網(wǎng)絡(luò)(譬如一個(gè)PID 環(huán)控制)使用FPGA來(lái)實(shí)現(xiàn),而配置,監(jiān)控和事務(wù)交互功能塊仍然由軟件實(shí)現(xiàn)。這樣完整的硬件實(shí)現(xiàn),避免了軟件的干預(yù)而造成不確定性和實(shí)時(shí)性。并且能夠高速地處理控制算法和信號(hào)處理。

某一段功能塊網(wǎng)絡(luò)的硬件實(shí)現(xiàn)最好的方法是將這些硬件功能塊網(wǎng)封裝成為復(fù)合功能塊。通過(guò)工具軟件將這個(gè)復(fù)合功能塊轉(zhuǎn)換成為FPGA 硬件語(yǔ)言(HDL,verilog等)。由FPGA開(kāi)發(fā)工具vivado 轉(zhuǎn)換成FPGA 比特流。

IEC61499 硬件功能塊的實(shí)現(xiàn)

筆者初步開(kāi)始嘗試FPGA 實(shí)現(xiàn)IEC61499 的方法,使用xilinx zynq 作為SOC平臺(tái)。由于IEC61499 并不普及,網(wǎng)絡(luò)上相關(guān)的文章非常少。也只能自己慢慢摸索

在IEC61499 運(yùn)行時(shí)的實(shí)現(xiàn)中,功能塊大多數(shù)采用了C++ 類(lèi)實(shí)現(xiàn),因此我們希望采用HLS 來(lái)實(shí)現(xiàn)C++類(lèi)為基礎(chǔ)的IEC61499 功能塊,但是發(fā)現(xiàn)HLS 幾乎是為復(fù)雜算法而準(zhǔn)備的,使用C++類(lèi)的介紹非常少,如果去實(shí)現(xiàn)與數(shù)字邏輯非常接近的功能塊,好像不如verilog 語(yǔ)言更簡(jiǎn)單。

verilog 語(yǔ)言以module 為一個(gè)編程單元,相當(dāng)于C語(yǔ)言中的一個(gè)函數(shù)(function),但是由于硬件的特殊性,所有的變量都是靜態(tài)分配的,所以與C++的類(lèi)又有幾分相似,內(nèi)部實(shí)現(xiàn)ECC狀態(tài)機(jī)和算法十分方便。與此同時(shí),verlog 的功能塊能夠?qū)嵗T诹硗獾哪K中實(shí)現(xiàn)實(shí)例。與IEC61499 功能塊實(shí)例化十分相像。使用verilog 語(yǔ)言編寫(xiě)IEC61499 硬件功能塊更加合適。

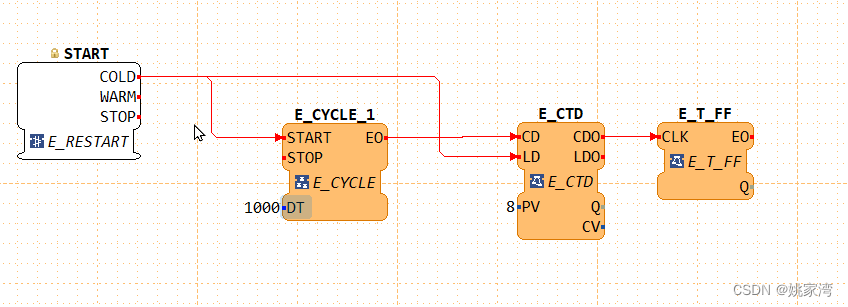

例子1-E_CTD 功能塊

下面是筆者使用verilog 實(shí)現(xiàn)的一個(gè)E_CTD 計(jì)數(shù)器

`timescale 10ns / 1ns module e_ctd(cd,ld,cdo,ldo,pv,cv,q); input cd,ld; input [15:0] pv; output reg q,cdo,ldo; output reg [15:0] cv; reg [15:0] v; always@(posedge cd) begin if (cv==0)begin cv <= v; ? ? ? ? ? #5 q=1; ? ? ? ? ? end else ? ? ? ? ? begin ? ? ? ? ? ? cv <= cv - 1; ? ? ? ? ? #5 q=0; ? ? ? ? ? end ? ? ? #5 cdo=1; ? ? ? #5 cdo=0; ? end ? always@(posedge ld) ? begin ? ? ? v <= pv; ? ? ? cv <= pv; ? ? ? ldo=1; ? ? ? #10 ldo=0; ? end endmodule

在上面的程序中,忽略了ECC 的實(shí)現(xiàn)。module e_ctd是功能塊,下面的test 是仿真程序

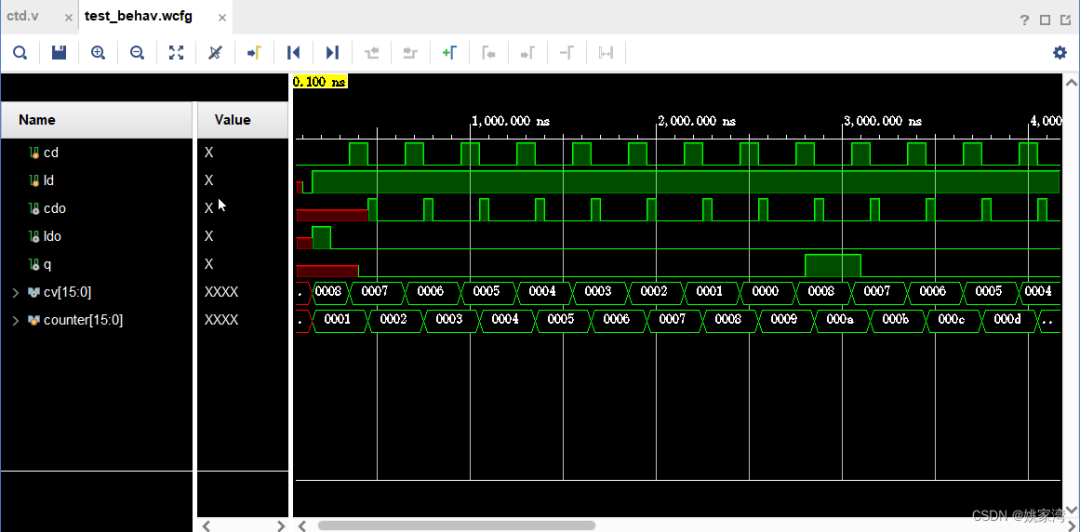

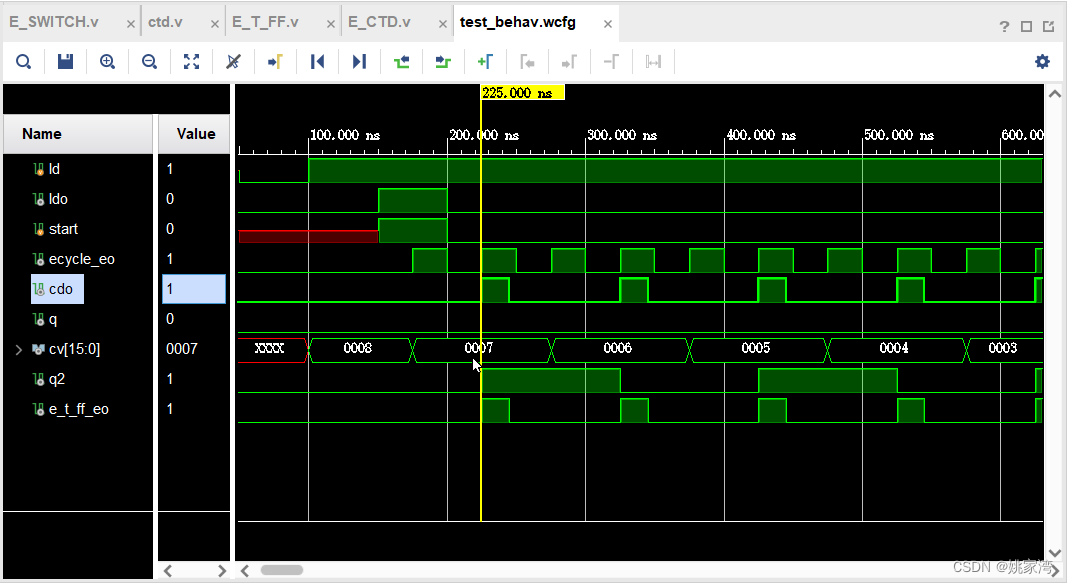

仿真的結(jié)果

IEC61499 基本功能塊都是底層邏輯構(gòu)建得,使用verilog 語(yǔ)言描寫(xiě)非常合適,如果要深入研究IEC61499 功能塊硬件化得課題,需要開(kāi)發(fā) hardware function block 庫(kù)。在這個(gè)基礎(chǔ)上開(kāi)發(fā)一些構(gòu)建工具(XML->verilog)

例2 -E_CYCLE 功能塊

`timescale 10ns / 1ns module e_cycle(start,stop,eo); input start,stop; output reg eo; parameter FREQ = 100000; // in constraint_mode parameter DUTY = 50; // in percentage parameter clk_pd = 1.0/(FREQ * 1e3) * 1e9; parameter clk_on = DUTY/100.0 * clk_pd; parameter clk_off = (100.0 - DUTY)/100.0 * clk_pd; reg start_clk; initial begin eo <= 0; ? start_clk <= 0; end always @(posedge start) begin ? if (start) ? ? start_clk=1; end ? always @(posedge stop) begin ? if (stop) ? ? start_clk=0; end ? ? always @(posedge start_clk) begin if (start_clk) begin while (start_clk) begin ? ? #(clk_on) eo=1; ? ? #(clk_off) eo=0; ? ? ? ? end ? ? ? ? end end ? endmodule

例3 -E_T_FF

`timescale 10ns / 1ns

module E_T_FF(clk,eo,q);

input clk;

output reg eo,q;

initial

begin

q=0;

eo=0;

end

always @(posedge clk) begin

if (clk)

begin

q <=~q;

? ? eo=1;

? ? #2 eo=0;

? ? end

end

endmodule

測(cè)試程序

測(cè)試程序完成IEC61499 功能塊網(wǎng)絡(luò)。

`timescale 10ns / 1ns

module test();

reg cd,ld;

wire cdo,ldo,q,q2;

wire [15:0] cv;

wire ecycle_eo,e_t_ff_eo;

reg start,stop;

E_CYCLE #(.FREQ(200000)) ecycle1(start,stop,ecycle_eo);

E_CTD #(.PV(8)) etcd1(ecycle_eo,ld,cdo,ldo,cv,q);

E_T_FF e_t_ff(cdo,e_t_ff_eo,q2);

initial

begin

#5 ld =0;

#5 ld=1;

#5 start=1;

#5 start=0;

end

initial

$monitor("at time %t ,",$time,"CDO=%b,LDO=%b,Q=%b,CV=%b",ecycle_eo,ldo, q,q2);

endmodule

仿真結(jié)果

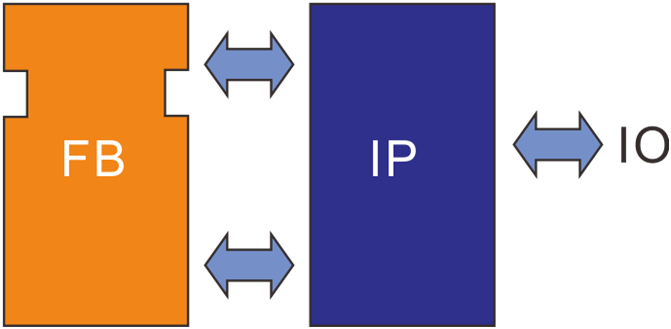

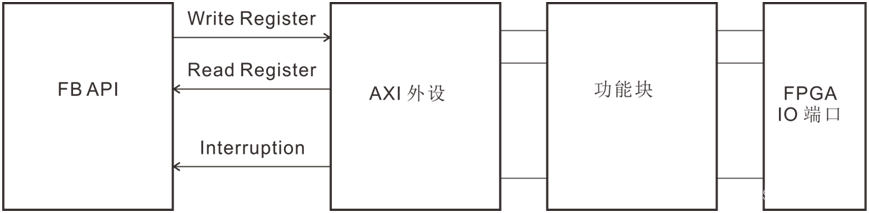

軟硬件接口

實(shí)現(xiàn)IEC61499 硬件功能塊,需要設(shè)計(jì)一個(gè)統(tǒng)一的軟硬件接口。如下圖所示。

IEC61499 運(yùn)行時(shí)通過(guò)HFB API 訪(fǎng)問(wèn)硬件功能塊

API 包括:

Event_Action() 向硬件FB 發(fā)送事件

Put_Data 向FB 發(fā)送數(shù)據(jù)

Get_Data讀取FB數(shù)據(jù)

Event_Notify() 處理FB 輸出的事件中斷。(也可以是查詢(xún)方式)

ARM 處理器通過(guò)AXI-lite 接口與PL 端的AXI 外設(shè)IP 通信

write Register

readRegister

interrupt processing

AXI 外設(shè)寄存器

輸入事件寄存器(Input Event register)

輸出事件寄存器(Output Event register)

輸入數(shù)據(jù)寄存器(Input Data Register)

輸出數(shù)據(jù)寄存器(Output Data Register)

操作過(guò)程

事件輸入

當(dāng)需要向功能塊注入事件時(shí),運(yùn)行時(shí)向輸入事件寄存器對(duì)應(yīng)的bit 位置 1,硬件FB 檢測(cè)輸入事件寄存器的狀態(tài),一旦發(fā)現(xiàn)變化,轉(zhuǎn)向事件處理。完成后,清除對(duì)應(yīng)的狀態(tài)位。

事件輸出

當(dāng)功能塊輸出一個(gè)事件時(shí),在輸出事件寄存器相關(guān)位置1,并產(chǎn)生一個(gè)中斷信號(hào)。由運(yùn)行時(shí)軟件讀取事件寄存器,并且清零。

數(shù)據(jù)輸入/輸出

由軟件直接寫(xiě)入或讀取數(shù)據(jù)輸入寄存器。這一點(diǎn)與軟件實(shí)現(xiàn)有所不同,軟件FB 處理時(shí)是通過(guò) getDataIn根據(jù)connection 去數(shù)據(jù)源功能塊中讀取的。對(duì)于硬件FB,當(dāng)事件來(lái)臨時(shí),API要根據(jù)事件-數(shù)據(jù)關(guān)聯(lián)性,調(diào)用getDataIn 讀取數(shù)據(jù)后需要寫(xiě)入數(shù)據(jù)輸入寄存器中。

結(jié)束語(yǔ)

這只是一個(gè)開(kāi)頭,還有許多工作要做

1 軟件功能塊與硬件功能塊的接口的實(shí)現(xiàn)方式

2 如何將IEC61499 復(fù)合功能塊的XML 描述轉(zhuǎn)換成verilog 的模塊。

3 如何調(diào)用HLS 產(chǎn)生的IP

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614257 -

PLC控制

+關(guān)注

關(guān)注

9文章

253瀏覽量

27831 -

編解碼器

+關(guān)注

關(guān)注

0文章

272瀏覽量

24650 -

RTOS

+關(guān)注

關(guān)注

24文章

841瀏覽量

120780

原文標(biāo)題:IEC61499 在FPGA中的實(shí)現(xiàn)

文章出處:【微信號(hào):ZYNQ,微信公眾號(hào):ZYNQ】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

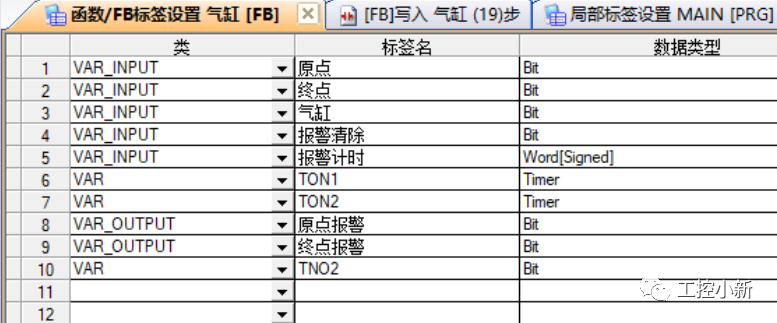

什么是FB功能塊?為什么要使用FB功能塊?如何制作一個(gè)FB功能塊?

資料下載:從PLC 到IEC61499 控制器

漫談工業(yè)軟件IEC61499 功能塊

基于IEC61131的PLC和IEC61499兼容型控制器之間有何差別

IEC 61499是什么

容器技術(shù)和IEC61499在智能制造系統(tǒng)中有何應(yīng)用

基于FF現(xiàn)場(chǎng)總線(xiàn)的先進(jìn)PID功能塊設(shè)計(jì)

基于EPA的PID功能塊的設(shè)計(jì)及實(shí)現(xiàn)

騰控MODBUS主站功能塊通迅詳解

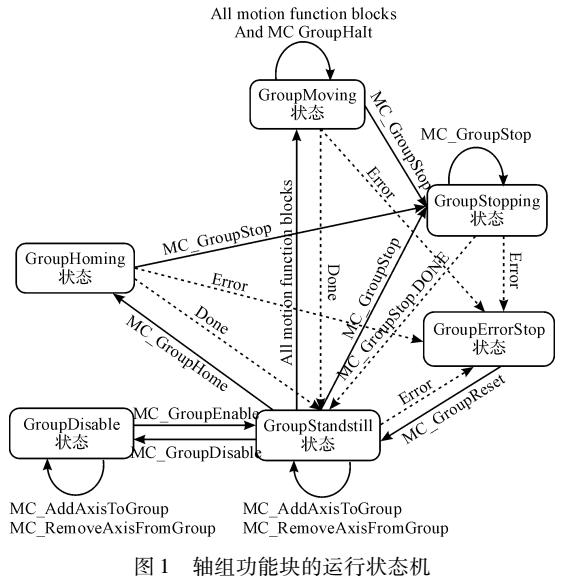

PLCopen軸組運(yùn)動(dòng)功能塊研究

采取FPGA對(duì)IEC61499的功能塊進(jìn)行加速

采取FPGA對(duì)IEC61499的功能塊進(jìn)行加速

評(píng)論