設計組有個小伙子叫小博,入職剛滿一年,今天收到了公司發來的暖心郵件。

他卻高興不起來,因為昨晚收到了一封電源仿真結果的郵件:自己獨立接手的第一個設計任務,到了投板的節骨眼,直流壓降有問題。

正可謂:

曾因壓降夜難寐,猶為阻抗困愁城。

世間無限丹青手,一片憂心畫不成。

小博一夜難眠,一大早就來求助高速先生。

看著小博急切又期待的眼神,高速先生認真查了下板,最后給出的建議是,問題不大,不改平面不加層,動動走線就能行。小博半信半疑……

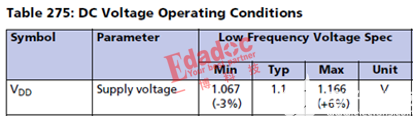

電源的直流壓降,作為衡量電源性能的一個重要指標,用電芯片端的要求通常會以電壓百分比的方式給出,例如下表的DDR5的VDD,直流壓降要求為-3%~+6%

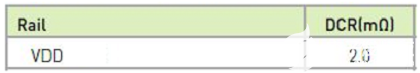

不過,越來越多的芯片手冊直接對電源路徑的直流電阻提出要求,以DCR(Direct Current Resistance)阻值的形式給出。

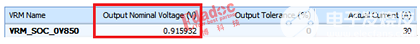

再來看看小博遇到的這個電源,電源電壓0.85V,用電芯片端的壓降要求:-1%~-+1%.

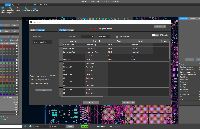

原設計文件的仿真結果如下:VRM輸出916mV,到達用電芯片的電壓為833mV,不滿足壓降要求。

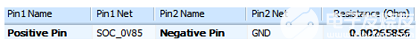

此時,電源DCR為2.66mΩ。

按照高速先生的建議,微調走線后,用電芯片的電壓增加至846mV。

結果竟然達標了!小博驚掉了下巴,這……

電源DCR卻保持不變,仍然是2.66mΩ

修改前后的電源通道完全沒有變化,電源DCR均為2.66mΩ,可是用電芯片端的電壓怎么就神奇的抬起來了呢?玄機就在電源輸出的變化。

修改前,VRM輸出916 mV。

修改后,VRM輸出增加至929mV。

VRM輸出電平抬高,電源路徑壓降不變,用電芯片端的電壓可不就水漲船高嘛。

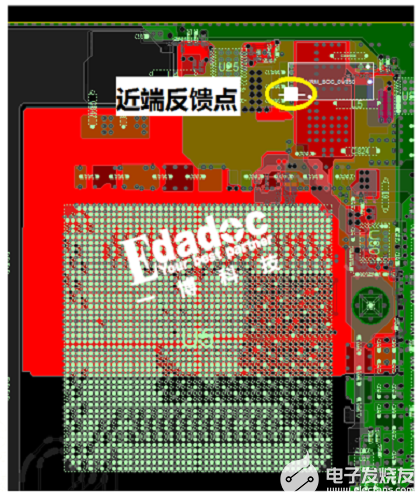

有經驗的Layout攻城獅應該已經猜到了小博的問題出在哪了。

沒錯,由于經驗不足,小博原設計的電壓反饋點設置在了近端,太靠近VRM。

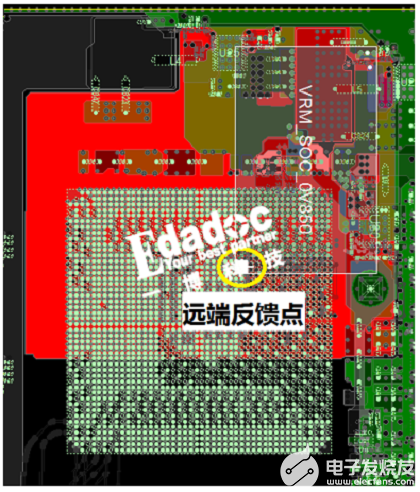

為了抬高VRM的輸出電平,高速先生建議將反饋點調整至遠端,修改后的版本如下,靠近了用電芯片:

僅通過調整VRM的電壓反饋走線,不涉及電源平面和層疊的修改,就能讓用電芯片的電壓滿足要求,簡直是懶人福音,不過,前提是VRM有電壓反饋的功能,而且,電壓輸出調整幅度也有一定的范圍,不能任性。

與電壓百分比的方式相比,有些芯片手冊對電源DCR提出要求也有它的道理,它可以更加直接的反映電源通道本身的參數。作為電源通道的重要組成部分,電源平面可以視為方塊電阻,而方塊電阻的阻值與面積和厚度有關,因此,DCR的大小也與銅皮的有效面積和厚度有關系。

這里可以再做個仿真對比,說明DCR的變化對電源的影響。還是使用上面的仿真文件,為了簡化問題,刪除了電壓反饋線,VRM輸出電壓將保持為0.85V,對比不同銅厚帶來的變化。按照當前的電源平面和層疊設置,直流壓降仿真結果如下:

因為通道沒有變化,電源路徑直流壓降仍然是83mV,電源DCR也保持不變,2.66mΩ。

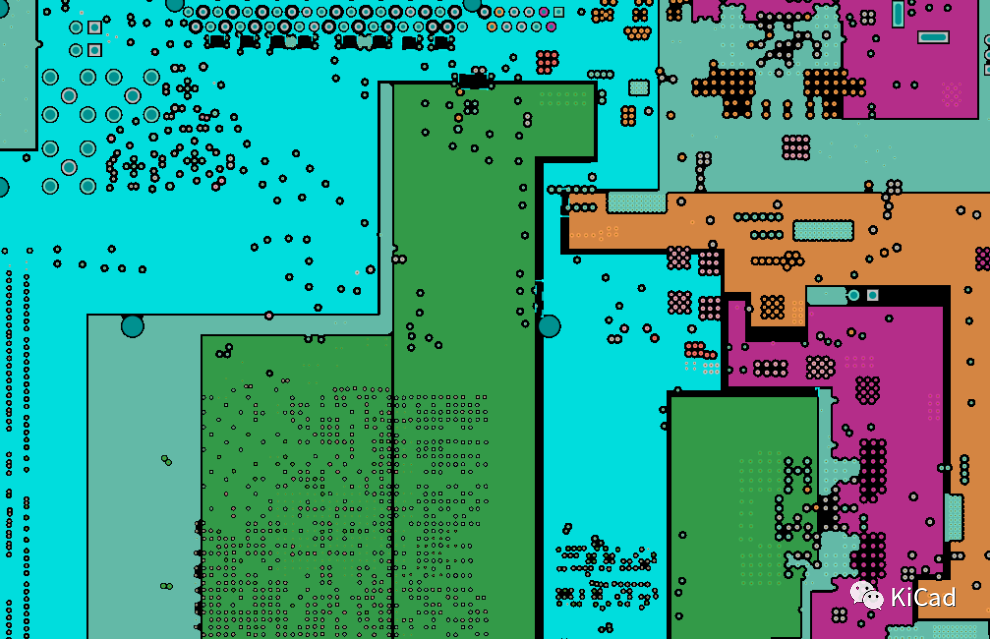

我們把電源平面的銅厚由1oz增加到2oz,其它不變,再來看看仿真結果:

由于電源平面的銅厚增加,電源DCR由2.66mΩ減小到2.48mΩ,直流壓降也從83mV降低至76mV。由此可見,電源通道本身的優化確實可以減小DCR,進而改善壓降。

經驗豐富的攻城獅都知道,在單板設計后期改動電源通道耗時費力,因此根據壓降和通流要求提前規劃電源就顯得格外重要。當然了,走彎路也是學習的一種方式,雖然效率不是最高的,但是,一定是記憶最深刻的,小博應該深有感觸。

審核編輯:湯梓紅

-

電源

+關注

關注

185文章

18313瀏覽量

255414 -

芯片

+關注

關注

459文章

52308瀏覽量

437810 -

直流電阻

+關注

關注

1文章

161瀏覽量

15141

發布評論請先 登錄

PCB的EMC設計(一):層的設置與排布原則

PCB走線,盲目拉線,拉了也是白拉!

DAC161S055在上電后不加任何時序操作,Vout是否輸出上電值引腳(MZB)所接的電平值?

DAC161S055在上電后不加任何時序操作,Vout是否輸出上電值引腳(MZB)所接的電平值?

帶屏蔽層的網線怎么接

【「基于大模型的RAG應用開發與優化」閱讀體驗】+大模型微調技術解讀

KiCad中如何分割電源平面

技術資訊 I 如何使用 Allegro X PCB Editor 優化RF布線和阻抗

不改平面不加層,微調走線抬電平

不改平面不加層,微調走線抬電平

評論