在談 RISC-V 之前,我們先梳理幾個概念:

1. 芯片

芯片 是所有半導體元器件的統稱,它是把一定數量的常用電子元件(如電阻,電容,晶體管等),通過半導體工藝集成在一起,具有特定功能的電路。

2. CPU

cpu 是芯片的一種,它里面包含了控制部件和運算部件,即中央處理器。1971 年, Intel 將運算器和控制器集成到一個芯片上,稱為4004 微處理器,這標志著CPU 的誕生。

CPU 的工作流程分為以下5個階段:

取指令

指令譯碼

執行指令

訪存讀取數據

結果寫回

指令和數據統一存儲在內存中,數據與指令需要從統一的存儲空間存取,經由共同的總線傳輸,無法并行讀取數據和指令。馮諾依曼結構

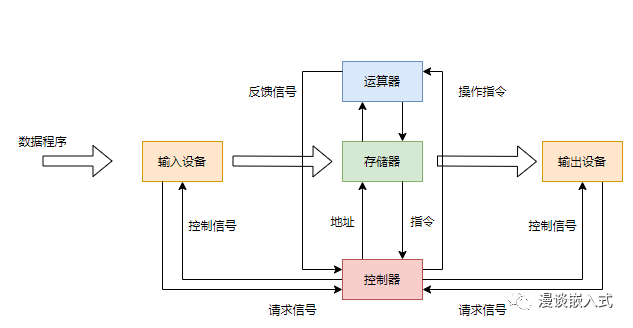

3. 馮諾依曼結構

馮·諾依曼結構也稱普林斯頓結構,是一種將程序指令存儲器和數據存儲器合并在一起的存儲器結構。

程序指令存儲地址和數據存儲地址指向同一個存儲器的不同物理位置,因此程序指令和數據的寬度相同,如英特爾公司的8086中央處理器的程序指令和數據都是16位寬。

數學家馮·諾依曼提出了計算機制造的三個基本原則,即采用二進制邏輯、程序存儲執行以及計算機由五個部分組成:

運算器

控制器

存儲器

輸入設備

輸出設備

現代計算機發展所遵循的基本結構形式始終是馮·諾依曼機結構。這種結構特點是“程序存儲,共享數據,順序執行”,需要 CPU 從存儲器取出指令和數據進行相應的計算

(1)單處理機結構,機器以運算器為中心;

(2)采用程序存儲思想;

(3)指令和數據一樣可以參與運算;

(4) 數據以二進制表示;

(5)將軟件和硬件完全分離;

(6) 指令由操作碼和操作數組成;

(7)指令順序執行。

這套理論被稱為馮·諾依曼體系結構。

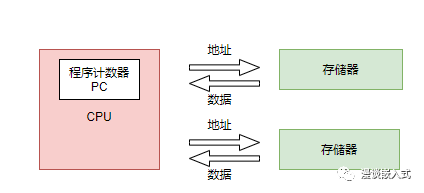

4. 哈佛結構

哈佛結構是一種將程序指令存儲和數據存儲分開的存儲器結構,如下圖所示。中央處理器首先到程序指令存儲器中讀取程序指令內容,解碼后得到數據地址,再到相應的數據存儲器中讀取數據,并進行下一步的操作(通常是執行)。

程序指令存儲和數據存儲分開,可以使指令和數據有不同的數據寬度,如Microchip公司的PIC16芯片的程序指令是14位寬度,而數據是8位寬度。

哈佛結構的微處理器通常具有較高的執行效率。其程序指令和數據指令分開組織和存儲的,執行時可以預先讀取下一條指令。

哈佛結構是指程序和數據空間獨立的體系結構, 目的是為了減輕程序運行時的訪存瓶頸。

哈佛結構能基本上解決取指和取數的沖突問題。

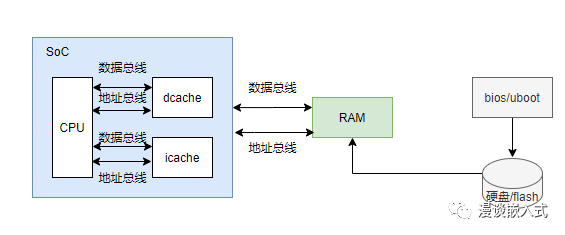

5. 混合式結構

使用兩個獨立的存儲器模塊,分別存儲指令和數據,每個存儲模塊都不允許指令和數據并存;

具有一條獨立的地址總線和一條獨立的數據總線,利用公用地址總線訪問兩個存儲模塊(程序存儲模塊和數據存儲模塊),公用數據總線則被用來完成程序存儲模塊或數據存儲模塊與CPU之間的數據傳輸;

兩條總線由程序存儲器和數據存儲器分時共用。

6. CISC

從前面的內容中,我們已經得知 CPU 就是不斷的執行指令,來實現程序的執行,最后實現相應的功能。但是一顆CPU 能實現多少條指令,每條指令完成多少功能,卻是值得細細考量的問題。

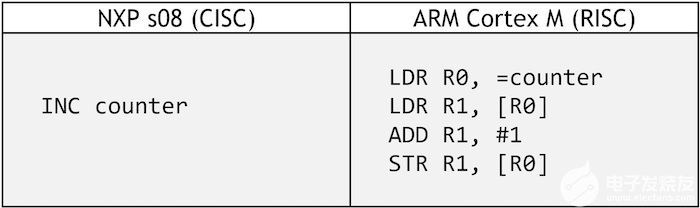

CISC的英文全稱為“Complex InstrucTIon Set Computer”,即“復雜指令系統計算機”,從計算機誕生以來,人們一直沿用CISC指令集方式。早期的桌面軟件是按CISC設計的,并一直沿續到現在。目前,桌面計算機流行的x86體系結構即使用CISC。

CISC 的優勢在于,用少量的指令就能實現非常多的功能,程序自身大小也會下降,減少內存空間占用。

缺點:這些復雜指令集,包含的指令數量多且功能復雜,設計復雜。

7. RISC

RISC的英文全稱為“Reduced InstrucTIon Set Computer”,即“精簡指令集計算機”,是一種執行較少類型計算機指令的微處理器,起源于80年代的MIPS主機(即RISC機),RISC機中采用的微處理器統稱RISC處理器。

這樣一來,它能夠以更快的速度執行操作(每秒執行更多百萬條指令,即MIPS)。因為計算機執行每個指令類型都需要額外的晶體管和電路元件,計算機指令集越大就會使微處理器更復雜,執行操作也會更慢。

RISC 設計方案非常簡約,通常有20 多條簡化的指令集。每條指令長度固定,由專用的加載和儲存指令用于訪問內存,減少了內存的尋址方式,大多數運算指令只能訪問操作寄存器。

CPU 中配有大量的寄存器,這些指令的選取都是工程中使用頻率最高的指令。由于指令長度一致,功能單一,操作依賴于寄存器,這些特性使得CPU 指令預取、分支預測、指令流水線等部件的效能大大發揮,幾乎一個時鐘周期能執行多條指令

RISC 的代表產品是 ARM 和 RISC-V。現在,兩者已經沒有明顯的界限了,開始相互融合了

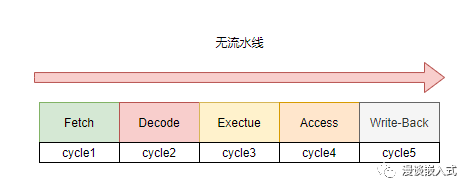

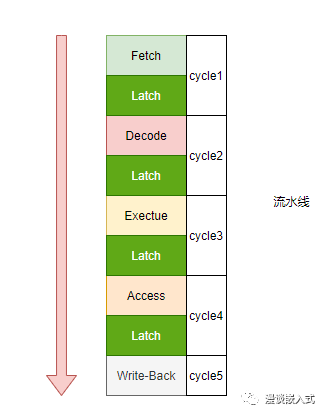

8. 流水線

談到指令并行,就不得不談到CPU 核心的流水線。現代處理器都是流水線結構。

流水線(Pipeline)技術是指程序在執行時候多條指令重疊進行操作的一種準并行處理實現技術。通俗的講將一個時序過程,分解成若干個子過程,每個過程都能有效的與其他子過程同時執行。這種思想最初是在RISC的架構中出現的,旨在提高處理器處理效率,爭取在一個時鐘周期中完成一條指令。

一般常見的5級流水線有:

取指:指令取指(Instruction Fetch)是指將指令從存儲器中讀取出來的過程。

譯碼:指令譯碼(Instruction Decode)是指將存儲器中取出的指令進行翻譯的過程。經過譯碼之后得到指令需要的操作數寄存器索引,可以使用此索引從通用寄存器組(Register File)中將操作數讀出。

執行:指令譯碼之后所需要進行的計算類型都已得知,并且已經從通用寄存器組中讀取出了所需的操作數,那么接下來便進行指令執行(Instruction Execute)。指令執行是指對指令進行真正運算的過程。譬如,如果指令是一條加法運算指令,則對操作數進行加法操作;如果是減法運算指令,則進行減法操作。在“執行”階段的最常見部件為算術邏輯部件運算器(Arithmetic Logical Unit,ALU),作為實施具體運算的硬件功能單元。

訪存:存儲器訪問指令往往是指令集中最重要的指令類型之一,訪存(Memory Access)是指存儲器訪問指令將數據從存儲器中讀出,或者寫入存儲器的過程。

寫回:寫回(Write-Back)是指將指令執行的結果寫回通用寄存器組的過程。如果是普通運算指令,該結果值來自于“執行”階段計算的結果;如果是存儲器讀指令,該結果來自于“訪存”階段從存儲器中讀取出來的數據。

無流水線:

有流水線:

它增加了四組寄存器,每一個流水線級數內部都有各自的組合邏輯數據通路,彼此之間沒有復用資源,因此,其面積開銷是比較大的,但是由于可以讓不同的流水線級數同時做不同的事情,而達到流水的效果,提高了性能,優化了時序,增加了吞吐率。

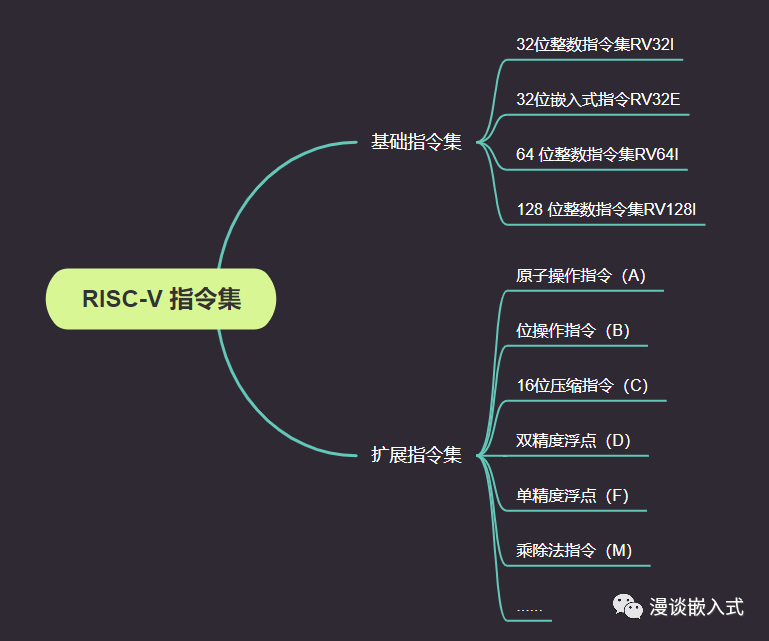

9. RISC-V

在了解了 RISC 和 CISC 兩種計算機指令設計架構后。我們來看看 RISC-V。

RISC-V 的 “V”, 有兩層意思,一方面代表第5代 RISC;另一方面, “V”取Variation 之意代表變化。

9.1 RISC-V 是什么?

RISC-V 是一套開放許可證書、免費的、由基金維護的、一個整數運算指令集外加多個擴展指令集的CPU 結構規范(ISA)。

整數運算指令集 + 擴展指令集

任何硬件開發商或者組織都可以免費使用這套規范,構建CPU 芯片產品。

9.2 指令集命名方式

以RV 為2前綴,然后是位寬,最后代表是指令集的字母集合:

RV[###][abc......xyz]

| 符號 | 說明 |

|---|---|

| RV | RISC-V 縮寫 |

| [###] | 用于標識處理器位寬,取值[32, 64,128],也就是處理器的寄存器位寬 |

| [abc...xyz] | 標識該處理器支持的指令模塊集合 |

比如:RV64IMAC, 表示64 位 RISC-V, 支持整數指令、乘除法指令、原子指令和壓縮指令。

9.3 指令集模塊

指令集模塊是一款CPU架構的主要組成部分,是CPU 和 上層軟件交互的核心,也是cpu主要功能體現。

RISC-V 規范只定義了CPU 需要包含的基礎整型操作指令:

整型的儲存

加載

加減

邏輯

移位

分支

等。

其他指令為可選指令或者用戶擴展指令。比如:

乘

除

取模

單精度浮點

雙精度浮點

壓縮

原子指令

等。

擴展指令是芯片工程師根據需求自定義。

所以 RISC-V 采用的是模塊化的指令集,易于擴展、組裝。它適用于不同的應用場景,可以降低 CPU 實現成本。

9.4 RISC-V 寄存器

指令的操作數來源于寄存器,精簡指令架構的CPU,都會提供大量的寄存器。

RISC-V 的規范定義了32個通用寄存器以及一個PC寄存器,這對于RV32I、RV64I、RV128I 指令集都是一樣的,只是寄存器的位寬不一樣。

如果要實現支持F/D擴展指令集的CPU,則需要額外支持32個浮點寄存器。而如果實現只支持RV32E指令集的嵌入式CPU,則可以將32個通用寄存器縮減為16個通用寄存器。

| 寄存器 | ABI 名稱 | 說明 |

|---|---|---|

| x0 | zero | 0值寄存器,硬編碼為0,寫入數據忽略,讀取數據為0 |

| x1 | ra | 用于返回地址(return address) |

| x2 | sp | 用于棧指針(stack pointer) |

| x3 | gp | 用于通用指針 (global pointer) |

| x4 | tp | 用于線程指針 (thread pointer) |

| x5 | t0 | 用于存放臨時數據或者備用鏈接寄存器 |

| x6~x7 | t1~t2 | 用于存放臨時數據寄存器 |

| x8 | s0/fp | 需要保存的寄存器或者幀指針寄存器 |

| x9 | s1 | 需要保存的寄存器 |

| x10~x11 | a0~a1 | 函數傳遞參數寄存器或者函數返回值寄存器 |

| x12~x17 | a2~a7 | 函數傳遞參數寄存器 |

| x18~x27 | s2-s11 | 需要保存的寄存器 |

| x28~x31 | t3~t6 | 用于存放臨時數據寄存器 |

ABI: 應用程序二進制接口,可以理解為寄存器別名,高級語言在生成匯編會用到。

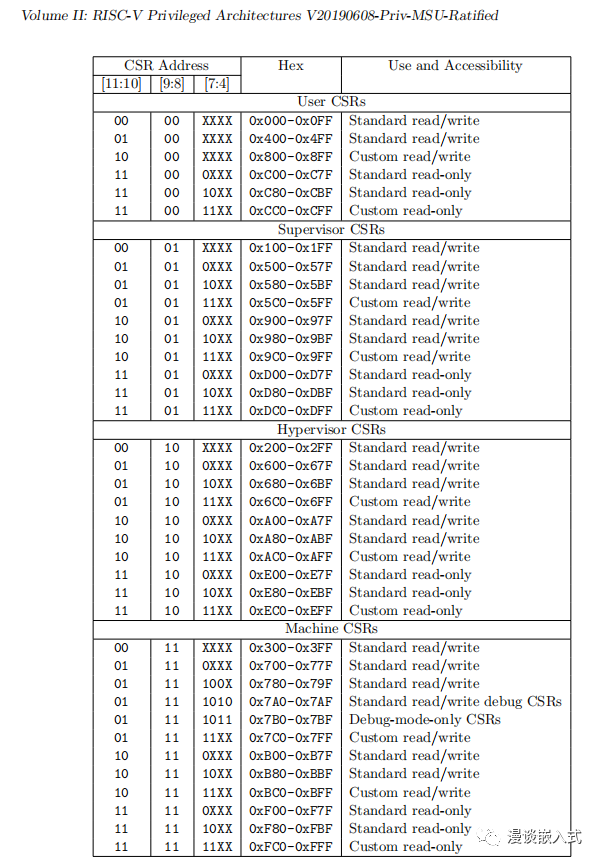

9.5 RSIC-V 特權級

不同的 指令集架構都有特權級的概念,RSIC-V 也不例外,我們來看看RISC-V 的特權級。

不同的特權級能訪問的系統資源不同,高特權級的能訪問低特權級的資源,反之卻不行。

RISC-V 的規范文檔定義了四個特權級別(privilege level),特權等級由高到低排列,如下表所示。

| 名稱 | 級別 | 縮寫 | 編碼 |

|---|---|---|---|

| 用戶,應用程序特權級 | 0 | U | 00 |

| 管理員特權級 | 1 | S | 01 |

| 虛擬機監視特權級 | 2 | H | 10 |

| 機器特權級 | 3 | M | 11 |

一個RISC-V 硬件線程(hart),相當于一個CPU 內獨立的可執行核心,在任意時刻,只能運行在某一個特權級上,這個特權級由CSR(控制和狀態寄存器)指定配置。

具體分級如下:

機器特權級(M):RISC-V 中 hart 可以執行的最高權限模式。在M 模式下運行的 hart,對內存、I/O 和一些必要的底層功能(啟動和系統配置)有著完全的控制權。它是唯一一個所有標準RISC-V CPU 都必須實現的權限級。

虛擬機監視特權級(H):為了支持虛擬機監視器而定義的特權級。

管理員特權級(S):主要用于支持現代操作系統,如Linux、FreeBSD和 windows 等

用戶應用特權級(U):用于運行應用程序,同樣也適用于嵌入式系統。

特權級的存在,是給指令加上了權力,從而去控制指令編寫應用程序。應用程序只能干應用程序該干的事情,不能越權操作。操作系統則擁有更高的權力,能對系統資源進行管理。

10. 總結

本文梳理了 芯片、CPU、流水線,指令與架構等基礎概念,引出了RISC-V 基礎介紹,簡單介紹了RISC-V 由來。后續針對risc-v 會根據自身學習情況做相應介紹。

審核編輯:劉清

-

控制器

+關注

關注

114文章

17113瀏覽量

184386 -

晶體管

+關注

關注

77文章

10020瀏覽量

141754 -

運算器

+關注

關注

1文章

164瀏覽量

16809 -

RISC-V

+關注

關注

46文章

2574瀏覽量

48855

原文標題:適合新手的RISC-V入門基礎知識

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IC設計工程師想了解的RISC-V知識點分享

RISC-V入門:模塊化開放式的ISA CISC和RISC代碼區別

關于RISC-V學習路線圖推薦

RISC-V單片機快速入門01-開發環境搭建 相關資料下載

如何入門RISC-V嵌入式

RISC-V基礎知識:模塊化開放式的ISA CISC和RISC代碼區別

適合新手的RISC-V入門基礎知識

初探RISC-V—《RISC-V體系結構編程與實踐》

適合C語言小白看的基礎知識梳理總結

RISC-V如何填補CPU知識空白

關于risc-v啟動部分的思考

從零開始寫RISC-V處理器

RISC-V 簡介——理解 RISC 的開放式 ISA

RISC-V入門基礎知識梳理

RISC-V入門基礎知識梳理

評論