最近產品類文章寫得偏多,回歸下技術文章,最近有朋友在問:

沒有qrcTechfile文件,用captable可以不?

沒有指定process node可以不?

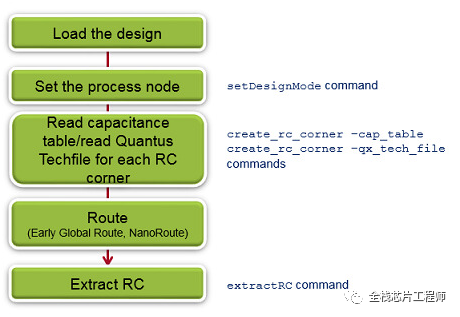

先看第二問題,為什么要設置process node:

例:setDesignMode -process 40

setDesignMode [-help] [-reset] [-addPhysicalCell {hier | flat}] [-congEffort {low|medium|high|auto}] [-dual_rail_via_pitch min_via_pitch min_filler_via_pitch cell_boundary_spacing] [-earlyClockFlow {true|false}] [-expressRoute {true|false}] [-flowEffort {express|standard|extreme}] [-ignore_followpin_vias {true|false}] [-pessimisticMode {true|false}] [-powerEffort {none|low|high}] [-process integer] [-slackWeighting {unityWeighting|viewBasedWeighting}]

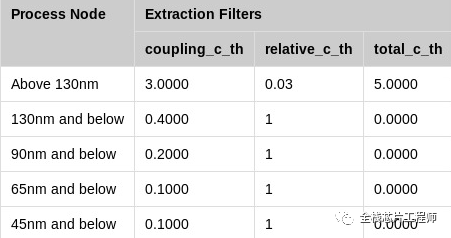

隨著先進工藝已經進入到3nm階段,EDA工具對Delay計算的準確度變得十分具有挑戰性,Cadence設置如下表參數,通過setDesignMode -process 40可以直接全局配置Cadence相關參數為40nm模式,增強避免多次配置,同時提高了RC提取精度。

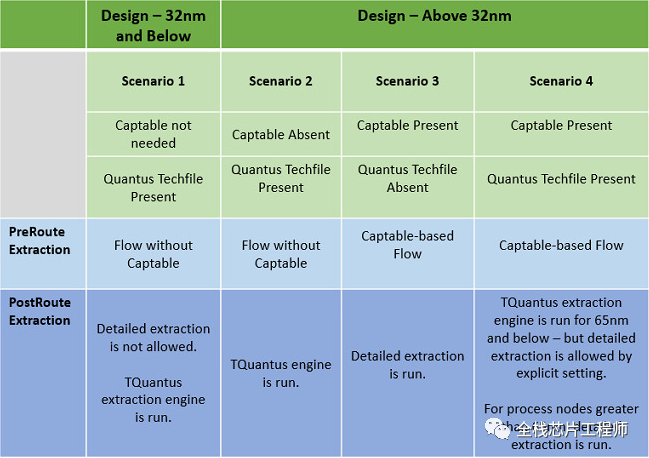

再看第1個問題。沒有qrcTechfile文件,用captable可以不?

32nm及以上工藝,要么用qrcTechfile文件,要么用captable。

若qrcTechfile和captable都沒有,Innovus會利用默認工藝參數生成一個captable,但精度會差很多。

32nm及以下更先進工藝則必須要qrcTechfile。

每個tech corner都需要一個對應的captable/qrcTechfile

審核編輯:劉清

-

EDA工具

+關注

關注

4文章

273瀏覽量

32784 -

Cadence

+關注

關注

67文章

971瀏覽量

144202

原文標題:RC抽取工藝文件

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請問node怎么設置不被特定的provision配網?

請問ble_mesh的node和node之間是否要定義協議通訊?

node怎么設置不被特定的provision配網?

Elasticsearch底層模塊:如何去規劃和配置各種各樣的node

搭建Node-RED環境,將開發板變身為工業控制網關——米爾基于NXP LS1028A開發板

Node-RED如何制作漂亮的界面

為什么要設置process node

為什么要設置process node

評論