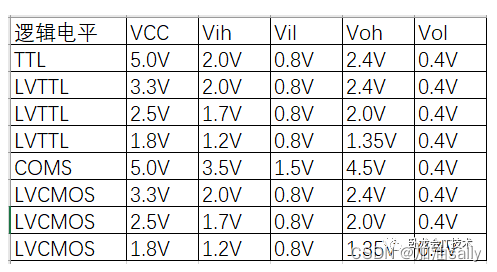

電路設(shè)計(jì)中,經(jīng)常遇到各種不相同的邏輯電平。常見(jiàn)的邏輯電平如下:

TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,還有一些速度比較高的 LVDS、GTL、PGTL、CML、HSTL、SSTL等。

TTL電平

TTL:Transistor-Transistor Logic 三極管結(jié)構(gòu)。TTL電平常用的一般分為2種,分別是3.3V和5V,不論是3.3V還是5V的TTL的VIH/VIL與VOH/VOL都是一樣的,輸入的高低電平VIH/VIL一般是2V/0.8V,輸出的高低電平VOH/VOL一般是 2.4V/0.4V,也就是 輸出:VOH>=2.4V;VOL<=0.5V;輸入:VIH>=2V;VIL<=0.8V。另外由于2.4V與5V之間還有很大空閑,對(duì)改善噪聲容限并沒(méi)什么好處,又會(huì)白白增大系統(tǒng)功耗,還會(huì)影響速度。所以后來(lái)就把一部分“砍”掉了。也就是后面的LVTTL。

LVTTL電平

LVTTL又分3.3V、2.5V以及更低電壓的LVTTL(Low Voltage TTL)。

3.3V LVTTL:

Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。

2.5V LVTTL:

Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。

TTL使用注意:TTL電平一般過(guò)沖都會(huì)比較嚴(yán)重,可能在始端串22歐或33歐電阻;TTL電平輸入腳懸空時(shí)是內(nèi)部認(rèn)為是高電平。要下拉的話(huà)應(yīng)用1k以下電阻下拉。TTL輸出不能驅(qū)動(dòng)CMOS輸入。

COMS電平

COMS:Complementary Metal Oxide SemiconductorPMOS+NMOS。CMOS的速度比較快,大多數(shù)用于相對(duì)高速的器件,比如一驅(qū)多時(shí)鐘芯片。

Vcc:5V時(shí),輸出:VOH>=4.45V;輸入:VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。

CMOS使用注意:CMOS結(jié)構(gòu)內(nèi)部寄生有可控硅結(jié)構(gòu),當(dāng)輸入或輸入管腳高于VCC一定值(比如一些芯片是0.7V)時(shí),電流足夠大的話(huà),可能引起閂鎖效應(yīng),導(dǎo)致芯片的燒毀。相對(duì)TTL有了更大的噪聲容限,輸入阻抗遠(yuǎn)大于TTL輸入阻抗。對(duì)應(yīng)3.3V LVTTL,出現(xiàn)了LVCMOS,可以與3.3V的LVTTL直接相互驅(qū)動(dòng)。

3.3V LVCMOS:

Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。

2.5V LVCMOS:

Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

ECL、 PECL、LVPECL電平

ECL:Emitter Coupled Logic 發(fā)射極耦合邏輯電路(差分結(jié)構(gòu))

Vcc=0V;Vee:-5.2V;VOH=-0.88V;VOL=-1.72V;VIH=-1.24V;VIL=-1.36V。

速度快,驅(qū)動(dòng)能力強(qiáng),噪聲小,很容易達(dá)到幾百M(fèi)的應(yīng)用。但是功耗大,需要負(fù)電源。為簡(jiǎn)化電源,出現(xiàn)了PECL(ECL結(jié)構(gòu),改用正電壓供電)和LVPECL。

PECL:Pseudo/Positive ECL

Vcc=5V;VOH=4.12V;VOL=3.28V;VIH=3.78V;VIL=3.64V

LVPELC:Low Voltage PECL

Vcc=3.3V;VOH=2.42V;VOL=1.58V;VIH=2.06V;VIL=1.94V

ECL、 PECL、LVPECL使用注意:不同電平不能直接驅(qū)動(dòng)。中間可用交流耦合、電阻網(wǎng)絡(luò)或?qū)S眯酒M(jìn)行轉(zhuǎn)換。以上三種均為射隨輸出結(jié)構(gòu),必須有電阻拉到一個(gè)直流偏置電壓。(如多用于時(shí)鐘的LVPECL:直流匹配時(shí)用130歐上拉,同時(shí)用82歐下拉;交流匹配時(shí)用82歐上拉,同時(shí)用130歐下拉。但兩種方式工作后直流電平都在1.95V左右。)

LVDS電平

LVDS:Low Voltage Differential Signaling。前面的電平標(biāo)準(zhǔn)擺幅都比較大,為降低電磁輻射,同時(shí)提高開(kāi)關(guān)速度又推出LVDS電平標(biāo)準(zhǔn)。差分對(duì)輸入輸出,內(nèi)部有一個(gè)恒流源3.5-4mA,在差分線(xiàn)上改變方向來(lái)表示0和1。通過(guò)外部的100歐匹配電阻(并在差分線(xiàn)上靠近接收端)轉(zhuǎn)換為±350mV的差分電平,中心電平一般在1.2V左右。LVDS使用注意:可以達(dá)到600M以上,PCB要求較高,差分線(xiàn)要求嚴(yán)格等長(zhǎng),差最好不超過(guò)10mil(0.25mm)。100歐電阻離接收端距離不能超過(guò)500mil,最好控制在300mil內(nèi)。

CML電平

CML:是內(nèi)部做好匹配的一種電路,不需再進(jìn)行匹配。三極管結(jié)構(gòu),也是差分線(xiàn),速度能達(dá)到3G以上。只能點(diǎn)對(duì)點(diǎn)傳輸。

GTL電平

GTL:類(lèi)似CMOS的一種結(jié)構(gòu),輸入為比較器結(jié)構(gòu),比較器一端接參考電平,另一端接輸入信號(hào)。1.2V電源供電。

Vcc=1.2V;VOH>=1.1V;VOL<=0.4V;VIH>=0.85V;VIL<=0.75V

PGTL/GTL+:

Vcc=1.5V;VOH>=1.4V;VOL<=0.46V;VIH>=1.2V;VIL<=0.8V

HSTL與SSTL電平

HSTL是主要用于QDR存儲(chǔ)器的一種電平標(biāo)準(zhǔn):一般有V?CCIO=1.8V和V??CCIO= 1.5V。和上面的GTL相似,輸入為輸入為比較器結(jié)構(gòu),比較器一端接參考電平(VCCIO/2),另一端接輸入信號(hào)。對(duì)參考電平要求比較高(1%精度)。SSTL主要用于DDR存儲(chǔ)器。和HSTL基本相同。V??CCIO=2.5V,輸入為輸入為比較器結(jié)構(gòu),比較器一端接參考電平1.25V,另一端接輸入信號(hào)。對(duì)參考電平要求比較高(1%精度)。

HSTL和SSTL大多用在300M以下。

RS232和RS48電平

RS232采用±12-15V供電,我們電腦后面的串口即為RS232標(biāo)準(zhǔn)。+12V表示0,-12V表示1。可以用MAX3232等專(zhuān)用芯片轉(zhuǎn)換,也可以用兩個(gè)三極管加一些外圍電路進(jìn)行反相和電壓匹配。

RS485是一種差分結(jié)構(gòu),相對(duì)RS232有更高的抗干擾能力。傳輸距離可以達(dá)到上千米。

原文標(biāo)題:FPGA幾種電平:TTL,CMOS以及LVTTL,LVCMOS

文章出處:【微信公眾號(hào):嵌入式學(xué)習(xí)資料】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1644文章

22007瀏覽量

616290

發(fā)布評(píng)論請(qǐng)先 登錄

什么是TTL電平、CMOS電平?區(qū)別?

TTL電平和CMOS電平的區(qū)別!

TTL電平 CMOS電平推挽輸出

電平標(biāo)準(zhǔn)

TTL電平與CMOS電平的區(qū)別,TTL & CMOS

ttl電平與cmos電平的區(qū)別

FPGA的常用電平標(biāo)準(zhǔn)

詳解信號(hào)邏輯電平標(biāo)準(zhǔn):CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載

I/O接口標(biāo)準(zhǔn)(1):LVTTL、LVCMOS、SSTL、HSTL

FPGA幾種電平:TTL,CMOS以及LVTTL,LVCMOS

FPGA幾種電平:TTL,CMOS以及LVTTL,LVCMOS

評(píng)論