引言

在電子電氣架構從分布式向域集中式演進的過程中,行泊一體域控方案應運而生。據不完全統計,到現在為止,國內至少已經有十幾家廠商發布了行泊一體域控的解決方案。

整體來講,行泊一體技術方案可以劃分為中低算力(輕量級)行泊一體域控方案和大算力行泊一體域控方案。關于兩者的區別,感興趣的讀者可以查閱筆者之前的文章:《關于智能駕駛域控制器的一些觀察》和 《行泊一體 - 打通智能駕駛的“任督二脈”》——分別從市場維度和技術維度展開了詳細說明,此處便不再具體展開。

無論是輕量級行泊一體域控,還是大算力行泊一體域控,都會有單SoC芯片配置和多SoC芯片配置之分。在當前階段,多SoC芯片配置是一種比較常見的行泊一體硬件架構方案。

目前市場上推出的多SoC芯片行泊一體方案案例有:

1)中低算力級別:3*J3, J3+TDA4以及雙TDA4等

2)大算力級別:雙Orin-X,4Orin-X 以及 2*SA8540P+SA9000P等

基于當前芯片技術的發展和不同等級自動駕駛對域控方案的性能需求,不少業內人士一致認為,中短期內,大算力行泊一體域控依然會繼續沿用多SoC芯片方案;輕量級行泊一體域控將逐漸開始采用單SoC芯片方案。

輕量級行泊一體域控方案的功能需求和系統應用 —— 用于實現什么樣的功能、需要什么樣的傳感器配置、采用什么樣的算法模型等,已經比較確定;另外,芯片廠商也在不斷地推出可以支持單SoC芯片行泊一體域控方案的芯片,比如 黑芝麻的A1000L和A1000 、行歌的SD5223等。因此,單SoC芯片行泊一體方案將會率先在輕量級域控領域規模化量產落地。

1.業內關于單SoC芯片行泊一體方案的一些質疑

1.1 目前,為什么大算力行泊一體域控很少采用單SoC芯片方案?

大算力行泊一體域控,比較常見的是采用英偉達的Orin芯片,比如國內的蔚小理、上汽智己、上汽非凡汽車、威馬等品牌。他們有的是采用雙Orin方案,也有采用4片Orin方案, 但是很少有采用單Orin方案,這是為什么呢?

經過調研分析,主要原因有以下幾個方面:

其一,采用Orin方案的車型,目前基本都屬于前期拼配置的階段,對成本尚不太敏感。各車廠希望能夠在功能和算力上進行比拼,雖然采用多SoC芯片方案成本高,但廣告宣傳效果也會更好。

其二,現階段,算法廠商或者車廠自研的大算力域控相關的算法還不夠成熟,仍需要進一步優化。因此,車廠在前期需要做好算力預埋,防止后期對算法模型進行優化時出現算力不夠用的尷尬局面。

其三,與大算力行泊一體域控的市場定位有關 ——大算力域控用于支持更高階的智能駕駛功能,對功能安全等級的要求較高,并且還需要做系統冗余的方案設計。然而,單SoC方案目前尚不能很好地滿足大算力域控的這些要求,因此,在短期內,大算力域控還無法使用單SoC芯片方案來實現。

1.2 對于單SoC芯片輕量級行泊一體方案,芯片廠商如何兼顧SoC芯片性能和成本上的平衡?

對于芯片廠商而言,首先,他們需要把芯片性能定義好,以保證后續功能應用的拓展和升級。其次,他們也需要兼顧到芯片的成本。

尤其是輕量級行泊一體域控方案,主機廠為了能夠盡快地讓其量產上車,一般采用軟硬一體的打包解決方案,所以主機廠會重點關注兩點:一是,它能不能盡快量產;二是,它有沒有較高的性價比。

在之前的分布式ECU架構方案下,行車和泊車功能分別用獨立的控制器來實現:1個前向多功能攝像頭模塊(內部包含行車控制器)+ 1個泊車控制器。現在單個SoC芯片要把兩者融合在一起,如何去平衡芯片的性能和成本,是一件很有挑戰性的事情。

那么,芯片公司又會如何應對這樣的挑戰呢?黑芝麻智能高級產品經理額日特介紹道:“我們在芯片設計之初,就把整個芯片的配置設計得比較完整和均衡,確保芯片在能夠承擔更多功能的同時,對各項應用也能提供足夠的算力支持。同時,我們還考慮芯片設計的連續性問題,比如A1000L和A1000采用pin2pin的平臺化方案設計,算力可以靈活配置,有利于降低客戶域控平臺的拓展升級成本。我們的產品通過不停地迭代,能夠很好地做到成本和性能上的均衡。”

1.3 關于單SoC芯片行泊一體方案,目前去掉外掛MCU合適么?

現在的主控SoC芯片內部一般都內置有MCU模塊,因此,一些Tier1在做單SoC芯片行泊一體方案開發的時候,也在考慮用SoC芯片內部的MCU去替代外掛的MCU。

不過,現在大多數業內人士認為,目前尚不具備完全替代外掛MCU的條件,主要原因如下:

1)與傳統成熟工藝的外掛MCU相比,內置MCU的內存有限,影響規劃控制算法模型及MCU系統軟件部署。

2)內置MCU在功能安全、實時性和可靠性方面與外掛MCU相比仍存在一定的差距。

3)把一些系統軟件和功能軟件從已成熟開發完成的外掛MCU移植到內置MCU上可能會產生軟件漏洞或軟件缺陷上的一些風險。

因此,短期來看,單SoC芯片的行泊一體方案,依然需要配合一個外掛MCU來實現行泊一體功能。

黑芝麻智能系統架構高級經理仲鳴告訴九章智駕:“黑芝麻的 SoC 芯片內置多顆MCU核心,用戶可以靈活使用其處理高實時任務,同時它們也可以用來承擔信息安全和功能安全兩個重要任務 —— 滿足HSM 信息安全要求以及診斷和監控等一些功能安全方面的功能,這些功能可以很好地在有限的存儲空間內實現。

“但是,從整個業內的芯片產品以及軟件算法的發展來看,在現階段,把整套AUTOSAR及規控相關的應用程序全部從外掛MCU移植到SoC內部的MCU仍存在一定的挑戰。

1)內置MCU存儲空間有限, 采用高階制程的處理器現在還無法支持內部的 Flash 存儲集成,必須外掛一個Flash 存儲器。相比之下,外掛MCU多采用傳統成熟的制程,內存空間也大,數據/軟件代碼都可以存放在芯片內的 Flash存儲器 ,因此外掛MCU可以運行稍大一些的算法模型,并且運算速度較快。

2)內置MCU在低功耗方面處于劣勢,考慮到大型處理器結構復雜,在休眠的時候,作為子系統的內置MCU模塊很難做到像外掛MCU一樣極低的休眠功耗和豐富的喚醒功能。”

1.4 如何做好單SoC芯片行泊一體方案在功能安全和信息安全上的有效隔離?

在芯片設計之初,硬隔離設計是過安全認證的一個非常重要的環節。芯片內部不同模塊之間數據的相互訪問控制,可以避免數據的誤操作和數據的泄露,對信息安全和功能安全都有至關重要的作用。同時,它還可以起到對外設的保護作用。外設的保護主要是功能安全方面的防護 —— 當傳輸一些重要的功能安全數據的時候,不會被其它的核心模塊所干擾,進而避免功能安全相關的數據(比如剎車、油門等執行控制信號)出錯。

如果是多個SoC芯片級聯的方案,系統會更復雜,所要考慮的因素會更多,不僅要考慮單個芯片內部的隔離,還要考慮芯片與芯片之間的隔離,因此整個系統的隔離設計會更加復雜。

對于單SoC芯片行泊一體方案,主流的SoC芯片上面都會內置有功能安全島 - Safety MCU ,相當于是一個“監督者”的角色 —— 不斷地去監控SoC內部其它重要模塊的工作情況。因為錯誤的來源是單向的,所以,當某個硬件模塊出現問題,該模塊可以直接通過內部的硬件機制匯報給功能安全島。單SoC芯片方案使得系統的集成度更高,不僅降低了系統隔離設計的難度,也提升了系統的可靠性。

“現在大家的SoC芯片基本都是異構多核,可能有CPU+NPU+MCU+DSP+ISP等多種核。但是,這些核的能力有多強,能做哪些事情,因芯片廠家而異。

“比如,有的SoC芯片內部只有1個或2個DSP,DSP可能全部被分配去做傳統的CV圖像處理,而黑芝麻的芯片內部有4個大型DSP,這些DSP除了做大量圖像及激光算法處理之外,還承擔實時管理神經網絡加速器的工作。這樣便無需占用CPU ARM核參與網絡執行,大幅度釋放CPU資源;并且,SoC芯片內置有MCU核 —— 實現內部其它計算核之間的通信監控以及報錯的功能。

“總之,SoC芯片內部的核越多越全面,結合硬件隔離技術的應用,能夠做到支持不同功能、不同類別的應用空間也越大,確保各核之間互不影響、高可靠運行。”額日特講道。

2. 什么樣的單SoC芯片才可以支持行泊一體功能?

在輕量級域智駕域控方案中,需要多大的算力才能滿足應用需求呢?

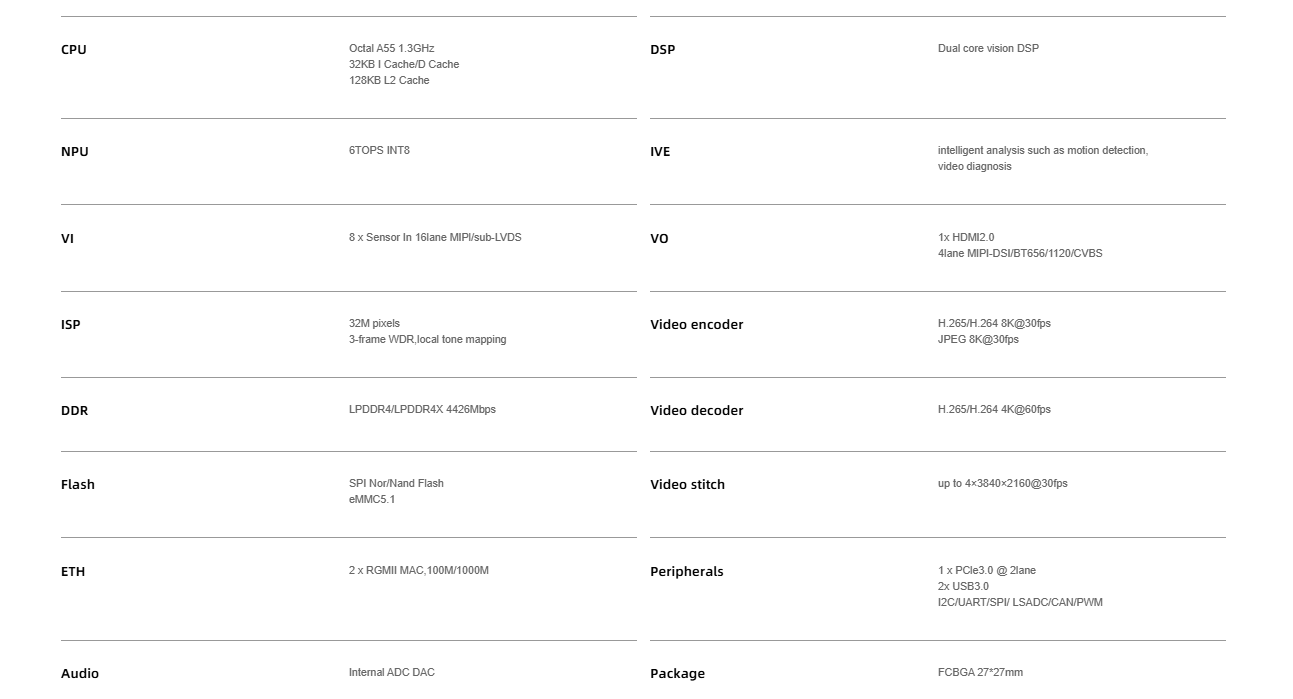

仲鳴表示,在輕量級行泊一體域控方案中, 一般情況下,1顆800萬像素前向攝像頭大概會用到8TOPS左右的AI算力。4顆200萬像素環視攝像頭通常需要用到 4TOPS的AI算力。對于上述的AI算力需求來講,A1000L(16TOPS)的AI算力是非常精準的設計。

另外,行車和泊車場景需要不同類型的核去完成相應的任務。例如,泊車場景下,3D環視全景的渲染和圖像拼接都必須使用GPU來完成;行車場景下,攝像頭和毫米波雷達的數據融合以及地圖定位需有足夠算力的CPU以及DSP去完成。

基于GPU的3D渲染效果示意圖(圖片來源于網絡)

在接口層面,芯片廠商不僅需要預留足夠的傳感器接口,同時還要考慮到這些傳感器接入后,數據的處理對各類存儲器和帶寬的需求。最后,還要預留PCIE、USB等用于擴充算力和存儲的一些接口,確保整個域控方案具有一定的可擴展性。

總之,能同時支持行車和泊車的單SoC芯片應滿足如下幾項條件 ——

2.1 有充足的CPU算力和AI算力支持

據安霸軟件研發高級總監孫魯毅透露,如果用單SoC芯片去做入門級行泊一體方案,CPU的算力大概只需要20KDMIPS左右,如果有硬件加速,CPU算力需求可相應降低;而AI等效算力只需要十幾個TOPS。

若支持高階版單SoC行泊一體方案,CPU算力至少需要150KDMIPS,AI算力至少100TOPS。因為,高階版的行泊一體方案需要接入更多路、更高分辨率的攝像頭,甚至還需增加4D毫米波雷達、激光雷達等傳感設備,并且運行的神經網絡模型也要更大更復雜,因此CPU算力和AI算力需求都會呈7~10倍的增長。

另外,行泊一體方案對算力的需求,與采用前融合處理還是后融合處理也存在較大關系。

后融合是指各傳感器獨立輸出各自的感知結果,并在決策層進行融合;而前融合是指把各傳感器采集的數據經過時間和空間同步后,直接對原始數據進行融合。

前融合相比于后融合,能夠讓數據更早地做融合,數據損失比較少,融合結果的質量也會有較大程度的提升。但是,前融合是對輸入進來的不同模態的原始數據經過空間對齊后直接進行融合,不僅數據對齊過程中處理量大,并且還需要通過大規模神經網絡運算識別出障礙物大小、位置等信息,因此前融合對SoC芯片的CPU算力和AI算力都提出了極大的要求。

2.2 采用異構多核的架構設計

通常來看,能支持行泊一體功能的單SoC芯片主要包括以下幾種處理單元:

1)通用邏輯運算單元:通常是基于CPU來實現,主要負責一些邏輯運算任務,用于管理軟硬件資源,完成任務調度,實現系統層面的功能邏輯、診斷邏輯以及影子模式數據挖掘功能等。一些典型的應用包括:基于優化的決策規劃算法、車輛控制算法等。

2)AI加速單元:通常是基于GPU或NPU等處理器來實現,承擔大規模浮點數并行計算需求,會涉及到大量的典型神經網絡的運算,主要用于攝像頭、激光雷達等傳感器數據的融合、特征提取、分類等。一些典型的應用包括:物體檢測、車道線檢測、紅綠燈識別等。英偉達是采用GPU來實現,而其它主流的芯片廠商采用ASIC去實現,比如黑芝麻的DynamAI NN引擎, 安霸的NVP等。

3)圖像/視頻處理單元:通常是基于DSP、ISP、GPU等處理器來實現。

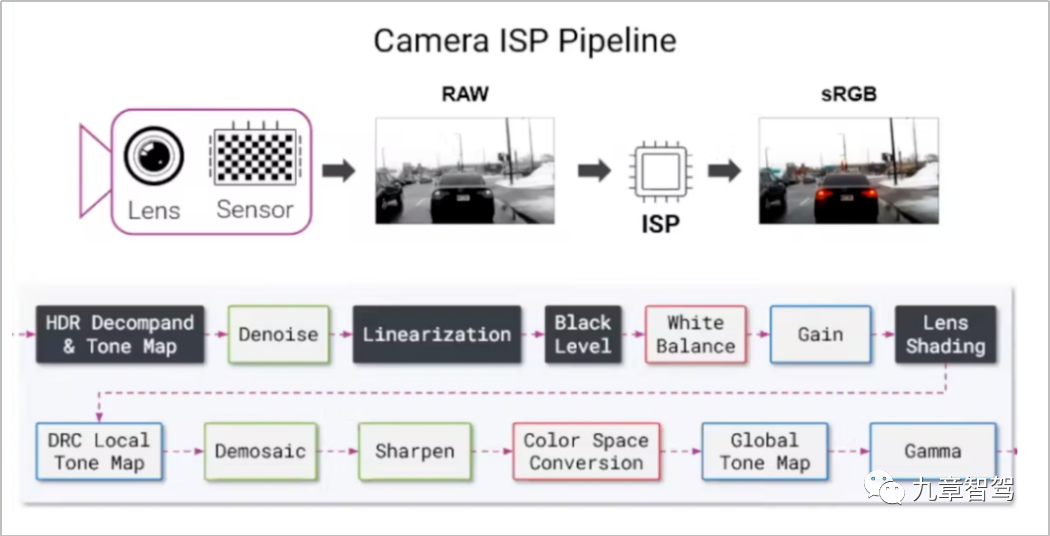

ISP作為視覺處理芯片,其主要功能是對攝像頭輸出的圖像信號做調校,包括 AE(自動曝光)、AF(自動對焦)、AWB(自動白平衡)、圖像去噪等;

攝像頭ISP工作流程(圖片來源于網絡)

DSP是一種具有特殊結構的微處理器,相比于通用CPU,它更適用于計算密集度高的處理工作。一些典型的應用包括:傳統的CV圖像處理、一些自定義算子的加速處理等;

GPU具有較強的浮點運算能力,主要用于泊車場景中的圖像拼接和渲染等工作。

4)內置MCU:用于實現功能安全和信息安全相關的一些基本任務,例如SoC內部各計算模塊的狀態監控和通信監控,以及在各模塊出現問題后能夠及時報錯等。

2.3 支持足夠多的傳感器接入

用于支持行泊一體方案的單SoC芯片需要預留足夠多的傳感器接口 ——支持多路攝像頭接入、多路以太網設備接入(4D毫米波雷達的主要接口是百兆以太網,激光雷達的主要接口是千兆以太網)、多路 CAN 接口設備接入(3D毫米波雷達)等。另外,能夠支持多少類型或多少路的傳感器接入,除了需要具備相應的接口和足夠的算力支持外,對SoC內部的其它相關模塊也有一定的要求。

例如,攝像頭主要考驗的是內存帶寬和ISP的處理能力,4D毫米波雷達主要考驗的是CPU的算力,激光雷達對CPU算力、AI算力以及內存帶寬的要求都很高。

攝像頭:攝像頭應用的數量越來越多,分辨率也越來越高,對ISP的處理能力要求也越來越高。同時,多路高清攝像頭數據的輸入也需要較高的內存帶寬來保證圖像數據的傳輸和處理效率。

孫魯毅講到,之前攝像頭內部一般集成有獨立的ISP模塊,現在ISP被集成到域控制器的主控SoC芯片上。如果ISP能夠通過內置的SRAM對來自多路攝像頭的圖像輸入進行計算,計算完之后再輸出到內存,便可以有效降低多路攝像頭輸入對內存帶寬的占用。

4D毫米波雷達:標準的4D毫米波雷達輸出結果是點云,各種點云的處理算法,比如聚類、特征降噪、感知、融合等,需要在SoC芯片內部進行執行,這些算法對于CPU的要求比較高。

激光雷達:激光雷達一般需要通過百兆網甚至千兆網接入。一般情況,它直接給SoC芯片輸入原始數據,并在SoC芯片上進行原始數據的處理,需要跑一些復雜的神經網絡算法,所以,它對SoC芯片內部的CPU算力、AI算力以及內存帶寬都有比較高的要求。

3.“真正融合”的行泊一體方案

由于市面上很少有一款合適的SoC芯片能夠以單芯片來支持行泊一體方案,因此主機廠也只能被動接受雙芯片甚至三芯片方案。然而,業內人士普遍認為,單SoC芯片方案才是“真正融合“的行泊一體方案。額日特說:“黑芝麻智能的A1000L和A1000芯片,無論性能,還是成本,都可以適配行泊一體方案的需求,可以作為目前市面上雙芯片或三芯片行泊一體的替代方案 ——其單芯片算力及架構足以分別支持入門級(5V5R )和高階(10V5R)行泊一體感知解決方案。”

那么,相比于多SoC芯片方案,基于黑芝麻智能A1000L或A1000的單SoC芯片行泊一體方案具有哪些優勢呢?

A1000L系統框圖

3.1 高能效

黑芝麻自研了兩個車規級核心IP:深度神經網絡處理器NPU - DynamAI NN引擎和圖像信號處理器ISP - NeuralIQ ISP。為什么說這兩個自研的IP可以給整個單SoC芯片(A1000L/A1000)行泊一體域控方案帶來較高的能效呢?

額日特向九章智駕解釋道:“自動駕駛的算法模型有大有小,如果只有一種類型的加速器,讓小模型跑到大的加速器上或者大模型跑到小加速器上,運算效率都會低很多。

“考慮到這個因素,我們的NPU采用多維異構的架構,包括三維的矩陣(MAC - 做乘加器)、兩維的矩陣以及一維的非線性的激活函數加速器等。另外,在NPU內部還有一個內置的DSP去做調度。

“所以,整體上NPU的算力利用率很高,最高可以達到80%。

“同時,我們的ISP采用高效的inline模式,攝像頭數據從采集到ISP處理,全部在線完成無需進出DDR。因此,數據處理完成后能夠及時地傳送到NPU去處理,并通過適配不同的加速器來保證整體的流暢性和識別效率。因為自研核心IP的兩個模塊具有很高的配合度,所以一整套系統運作下來,鏈路更通暢,整體的效能也更優。”

3.2 芯片內部資源高度共享

1)存儲資源完全共享

相比于多芯片方案,單SoC芯片方案的存儲區域共享,所有的計算模塊,不管是 CPU、NPU、GPU還是DSP ,他們之間不再需要去做片間的數據拷貝,這會大大提高傳感器數據的處理效率。

2)計算資源完全共享

在單SoC行泊一體技術方案中,SoC芯片內部的CPU、NPU以及DSP等計算資源可以完全共享,通過系統調度,內部計算資源得到充分的利用,同時,相應的工作任務也能夠高效完成。

仲鳴舉例說:“一般而言,行泊一體技術方案至少需要>20KDMIPS的CPU算力,如果是多SoC芯片方案,算力資源可能要被拆成多份跨SoC運行,相同任務的執行時間可能就要加倍。因為當芯片的計算資源被拆成多份后,很難有集中計算的能力,并且中間還會有一些數據同步或者匯總的操作,會影響整個系統的性能。

“如果是單SoC方案,8個CPU核心放在一個SoC內,可以同時工作去執行一項任務,任務很快就被完成。”

3.3 傳感器數據深度復用

在單SoC芯片方案中,所有的傳感器數據都會被傳輸到同一個SoC芯片內,并在存儲器內共享。那么,數據的傳輸速率更快、時延更低,系統的響應時間也會更短,有利于不同類型攝像頭(行車攝像頭和泊車攝像頭)的數據在對系統響應要求非常高的場景下進行復用。比如,泊車場景需要復用行車攝像頭的數據實現前方或側向物體的避障;行車場景需要復用泊車攝像頭的數據來實現車輛的橫向控制。

另外,在一個SoC芯片上,系統通過軟件能夠統一去訪問和調度芯片內部的資源,及時從各傳感器接口獲取到傳感器的原始數據進行融合,并快速地得出結果。因此,單SoC芯片方案更有利于做傳感器數據的前融合。

額日特解釋道:“前融合會涉及到時間同步的問題 :原始數據的時間戳是什么樣的 - 攝像頭的時間戳、毫米波雷達的時間戳、激光雷達的時間戳。

“例如,一輛車配置有攝像頭、毫米波雷達和激光雷達等多個傳感器,這些傳感器數據在做前融合時,會涉及到一個時間當量 —— 需要考慮這些傳感器的數據分別在什么時間點傳輸進來,如果數據傳輸進來的時間點不一致,就不能做融合處理。

“如果是多SoC芯片方案,這些傳感器數據可能分別輸入給不同的SoC芯片,需要考慮片間通訊的時延等問題,時間同步設計比較復雜;而在單SoC芯片方案中,所有傳感器數據都直接發送到同一個芯片上,時間同步設計相對就要簡單很多。”

3.4 有助于降低隱性成本

1)降低整個系統的物料成本

兩個差不多算力量級的行泊一體域控方案,一種采用單SoC芯片,一種采用多顆SoC芯片拼湊到一塊的形式,從系統整體成本上來看,單SoC芯片行泊一體方案系統成本會更低。

仲鳴認為,多SoC芯片方案中不應只考慮單一SoC芯片的價格,若算總賬,系統整體的成本還是非常高。因為每顆 SoC芯片都需要去適配自己的DDR存儲器和電源模塊等配套的基礎設施。從典型的嵌入式系統來看,SoC本身的成本可能只占總成本的一半不到,另外一半的成本來自這些配套的基礎設施,像eMMC 、NOR Flash 這些存儲器,單SoC芯片只需要一份,多SoC芯片可能就需要配備多份存儲設備資源。同樣,每顆SoC芯片基本上都需要一個獨立的 PMIC(電源管理模塊)。這些配套的部件都是整個系統里不可忽略的成本。

2)降低平臺拓展升級成本

A1000L和A1000是平臺化的產品 - 兩款芯片 pin2pin設計,軟硬件架構上完全兼容,有利于Tier1幫助車企打造平臺化方案,降低整個平臺的開發成本。

“車廠內部一般都開發有不同定位的車型平臺,比如低端平臺會選一個小算力芯片,中高端平臺選一個中等算力或大算力芯片;如果中高端平臺的車型銷量不高,并且平臺本身的溢價也不高,那么,車廠為中高端平臺重新去開發一個平臺的成本就很難被均攤下來。

“如果采用黑芝麻的芯片,可以低端平臺用A1000L,中高端平臺用A1000。因為兩者采用相同的軟硬件架構設計,在做平臺拓展升級時,可能只需要稍微改動一下外設接口,但整個板子的基本架構不用動,再加上系統軟件大規模的重用,這會帶來隱形成本的大幅度降低。”額日特介紹說。

3)減輕芯片廠商的備貨壓力

在當前缺芯的大環境下,芯片使用數量的減少,可以減輕芯片廠商在庫存和供應鏈管理方面的壓力。

額日特表示,單SoC芯片方案不但對主控SoC芯片本身的供應鏈管理非常友好,并對其配套的電源芯片和存儲芯片的管理也非常友好。A1000L和A1000采用pin2pin 的平臺化設計,有很多通用的物料。在極端情況下,假如A1000L整個板子上面有一些用料,現在買不到,就可以暫時把A1000的料轉用到A1000L上,以解燃眉之急。

4.芯片廠商如何助力主機廠更快地實現行泊一體方案的量產落地

4.1 充分了解主機廠的需求

軟件定義汽車已經成為業內的共識,外加“缺芯”的持續影響,芯片公司在整個汽車產業鏈中的地位發生了顯著變化 - 他們現在開始走向“前臺”去直面主機廠,既可以幫助Tier1拿項目,也可以和主機廠直接展開密切合作。

輕量級行泊一體域控,主機廠一般不會考慮自研,大多會選擇外包給Tier1,因此,芯片廠商需要通過與Tier1以及算法公司密切合作來間接地幫助主機廠實現行泊一體方案的快速落地。

大算力行泊一體域控,主機廠比較重視,一般會選擇自研,因為它是體現主機廠差異化和品牌力的重要部分。芯片公司作為參與方需要直接與主機廠展開密切合作 —— 在提供芯片的同時,還需要為主機廠提供相關配套工具鏈,進而推動項目更快實現量產落地。

因此,芯片廠商首先要了解主機廠到底想要什么樣的行泊一體方案,其次是要了解主機廠希望采用什么樣的合作模式。只有如此,芯片廠商才能更好地對癥下藥。

孫魯毅說:“我們逐漸體會到,需要跟主機廠進行更好、更深的溝通。只有這樣,芯片廠商才能更好地理解主機廠需要什么樣的行泊一體方案 ——是一個入門級,還是一個中等級別,亦或者是一個高性能級別;打算配置什么樣的傳感器(多少個攝像頭、多少個激光雷達);有什么樣的成本控制目標;SOP的時間如何安排等等。只有充分了解主機廠的需求,才能更快、更順利地展開合作。”

4.2 自研AI工具鏈和軟件算法

1)自研AI工具鏈

開發者要移植軟件/算法到芯片上,最關鍵的部分就是工具鏈 — 神經網絡的工具鏈是否好用、軟件交叉編譯的工具鏈是否好用?如果工具鏈好用,開發者就比較容易上手,就能夠縮短開發時間。

黑芝麻智能提供一整套深度學習工具鏈,可以將用戶在服務器以及其它平臺上開發的算法模型,轉換成在黑芝麻芯片上可以運行的程序。額日特介紹說“由于每一家用的模型可能都不太一樣,我們已經可以提供市面上所有主流模型的轉換工具,包括精度的調整、模型的裁剪等等。另外,我們還有一些仿真軟件,使得客戶在電腦上仿真就可以達到跟在板子上跑一樣的效果,這會大大減少客戶的一些重復性工作。”

2)自研軟件和算法

芯片廠商可以配合自家芯片自研中間件和感知算法,縮短客戶開發上層應用的時間,幫助合作伙伴更快、更高效地完成項目的量產落地。

黑芝麻智能自研了瀚海中間件,它是基于華山系列計算芯片推出的一款智能駕駛平臺SDK開發包,可屏蔽基礎硬件、操作系統和通訊協議的異構性,從而更好地鏈接上層應用和操作系統。

同時,黑芝麻智能自主研發了多種感知算法,并通過不同維度的數據,以無監督或者半監督的方式來提升算法的魯棒性。

“卷積神經網絡算法(CNN)也是最近幾年剛興起,很多車廠和Tier1并不具備感知算法的開發能力,并且,算法人才和能力的培養也不是短時間內能做到的事情。因此,我們需要配合客戶去完成感知算法的開發 —— 客戶會提出一些具體的需求,由我們去做具體的實施,包括前向避障、車道線識別等。另外,我們的算法與芯片不存在綁定關系,主機廠可以同時選擇我們的芯片和算法,也可以直接移植他們的自己的算法到我們的開發板。”額日特說。

結語

2025年是個關鍵的時間節點,是車企培養供應鏈體系的重要時機。黑芝麻智能CMO楊欣宇曾對外表示,“2025年之前如果芯片能上車,進入車廠的供應鏈體系,未來的機會很多。如果2025年還上不了車,這個芯片廠商的機會就非常小了。”對車企來講,培養一個成熟的供應商,特別是大算力芯片供應商,需要投入大量的人力、物力,如果沒有特殊原因,車企根本沒有更換的動力。

行泊一體方案的加速落地,也從側面反映了SoC芯片的市場需求在不斷地變大,并且市場逐漸變得成熟,價格也會更加透明,合作方之間的合作也越來越密切,最終將形成一個相對穩定的產業生態。

只要芯片廠商的產品具有足夠的競爭力 —— 產品的可靠性和魯棒性好、主要技術指標上有競爭力、相關的工具鏈要好用、供貨要有保證等,就一定能夠站穩腳跟,并脫穎而出。

審核編輯 :李倩

-

mcu

+關注

關注

146文章

17898瀏覽量

362140 -

控制器

+關注

關注

114文章

17029瀏覽量

183379 -

SoC芯片

+關注

關注

1文章

640瀏覽量

35720

原文標題:單SoC芯片方案,或將加速行泊一體方案規模化量產應用

文章出處:【微信號:阿寶1990,微信公眾號:阿寶1990】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

首款搭載知行科技iDC 500行泊一體域控制器的車型上市

方案解讀 | X9SP 單芯片艙泊一體

目前市場上主流的LLC+PFC組合IC(二合一控制器)匯總

知行科技行泊一體域控制器iDC 300量產落地

CV2880全數字轉全模擬的SOC單芯片介紹

如何選擇合適的邊緣ai分析一體機解決方案

目前市場上推出的多SoC芯片行泊一體方案案例

目前市場上推出的多SoC芯片行泊一體方案案例

評論