NOR gate

OR操作,即是

C=A+B

NOR操作,即是

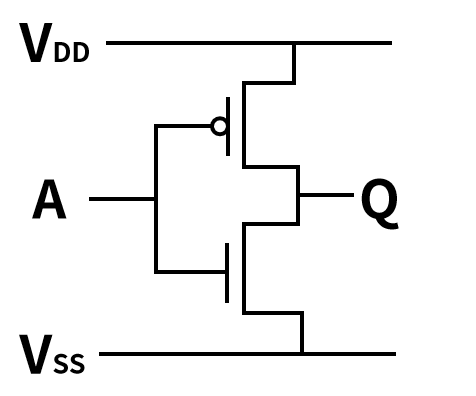

那怎么對CMOS反相器的結構,進行修改,使其變為NOR門呢?

首先,

需要兩個NMOS器件或者PMOS器件,而且由兩個輸入控制

再者,

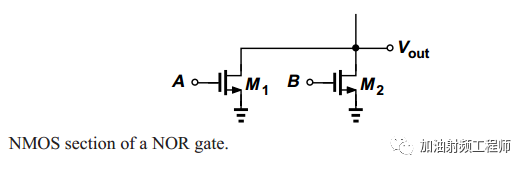

首先考慮NMOS部分,如果其中一個NMOS門是高電平,輸出必須保持低電平。如下圖所示。

其次,

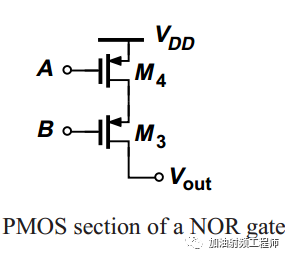

PMOS部分,如果A為高,B為高,或者A、B均為高時,PMOS部分必須處于關斷的狀態。而且,如果A和B均為低時,PMOS部分必須為ON的狀態。

如下圖所示,即滿足以上的要求。

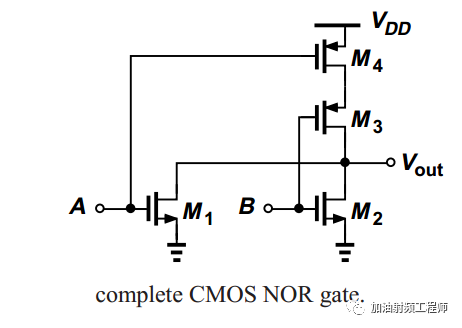

把PMOS部分和NMOS部分,結合起來,就成為一個完整的CMOS NOR gate.

從CMOS反相器來構建電路時,天生就帶著反相屬性,所以,當想要獲得OR 門時,則是在NOR門的后面再加一個反相器。

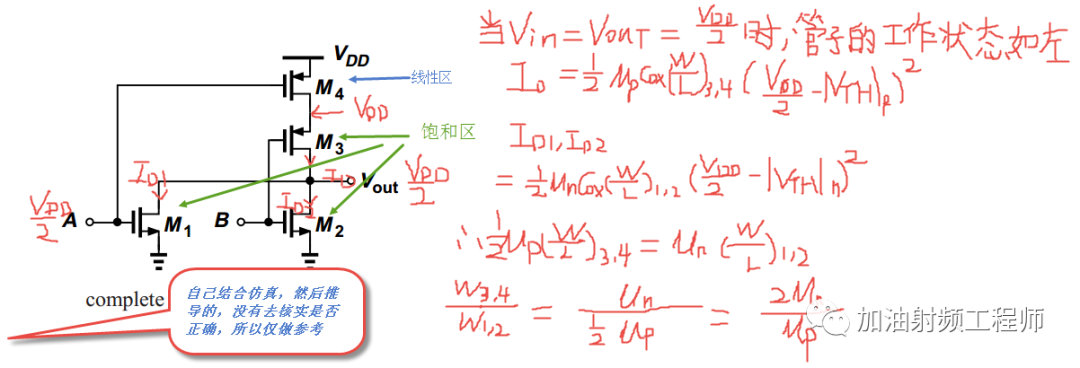

那M1,M2,M3,M4之間的寬度關系是怎么樣的呢?

NAND Gate

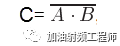

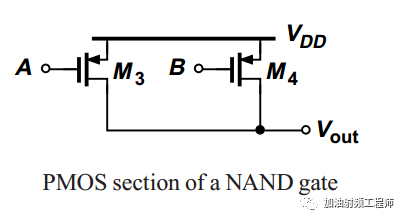

NAND操作即是,

只有輸入A和B都為高的時候,C才是低。

所以,在NMOS部分,應該是,只有A和B都為高的時候,才打通,使得Vout連接到地上。

如下圖所示。

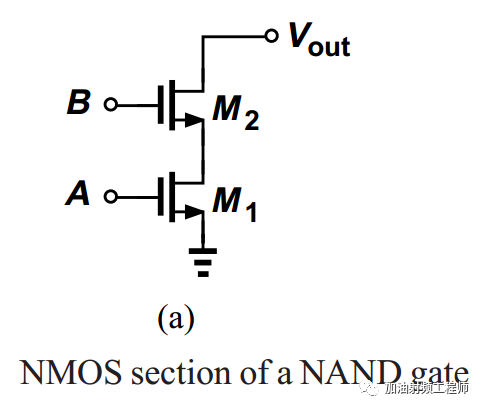

而PMOS部分,當A為低,B為低,或者A、B均為低時,PMOS能夠將Vout與VDD連接。

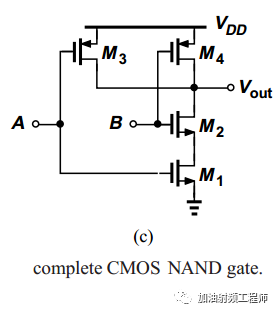

將NMOS和PMOS部分合并,即稱為一個完整的CMOS NAND gate,如下圖所示。

至于M3,M4,M1,M2之間的寬度關系,推導與NOR gate類似,這邊應該都為W。

審核編輯 :李倩

-

CMOS

+關注

關注

58文章

6001瀏覽量

238325 -

NAND

+關注

關注

16文章

1719瀏覽量

137905 -

反相器

+關注

關注

6文章

316瀏覽量

44109

原文標題:CMOS的NOR門和NAND門

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CMOS的邏輯門如何應用在電路中

霍爾開關在消防應急門中的智能應用

TTL邏輯門的種類及應用

FPGA門數的計算方法

晶閘管門極有什么作用

常用邏輯門芯片有哪些

磁通門電流傳感器缺點與優點有哪些

磁通門電流傳感器工作原理是什么

NAND閃存和NOR閃存有什么區別

霍爾開關在門磁開關里的應用

NAND Flash和NOR Flash哪個更好

DevOps中的質量門工作原理,以及靜態代碼分析Klocwork和Perforce Helix QAC在質量門中的實踐應用

磁通門電流傳感器工作原理 磁通門電流傳感器應用

磁通門電流傳感器 開環磁通門與閉環磁通門的區別

CMOS的NOR門和NAND門

CMOS的NOR門和NAND門

評論