臺積電是全球排名第一的半導體代工企業,他們的開放式創新平臺 (OIP) 活動很受歡迎,參加人數也很多,因為所提供的工藝技術和 IP 對許多半導體設計領域都非常有吸引力。臺積電技術路線圖顯示了到 2025 年的 FinFET 和 Nanosheet 計劃的時間表。

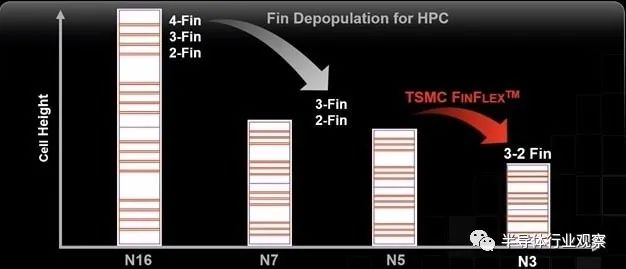

從 N3 開始,出現了一種名為FinFlex的新產品,它使用設計技術協同優化 (DTCO),有望為節能和高性能等細分市場改進功率、性能和面積 (PPA)。借助 FinFlex 方法,設計人員可以根據其設計目標從三種晶體管配置中進行選擇:

3-2 fin blocks,用于高性能

2-2 fin,高效性能

2-1 fin,功率最低,密度最佳

工藝節點 N16 到 N3 中使用的fin選擇的歷史如下所示:

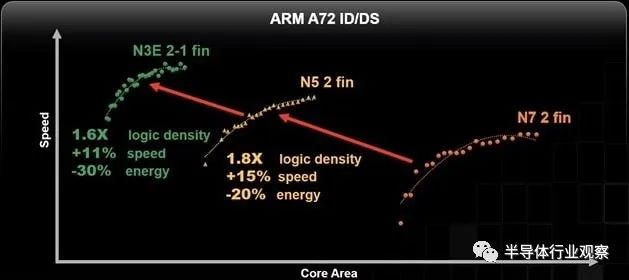

EDA 供應商 Synopsys、Cadence、Siemens EDA 和 ANSYS 已經更新了他們的工具以支持 FinFlex,并且在單個 SoC 中,您甚至可以混合使用fin block選項。沿著時序關鍵路徑,您可以使用高fin單元,而非關鍵路徑單元可以是低fin。作為進程縮放優勢的示例,Lu 展示了一個 ARM Cortex-A72 CPU,在 N7 中實現,具有 2 個fin,N5 具有 2 個fin,最后是 N3E 具有 2-1 個fin:

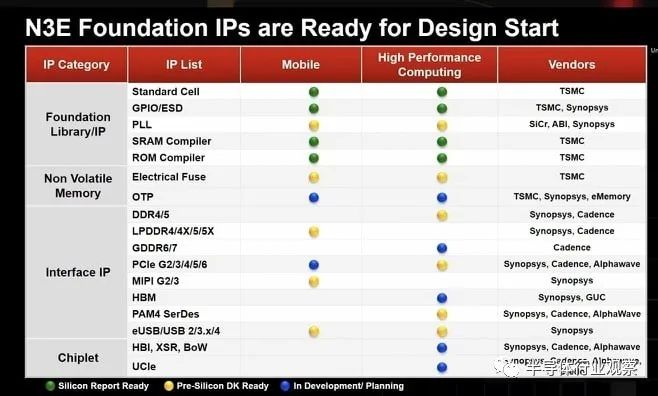

N3E 的 IP 單元來自多家供應商:TSMC、Synopsys、Silicon Creations、Analog Bits、eMemory、Cadence、Alphawave、GUC、Credo。IP 準備狀態分為三種狀態:硅報告準備就緒、硅前設計套件準備就緒和開發中。

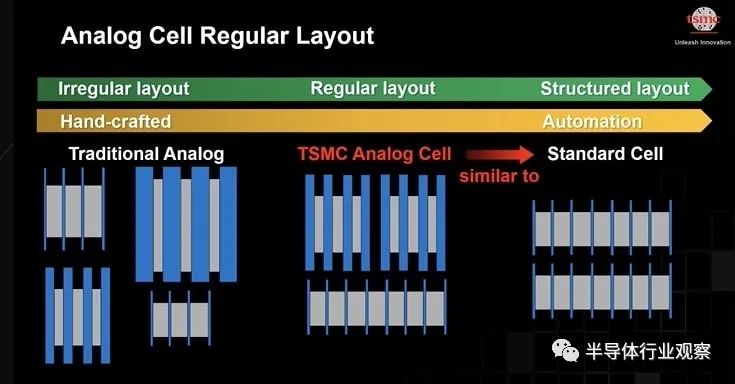

在 TSMC,他們的模擬 IP 使用結構化程度更高的規則布局,這會產生更高的產量,并讓 EDA 工具自動化模擬流程以提高生產力。TSMC 模擬單元具有均勻的多晶硅和氧化物密度,有助于提高良率。他們的模擬遷移流程、自動晶體管大小調整和匹配驅動的布局布線支持使用 Cadence 和 Synopsys 工具實現設計流程自動化。

模擬單元可以通過以下步驟進行移植:原理圖移植、電路優化、自動布局和自動布線。例如,使用他們的模擬遷移流程將 VCO 單元從 N4 遷移到 N3E 需要 20 天,而手動方法需要 50 天,快了大約 2.5 倍。

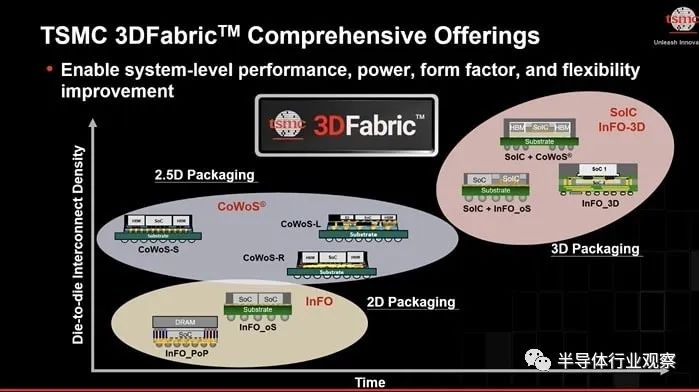

臺積電需要考慮三種類型的封裝,分別是二維封裝(InFO_oS、InFO_PoP)2.5D封裝(CoWoS)和3D封裝(SoIC和InFO-3D)

3DFabric 中有八種包裝選擇:

最近使用 SoIC 封裝的一個例子是 AMD EPYC 處理器,這是一種數據中心 CPU,它的互連密度比 2D 封裝提高了 200 倍,比傳統 3D 堆疊提高了 15 倍,CPU 性能提高了 50-80%。

3D IC 設計復雜性通過 3Dblox 解決,這是一種使用通用語言實現 EDA 工具互操作性的方法,涵蓋物理架構和邏輯連接。四大 EDA 供應商(Synopsys、Cadence、Siemens、Ansys)通過完成一系列五個測試用例,為 3Dblox 方法準備了工具:CoWoS-S、InFO-3D、SoIC、CoWoS-L 1、CoWoS-L 2。

臺積電通過與以下領域的供應商合作創建了 3DFabric 聯盟:IP、EDA、設計中心聯盟 (DCA)、云、價值鏈聯盟 (VCA)、內存、OSAT、基板、測試。對于內存集成,臺積電與美光、三星內存和 SK 海力士合作,以實現 CoWoS 和 HBM 集成。EDA測試廠商包括:Cadence、西門子EDA和Synopsys。IC測試供應商包括:Advantest和Teradyne。

AMD、AWS 和 NVIDIA 等半導體設計公司正在使用 3DFabric 聯盟,隨著 2D、2.5D 和 3D 封裝的使用吸引了更多的產品創意,這個數字只會隨著時間的推移而增加。臺積電擁有世界一流的DTCO工程團隊,國際競爭足以讓他們不斷創新新業務。數字、模擬和汽車細分市場將受益于臺積電在 FinFlex 上宣布的技術路線圖選擇。3D 芯片設計得到 3DFabric 聯盟中聚集的團隊合作的支持。

審核編輯:郭婷

-

半導體

+關注

關注

335文章

28930瀏覽量

238348 -

臺積電

+關注

關注

44文章

5757瀏覽量

169872

原文標題:臺積電先進制程和封裝的更多細節

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

臺積電先進制程和封裝改進功率、性能和面積

臺積電先進制程和封裝改進功率、性能和面積

評論