數(shù)字門級(jí)電路可分為兩大類:組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

組合邏輯描述了門級(jí)電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個(gè)輸入的邏輯與。如果輸入值發(fā)生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級(jí)行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當(dāng)前輸入值的組合。

SystemVerilog有三種在可綜合RTL級(jí)別表示組合邏輯的方法:連續(xù)賦值語句、always程序塊和函數(shù)。接下來幾篇文章將探討每種編碼風(fēng)格,并推薦最佳實(shí)踐編碼風(fēng)格。

連續(xù)賦值語句(布爾表達(dá)式)

連續(xù)賦值語句將表達(dá)式或操作結(jié)果驅(qū)動(dòng)到網(wǎng)絡(luò)或變量上,顯式連續(xù)賦值語句是以assign關(guān)鍵字開始的語句。連續(xù)賦值語句的一個(gè)簡(jiǎn)單示例:

賦值的左邊,即上面的sum;在上面的例子中,每當(dāng)右邊的值發(fā)生任何變化時(shí),即在上面的例子中a或b發(fā)生變化時(shí),sum就會(huì)更新。每當(dāng)右邊發(fā)生變化時(shí),左邊的這種持續(xù)更新行為就是組合邏輯行為的模型。

連續(xù)賦值語句允許在右側(cè)發(fā)生更改和左側(cè)更新之間指定傳播延遲。然而,綜合編譯器預(yù)期RTL模型為零延遲,并且會(huì)忽略連續(xù)賦值語句中的延遲。這可能會(huì)導(dǎo)致經(jīng)過延遲驗(yàn)證的設(shè)計(jì)與忽略延遲的綜合實(shí)現(xiàn)之間不匹配。本系列文章只展示零延遲示例。

左側(cè)類型。連續(xù)賦值語句的左側(cè)可以是標(biāo)量(1位)或向量,也可以是變量類型,也可以是用戶定義的類型。左側(cè)不能是未壓縮的的結(jié)構(gòu)體或未壓縮的數(shù)組。

在連續(xù)賦值語句的左側(cè)使用網(wǎng)絡(luò)或變量之間有一個(gè)重要區(qū)別:

-

網(wǎng)絡(luò)類型(如wire或tri)可以由多個(gè)源驅(qū)動(dòng),包括多個(gè)連續(xù)分配、多個(gè)模塊或基本實(shí)例的輸出或輸入端口連接,或驅(qū)動(dòng)的任意組合。

-

變量類型(如var或int)只能從單個(gè)源分配一個(gè)值,可以是:?jiǎn)蝹€(gè)輸入端口、單個(gè)連續(xù)賦值語句或任意數(shù)量的過程賦值(多個(gè)過程賦值被視為單個(gè)源;綜合器要求多個(gè)過程賦值在同一個(gè)過程中)。

請(qǐng)注意,logic關(guān)鍵字推斷出一種數(shù)據(jù)類型,但其本身不是網(wǎng)絡(luò)或變量類型。當(dāng)logic本身被使用時(shí),一個(gè)變量被推斷出來,并附帶單個(gè)源賦值限制)。當(dāng)使用logic關(guān)鍵字聲明輸出模塊端口時(shí),也會(huì)推斷出一個(gè)變量。當(dāng)使用logic關(guān)鍵字聲明輸入或inout模塊端口時(shí),將推斷出具有多個(gè)驅(qū)動(dòng)程序功能的wire類型。

| 最佳實(shí)踐指南7-1 |

|---|

| 在連續(xù)賦值的左側(cè)使用變量,為防止無意中出現(xiàn)多個(gè)驅(qū)動(dòng),只有打算讓一個(gè)信號(hào)有多個(gè)驅(qū)動(dòng)時(shí),才在左側(cè)使用wire或tri。 |

僅當(dāng)需要多個(gè)驅(qū)動(dòng)時(shí)使用網(wǎng)絡(luò)類型(如wire或tri),例如共享總線、三態(tài)總線或inout雙向模塊端口。

對(duì)于RTL建模,語義規(guī)則的一個(gè)重要優(yōu)點(diǎn)是變量只能有一個(gè)來源。ASIC和FPGA設(shè)備中的大多數(shù)信號(hào)大多數(shù)為單源邏輯,但三態(tài)總線和雙向端口除外。變量的單源限制有助于防止無意中的編碼錯(cuò)誤,如果對(duì)具有變量類型的同一信號(hào)進(jìn)行多個(gè)連續(xù)賦值語句或連接,則多源編碼錯(cuò)誤將在仿真和綜合中報(bào)告為編譯或布線錯(cuò)誤。

向量寬度不匹配。連續(xù)賦值語句的左側(cè)可以是與右側(cè)的信號(hào)或表達(dá)式結(jié)果不同寬度的向量大小。出現(xiàn)這種情況時(shí),SystemVerilog會(huì)自動(dòng)調(diào)整右側(cè)的向量寬度,以匹配左側(cè)的大小。如果右側(cè)的向量寬度大于左側(cè),則右側(cè)的最高有效位將被截?cái)酁樽髠?cè)的大小。如果右側(cè)是較小的向量寬度大小,則右側(cè)值將向左擴(kuò)展到左側(cè)的大小。如果表達(dá)式或運(yùn)算結(jié)果是無符號(hào)的,則左擴(kuò)展將用0擴(kuò)展。如果右側(cè)表達(dá)式或運(yùn)算結(jié)果是有符號(hào)的,則將使用符號(hào)擴(kuò)展。

| 最佳實(shí)踐指南7-2 |

|---|

| 確保連續(xù)賦值語句和程序賦值的兩側(cè)向量寬度相同。避免左側(cè)向量大小和右側(cè)向量大小不匹配 。 |

在一些特例的情況下,賦值的右側(cè)和左側(cè)有不同大小的向量。這方面的一個(gè)例子是變量旋轉(zhuǎn)操作(variable rotate operation)前面有介紹過,可以查看之前的文章。

顯式和隱式推斷的連續(xù)賦值語句

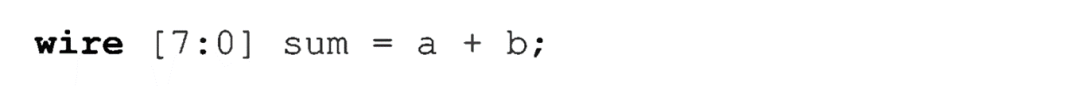

連續(xù)賦值語句有兩種形式:顯式連續(xù)賦值語句和隱式連續(xù)賦值語句。顯式連續(xù)賦值語句是用assign關(guān)鍵字聲明的,如前面的代碼段和示例所示。這種形式的連續(xù)賦值語句既可以賦值給網(wǎng)絡(luò)類型,也可以賦值給變量類型。隱式連續(xù)賦值語句將網(wǎng)絡(luò)類型的聲明與連續(xù)賦值語句相結(jié)合。即使未使用assign關(guān)鍵字,這種形式的連續(xù)性質(zhì)也是可以推斷出來的。

推斷網(wǎng)絡(luò)聲明賦值示例如下:

請(qǐng)注意,推斷網(wǎng)絡(luò)聲明賦值語句與變量初始化語句不同,例如:

變量初始化只執(zhí)行一次,而推斷網(wǎng)絡(luò)聲明賦值是一個(gè)過程,每當(dāng)右側(cè)表達(dá)式上的值發(fā)生變化時(shí),就會(huì)更新左側(cè)網(wǎng)絡(luò)。推斷網(wǎng)絡(luò)聲明賦值語句是可綜合的。

多次連續(xù)賦值語句

一個(gè)模塊可以包含任意數(shù)量的連續(xù)賦值語句。每個(gè)連續(xù)賦值語句都是一個(gè)單獨(dú)的過程,與其他連續(xù)賦值語句并行運(yùn)行。所有連續(xù)賦值語句從仿真時(shí)間零點(diǎn)開始計(jì)算右側(cè)運(yùn)算,并運(yùn)行到仿真結(jié)束。

一個(gè)模塊中的多個(gè)過程分配可用于表示數(shù)據(jù)流行為,其中功能是用布爾方程建模的,布爾方程使用SystemVerilog操作符產(chǎn)生輸出,而不是使用過程編程語句。在RTL模型中,數(shù)據(jù)流賦值表示數(shù)據(jù)在寄存器之間流動(dòng)的組合邏輯。

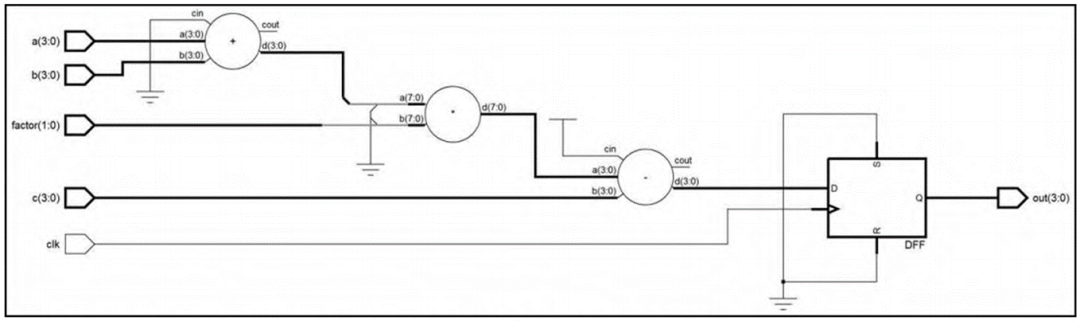

下面的示例使用連續(xù)賦值語句來仿真通過加法器、乘法器和減法器的數(shù)據(jù)流。該數(shù)據(jù)流的結(jié)果在時(shí)鐘每個(gè)正邊緣被存儲(chǔ)在寄存器中:

//`begin_keywords"1800-2012"//useSystemVerilog-2012keywords

moduledataflow

#(parameterN=4)//bussize

(inputlogicclk,//scalarinput

inputlogic[N-1:0]a,b,c,//scalableinputsize

inputlogic[1:0]factor,//fixedinputsize

outputlogic[N-1:0]out//scalableoutputsize

);

timeunit1ns;timeprecision1ns;

logic[N-1:0]sum,diff,prod;

assignsum=a+b;

assigndiff=prod-c;

assignprod=sum*factor;

always@(posedgeclk)

out<=?diff;

endmodule:?dataflow

//`end_keywords

因?yàn)槟K中的多個(gè)連續(xù)賦值語句并行運(yùn)行,所以RTL源代碼中賦值的順序沒有區(qū)別。這可以通過比較示例7-1中連續(xù)賦值語句的順序和圖7-1所示的綜合結(jié)果中的數(shù)據(jù)流順序看出來。RTL代碼按加法、減法、乘法的順序列出賦值語句,但操作的數(shù)據(jù)流是加法、乘法、減法。

同時(shí)使用連續(xù)賦值語句和always程序

一個(gè)模塊可以包含連續(xù)賦值語句和always程序的組合。

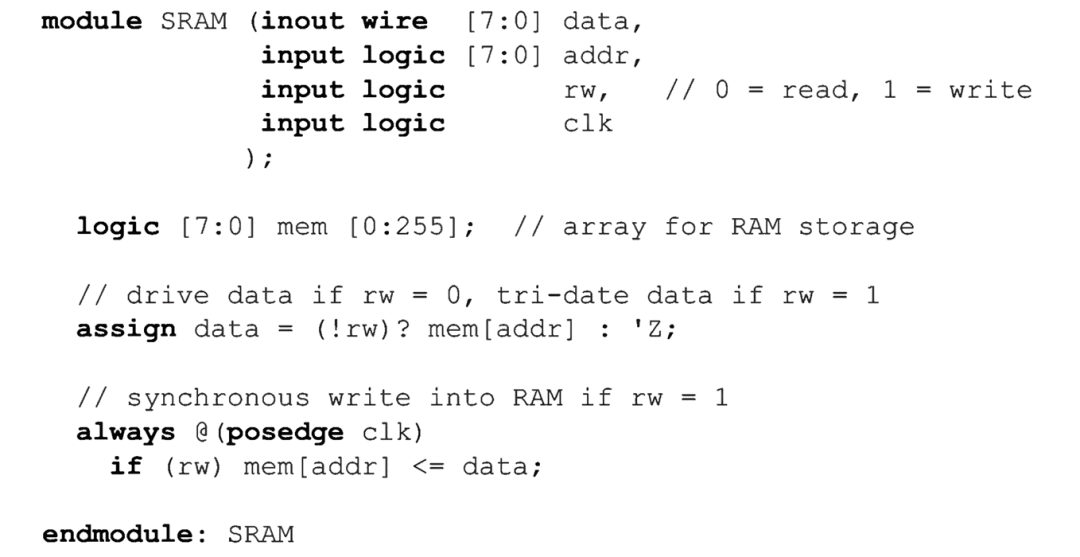

下面的簡(jiǎn)單示例演示了一個(gè)帶有雙向數(shù)據(jù)總線的靜態(tài)RAM。當(dāng)從RAM讀取數(shù)據(jù)時(shí),數(shù)據(jù)總線作為輸出端口被驅(qū)動(dòng)——當(dāng)不被讀取時(shí),數(shù)據(jù)總線被分配高阻態(tài),以便其他設(shè)備可以驅(qū)動(dòng)該總線,連續(xù)賦值語句用于仿真輸出功能,以及always程序用于仿真輸入功能(方便在時(shí)鐘上升沿觸發(fā))。

數(shù)據(jù)總線是一個(gè)雙向inout端口,必須是網(wǎng)絡(luò)類型,如wire或tri,才能有多個(gè)驅(qū)動(dòng)源。當(dāng)數(shù)據(jù)總線是RAM的輸出時(shí),它可以由RAM驅(qū)動(dòng),當(dāng)數(shù)據(jù)總線是RAM的輸入時(shí),它可以由其他模塊驅(qū)動(dòng)。只有連續(xù)賦值語句才能分配給網(wǎng)絡(luò)數(shù)據(jù)類型。

每個(gè)連續(xù)賦值語句和每個(gè)always程序都是一個(gè)單獨(dú)的并行過程,從仿真時(shí)間零點(diǎn)開始,在整個(gè)仿真過程中運(yùn)行。模塊中連續(xù)賦值語句和always程序的順序并不重要,因?yàn)檫@些程序是并行運(yùn)行的。

審核編輯 :李倩

-

鎖存器

+關(guān)注

關(guān)注

8文章

919瀏覽量

42007 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4365瀏覽量

63850 -

數(shù)據(jù)總線

+關(guān)注

關(guān)注

2文章

61瀏覽量

17775

原文標(biāo)題:數(shù)字硬件建模SystemVerilog-組合邏輯建模(1)連續(xù)賦值語句

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

VirtualLab Fusion應(yīng)用:漸變折射率(GRIN)鏡頭的建模

VIRTUALLAB FUSION中具有復(fù)雜擴(kuò)展區(qū)域的光波導(dǎo)器件建模

VirtualLab:系統(tǒng)建模分析器

全內(nèi)反射棱鏡(TIR)的建模

VirtualLab Fusion:系統(tǒng)建模分析器

VirtualLab:系統(tǒng)建模分析器

VirtualLab Fusion應(yīng)用:Herriott池的建模與仿真

如何通過建模與仿真提升電力電子組件的設(shè)計(jì)與性能?

【「數(shù)字IC設(shè)計(jì)入門」閱讀體驗(yàn)】+目錄和前2章

知識(shí)分享 | 輕松實(shí)現(xiàn)優(yōu)質(zhì)建模

通向數(shù)字創(chuàng)新之路:25個(gè)組合電路核心主題概念

數(shù)字硬件建模SystemVerilog-組合邏輯建模(1)連續(xù)賦值語句

數(shù)字硬件建模SystemVerilog-組合邏輯建模(1)連續(xù)賦值語句

評(píng)論