由于測試芯片的復(fù)雜性和覆蓋范圍的原因,單個小芯片對復(fù)合材料成品率下降的影響正在為晶圓測試帶來新的性能要求。從測試的角度來看,使小芯片成為主流技術(shù)取決于確保以合理的測試成本獲得“足夠好的模具”。

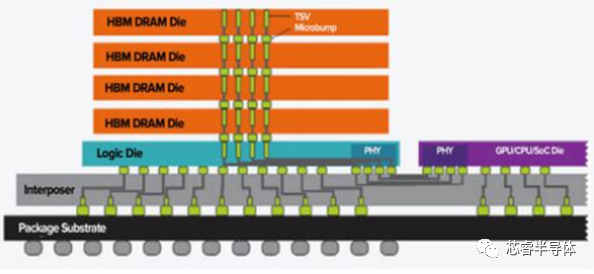

晶圓級測試在小芯片制造過程中扮演著至關(guān)重要的角色。以HBM(高帶寬內(nèi)存)為例,它可以及早發(fā)現(xiàn)有缺陷的DRAM和邏輯芯片,以便可以在復(fù)雜而昂貴的堆疊階段之前將其刪除。堆疊后晶圓的進一步測試可確保完成的堆疊在切割成獨立組件之前具有完整的功能。理想情況下,每個DRAM芯片在堆疊之前都應(yīng)進行已知良好芯片(KGD)測試,以獨立驗證其性能。但這在經(jīng)濟上通常是不可行的。在某些時候,測試成本超過了系統(tǒng)完成后增加的價值。 因此,需要一種平衡測試成本和未做芯片不良率檢測的測試策略,以將異構(gòu)集成引入大批量生產(chǎn)。

得益于MEMS探針卡技術(shù)的創(chuàng)新,F(xiàn)ormFactor的產(chǎn)品可以幫助客戶實現(xiàn)全流程的KGD測試(例如支持45μm柵格陣列間距微凸點測試的Altius探針卡,用于高速HBM和Interposer插入連接器的良品率驗證),并且可以接受有限的測試成本(例如SmartMatrix探針卡,通過同時測試300mm晶圓上的數(shù)千個芯片,大大降低了每個芯片的測試成本)。最終,我們在小型芯片制造過程的每個階段獲得有關(guān)產(chǎn)品性能和成品率的更多信息,從而幫助客戶降低總體制造成本。

審核編輯 :李倩

-

晶圓

+關(guān)注

關(guān)注

52文章

5130瀏覽量

129280 -

芯片制造

+關(guān)注

關(guān)注

10文章

681瀏覽量

29589

原文標(biāo)題:探針臺測試,從晶圓測試角度來看,使小芯片(Chiplet)成為主流技術(shù)所面臨的最大挑戰(zhàn)是什么?

文章出處:【微信號:gh_064d56de9e11,微信公眾號:芯睿半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Chiplet與先進封裝設(shè)計中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進封裝

Chiplet技術(shù)的優(yōu)勢和挑戰(zhàn)

全面剖析倒裝芯片封裝技術(shù)的內(nèi)在機制、特性優(yōu)勢、面臨的挑戰(zhàn)及未來走向

Chiplet:芯片良率與可靠性的新保障!

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Chiplet技術(shù)革命:解鎖半導(dǎo)體行業(yè)的未來之門

Chiplet技術(shù)有哪些優(yōu)勢

UCIe規(guī)范引領(lǐng)Chiplet技術(shù)革新,新思科技發(fā)布40G UCIe IP解決方案

薄膜發(fā)電為什么不能成為主流

國產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

剖析 Chiplet 時代的布局規(guī)劃演進

天合光能:TOPCon組件成為主流,700W+大勢所趨

使小芯片(Chiplet)成為主流技術(shù)所面臨的最大挑戰(zhàn)是什么?

使小芯片(Chiplet)成為主流技術(shù)所面臨的最大挑戰(zhàn)是什么?

評論