來源:半導體芯科技編譯

IMEC公司CMOS技術高級副總裁Sri Samavedam回顧了重要的半導體行業(yè)趨勢。哪些是未來幾年將在工業(yè)界推出的邏輯CMOS縮放的新創(chuàng)新?利用晶圓背面向器件輸送電力是下一個將被引入的主要性能提升器。晶圓正面的傳統(tǒng)金屬層將用于信號路由,而晶圓背面的金屬層將用于電力傳輸。分離電源傳輸和信號路由可以降低電源的壓降(從而提高性能),并減少正面金屬路由的擁擠。英特爾已經(jīng)宣布,他們將在2納米節(jié)點上用nanosheet器件引入這一技術。

TEM圖像顯示了連接到晶圓背面和正面的按比例的FinFET。

超越nanosheet和forksheet的器件架構是互補型FET(CFET),其中N和P器件使用復雜的集成方式堆疊在一起。有幾種類型的CFET是可能的,而我們正處于尋找路徑的早期階段。在后端金屬化方面,銅的雙大馬士革集成將讓位于高縱橫比金屬蝕刻,以形成低于20納米間距的線路。我們一直專注于實現(xiàn)釕的直接金屬蝕刻。為了降低電阻,釕的長寬比隨著氣隙的增大而增大,以減少電容影響。這些變化將確保后端RC(電阻-電容)的擴展路線圖在幾個節(jié)點上繼續(xù)進行。

邏輯和存儲器組件的擴展越來越難。節(jié)點對節(jié)點的改進正在減少,甚至由于集成的復雜性,成本繼續(xù)增加。在設計方面,有一種趨勢是為每個功能創(chuàng)造更多特定領域的加速器,如神經(jīng)處理、圖形、視頻等,并更加注重硬件-軟件共同優(yōu)化,以便在系統(tǒng)層面上獲得更多。

還有一種動力是尋找特定的技術來解決系統(tǒng)瓶頸,如內(nèi)存墻(如何以高帶寬獲得數(shù)據(jù),并以足夠的速度和足夠低的功率為邏輯核心提供數(shù)據(jù))、電源墻(如何有效地處理電力輸送和散熱)或數(shù)據(jù)通信瓶頸(如何確保有線、光子學和無線基礎設施能夠處理成倍增長的數(shù)據(jù)流量),而不是依賴現(xiàn)成的通用技術。

在高性能計算領域有一些例子,如AMD的V-cache技術,其中3D集成被用來使額外的SRAM內(nèi)存更接近CPU。另一個例子是在蘋果M1 Ultra系統(tǒng)芯片(SoC)中使用硅插橋來連接兩個CPU芯片。還有一個強大的推動力是利用不同的3D和2.5D技術對電子和光子IC進行聯(lián)合封裝,以減少光IO系統(tǒng)中數(shù)據(jù)帶寬增加時的寄生電阻。當涉及到3D和2.5D連接時,有幾種選擇,取決于連接的密度、成本和復雜性。設備、計量和EDA基礎設施也需要成熟,以推動標準化和降低成本,以便更廣泛地采用。

IMEC的設計技術共同優(yōu)化(DTCO)計劃致力于在邏輯、內(nèi)存和三維方面的設計基準,為未來節(jié)點建立有技術影響的工藝設計工具包(PDK)。在系統(tǒng)技術共同優(yōu)化(STCO)計劃中,我們使用這些研究PDK來解決系統(tǒng)挑戰(zhàn),如內(nèi)存墻和電源墻。例如,我們致力于特定領域SoC的3D分區(qū),并進行多尺度熱分析,包括不同的冷卻解決方案和混合存儲器的實現(xiàn)。

為了解決3D技術的成熟問題,我們正與關鍵設備供應商密切合作,并與Cadence公司合作,以實現(xiàn)SoC的真正3D分區(qū)所需的電子設計自動化(EDA)工具。

您能舉出一些IMEC正在關注的有前景的CMOS研發(fā)課題的例子嗎?

在邏輯方面,我們繼續(xù)探索和測試實現(xiàn)CFET器件的各種集成和模塊選項,預計這將實現(xiàn)4T標準單元的設計。在后端,在高縱橫比比金屬線中加入氣隙以實現(xiàn)RC擴展方面取得了進展。在量子計算領域,我們致力于降低硅自旋量子比特器件的電荷噪聲,這對量子計算的高保真量子比特操作是非常有希望的。

在后道,在高縱橫比金屬線中加入氣隙以實現(xiàn)RC擴展方面取得了進展。

隨著光IO支持的數(shù)據(jù)速率的增加,電子IC和光子IC更緊密地結合在一起,使用協(xié)同封裝的光學器件來減少寄生。我們正在開發(fā)新的模塊,使協(xié)同封裝的光學技術成為現(xiàn)實。

在有源存儲器項目中,我們繼續(xù)提高IGZO(氧化銦鎵鋅)器件的性能和可靠性,這將在未來按比例的DRAM架構中發(fā)揮關鍵作用。在我們的存儲項目中,我們繼續(xù)推動用于存儲應用的傳統(tǒng)全門控三維NAND閃存的擴展路線圖。

IMEC對可持續(xù)發(fā)展采取了廣泛和全面的方法。在我們的運營中,我們計劃到2030年將我們的碳足跡減少65%,我們正在朝著這個目標順利推進。此外,我們以強大的安全文化促進健康的工作和生活平衡,并將聯(lián)合國可持續(xù)發(fā)展目標作為研究項目的指南針。我們在綠色氫氣和光伏等可再生能源的生產(chǎn)方面進行研究。

去年,我們啟動了可持續(xù)半導體技術和系統(tǒng)(SSTS)計劃,旨在量化和減輕半導體制造在邏輯、內(nèi)存和三維集成流程中的碳足跡。

我們的目標是匯集整個半導體生態(tài)系統(tǒng),以應對這一全球挑戰(zhàn)。到目前為止,幾個領先的合作伙伴,如蘋果、亞馬遜、微軟、ASM、ASML、Kurita, Screen、東京電子已經(jīng)加入這一計劃。我們希望很快宣布其他幾個設備、代工廠和系統(tǒng)合作伙伴。我們正在與SEMI可持續(xù)發(fā)展咨詢委員會合作,廣泛分享學習成果和最佳實踐,以鼓勵行業(yè)領導者采用。

關于Sri Samavedam

Sri Samavedam自2019年8月起擔任IMEC的CMOS技術高級副總裁。他的職責包括邏輯、存儲器、光子學和三維集成方面的項目。在此之前,他是位于紐約州馬耳他的GlobalFoundries的技術開發(fā)高級總監(jiān),在那里他領導了14納米FinFET技術和衍生產(chǎn)品進入批量生產(chǎn)的資格認證以及7納米CMOS的早期開發(fā)。他的研究生涯開始于德克薩斯州奧斯汀的摩托羅拉公司,從事應力硅、金屬柵極、高k電介質(zhì)和全耗盡SOI器件的研究。他擁有麻省理工學院的材料科學與工程博士學位和普渡大學的碩士學位。

審核編輯黃昊宇

-

半導體

+關注

關注

334文章

27515瀏覽量

219791

發(fā)布評論請先 登錄

相關推薦

求問帖!靜電消除器在電子半導體領域的具體應用與需求!

2025年全球半導體八大趨勢,萬年芯蓄勢待發(fā)

AI驅(qū)動聞泰科技半導體業(yè)務持續(xù)增長

半導體行業(yè)加速國產(chǎn)替代,萬年芯多種產(chǎn)品受關注

聞泰科技榮獲年度功率半導體產(chǎn)品獎

芯和半導體將出席SiP及先進半導體封測技術論壇

中國半導體專利申請激增,萬年芯134項專利深耕行業(yè)

聞泰科技榮獲“2023年中國半導體行業(yè)功率器件十強企業(yè)”

半導體發(fā)展的四個時代

半導體發(fā)展的四個時代

功率半導體:現(xiàn)代電子工業(yè)的“心臟”與未來趨勢

盤點2024年半導體行業(yè)8大發(fā)展趨勢 #半導體發(fā)展趨勢 #半導體行業(yè) #半導體封裝核心部件 #ZR電機

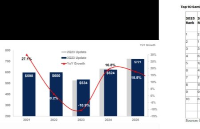

半導體行業(yè)產(chǎn)業(yè)趨勢詳細報告

【芯聞時譯】半導體行業(yè)的趨勢

【芯聞時譯】半導體行業(yè)的趨勢

評論