本應(yīng)用筆記討論如何有效保護(hù)ADC,使其免受運(yùn)算放大器驅(qū)動(dòng)器引起的輸入過(guò)壓的影響。新型MAX44205為180MHz、低噪聲、低失真、全差分ADC驅(qū)動(dòng)器,內(nèi)置箝位功能,使驅(qū)動(dòng)器輸出擺幅保持在ADC的額定電源范圍內(nèi)。

介紹

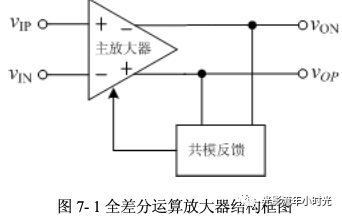

具有超低失真和噪聲的高性能、全差分運(yùn)算放大器對(duì)于實(shí)現(xiàn)高分辨率和低總諧波失真(THD)至關(guān)重要。運(yùn)算放大器(我們?cè)谶@里簡(jiǎn)稱(chēng)為驅(qū)動(dòng)器)在ADC的前端執(zhí)行各種操作。驅(qū)動(dòng)程序處理緩沖和幅度縮放。它將單端輸入轉(zhuǎn)換為差分輸出,為ADC的差分輸入供電。它通過(guò)VOCM引腳上的電壓設(shè)置來(lái)調(diào)整ADC的共模輸入信號(hào),并對(duì)信號(hào)進(jìn)行濾波。

在本應(yīng)用筆記中,我們將說(shuō)明如何有效保護(hù)ADC免受運(yùn)算放大器驅(qū)動(dòng)器引起的輸入過(guò)壓的影響。新型MAX44205為180MHz、低噪聲、低失真、全差分ADC驅(qū)動(dòng)器,內(nèi)置箝位功能,使驅(qū)動(dòng)器輸出擺幅保持在ADC的額定電源范圍內(nèi)。這種硬箝位可保護(hù)ADC免受其輸入端過(guò)壓的影響;該驅(qū)動(dòng)器和ADC之間無(wú)需額外的外部分立元件即可實(shí)現(xiàn)箝位保護(hù)。與傳統(tǒng)的保護(hù)二極管方法相比,這種設(shè)計(jì)節(jié)省了空間和成本。

保護(hù)ADC免受輸入過(guò)壓影響的重要性

由于高性能ADC價(jià)格高,系統(tǒng)設(shè)計(jì)人員必須選擇能夠保護(hù)ADC免受過(guò)壓影響的驅(qū)動(dòng)器。當(dāng)今的18位/20位ADC使用的基準(zhǔn)電壓/電源電壓不超過(guò)3.3V,但ADC驅(qū)動(dòng)器通常使用±5V分離電源或更高的電壓。驅(qū)動(dòng)器 V 上的負(fù)電壓黨衛(wèi)軍引腳用于適應(yīng)整個(gè)ADC軌到軌輸入信號(hào)擺幅。這里有一個(gè)警告。根據(jù)驅(qū)動(dòng)器的輸入信號(hào),其輸出可能遠(yuǎn)遠(yuǎn)超出ADC輸入電源。如果我們不將驅(qū)動(dòng)器輸出電壓箝位到ADC電源電壓以?xún)?nèi),ADC可能會(huì)永久損壞。

市場(chǎng)上的大多數(shù)ADC在兩個(gè)電源軌的輸入端都有ESD保護(hù)二極管,但這些二極管在永久損壞之前無(wú)法處理>20mA至50mA量級(jí)的電流超過(guò)幾秒鐘。即使長(zhǎng)時(shí)間通過(guò)內(nèi)部ESD二極管泄漏也會(huì)損壞保護(hù)二極管和ADC。

大多數(shù)設(shè)計(jì)人員在驅(qū)動(dòng)器輸出端使用齊納二極管或肖特基二極管來(lái)限制ADC的輸入信號(hào)擺幅。該鉗位解決方案需要四個(gè)分立二極管和限流電阻。還有另一種選擇。MAX44205為180MHz、低噪聲、低失真、全差分運(yùn)算放大器驅(qū)動(dòng)器,內(nèi)置箝位,將輸出擺幅限制在ADC電源范圍內(nèi)。因此,它可以保護(hù)ADC免受輸入端過(guò)壓的影響。該驅(qū)動(dòng)器的鉗位特性省去了四個(gè)額外的分立元件,節(jié)省了PCB空間和成本。

離散地實(shí)施夾緊

設(shè)計(jì)人員使用肖特基二極管來(lái)箝位ADC輸入電壓。這是一個(gè)很好的方法,因?yàn)檫@些二極管提供~0.25V至0.4V的最低正向壓降電壓,具體取決于流經(jīng)它們的電流。肖特基二極管還有其他三個(gè)重要優(yōu)點(diǎn):1)非常低的反向漏電流;2)寄生電容較小;3)非常快的反向恢復(fù)時(shí)間。在肖特基二極管的這三個(gè)優(yōu)點(diǎn)中,低反向漏電流和較小的寄生電容在精密ADC應(yīng)用中至關(guān)重要。第三個(gè)優(yōu)點(diǎn)是快速反向恢復(fù)時(shí)間,當(dāng)二極管進(jìn)入箝位和箝位的速度至關(guān)重要時(shí)非常有用。

雖然肖特基二極管的寄生電容很小,但設(shè)計(jì)人員必須選擇電容隨施加到二極管的反向電壓變化變化最小的二極管。這種非線(xiàn)性效應(yīng)對(duì)于諧波失真很重要的應(yīng)用至關(guān)重要。

齊納二極管還用于箝位電壓,其中需要粗箝位 工作時(shí),齊納二極管具有較高的反向漏電流,使其對(duì)ADC應(yīng)用的效率較低。

圖1顯示了使用肖特基二極管在ADC輸入端實(shí)現(xiàn)預(yù)定電壓電平的電壓箝位的基本方法。

圖1.帶肖特基二極管的基本電壓鉗位方案。

圖1使用兩個(gè)BAT42 Vishay?肖特基二極管。當(dāng)ADC驅(qū)動(dòng)器輸出超出正ADC電源時(shí),正電源電壓的每個(gè)輸出上的兩個(gè)肖特基二極管開(kāi)始導(dǎo)通;二極管將這些節(jié)點(diǎn)的電壓電平維持在3.3V,加上這些二極管的正向壓降。請(qǐng)注意,肖特基二極管的正向壓降電壓因二極管的功率處理能力而異。因此,應(yīng)選擇具有較低正向壓降規(guī)格且正向連續(xù)電流規(guī)格適合應(yīng)用的肖特基二極管。

在四個(gè)電阻中,R限制限制流過(guò)肖特基二極管并進(jìn)入穩(wěn)壓器提供的 3.3V 電源軌的電流。R系列保護(hù)ADC的內(nèi)部ESD保護(hù)二極管。設(shè)計(jì)人員必須調(diào)整這些電阻的尺寸,以將電流保持在應(yīng)用的可管理水平。

R型限制電阻還有助于減少流入穩(wěn)壓器的電流,即3.3V電源軌。如果不限制此電流,穩(wěn)壓器的輸出電壓可能會(huì)增加,并使用電路板的相同穩(wěn)壓器輸出電源損壞其他IC。如果您知道ADC驅(qū)動(dòng)器的電流不能超過(guò)~100mA,則有另一種方法。不要對(duì)串聯(lián)電阻使用限流電阻。驅(qū)動(dòng)器和ADC之間的RC抗混疊濾波器將通過(guò)外部肖特基二極管的電流限制在~10mA的可管理水平。

所以重復(fù)一遍,R限制電阻有助于限制流入 3.3V 電源軌的電流。此外,它們與肖特基二極管電容一起形成低通濾波器,并將滾降電路帶寬響應(yīng)。對(duì)于需要更高帶寬的ADC應(yīng)用,這是一個(gè)問(wèn)題,不利于ADC工作。

保護(hù)電路示例

使用外部肖特基二極管進(jìn)行硬箝位

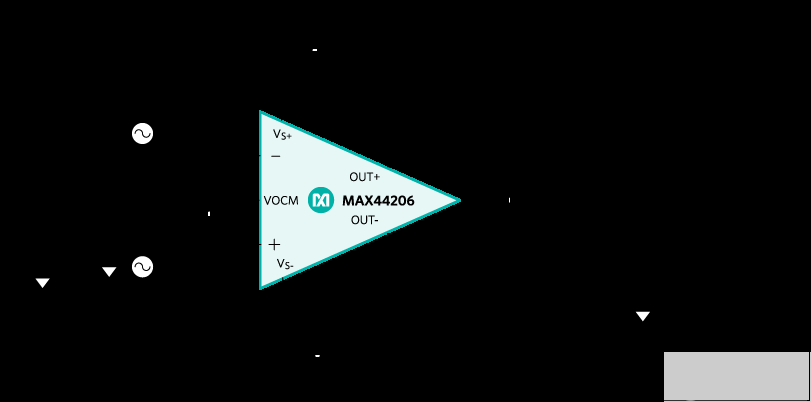

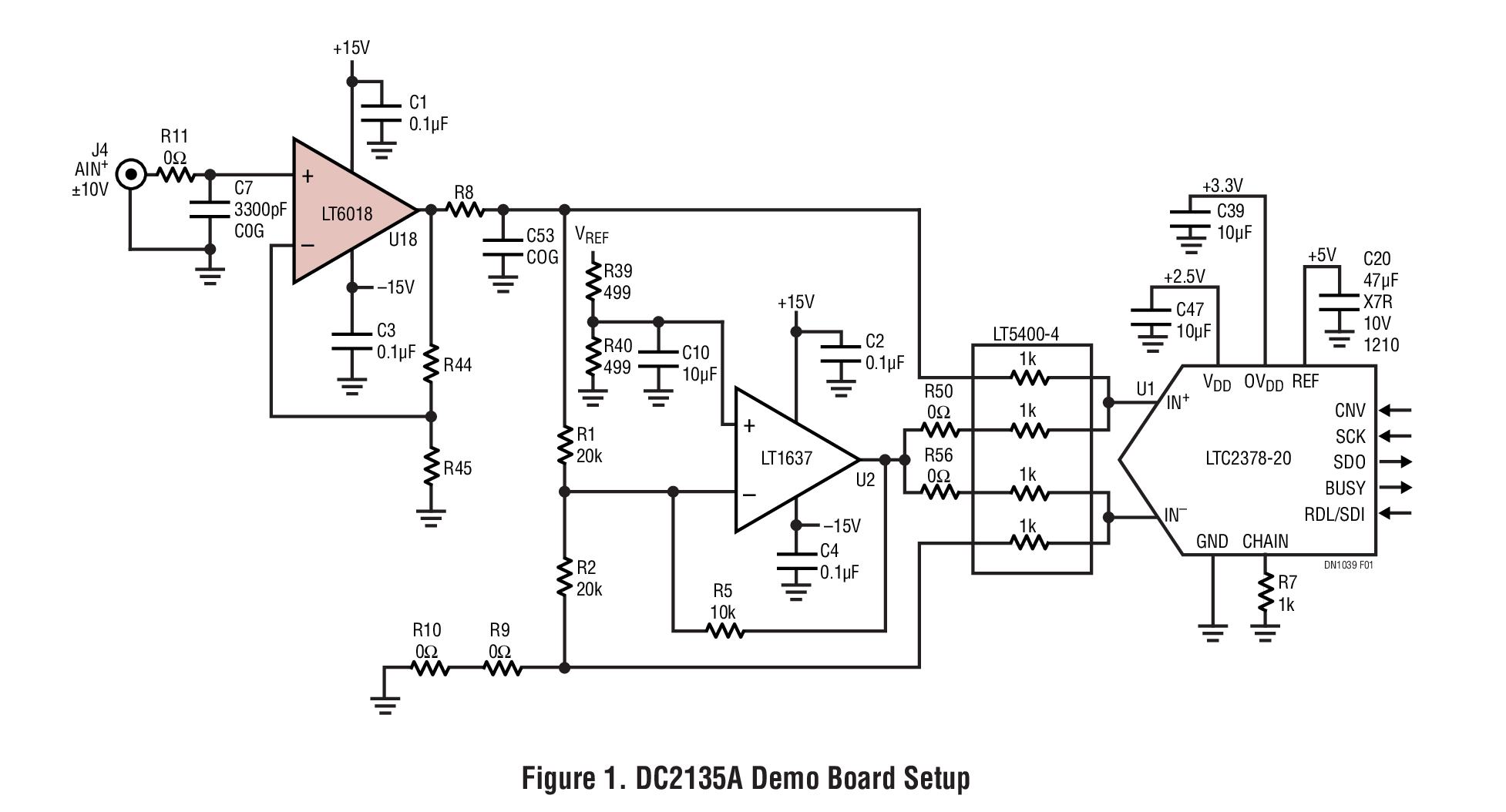

現(xiàn)在,我們將展示一個(gè)使用四個(gè)肖特基二極管(圖2)的電路,該電路可保護(hù)ADC免受驅(qū)動(dòng)器輸出過(guò)壓的影響。高性能16位至20位ADC需要一個(gè)低噪聲、低失真驅(qū)動(dòng)器,以保持輸入信號(hào)的質(zhì)量并保持ADC的整體轉(zhuǎn)換精度。這里,一對(duì)7.5Ω電阻和一個(gè)1nF電容構(gòu)成一個(gè)抗混疊濾波器,提供21.22MHz截止頻率。為簡(jiǎn)潔起見(jiàn),我們不討論低通濾波器元件的尺寸,本應(yīng)用筆記僅限于ADC過(guò)壓保護(hù)。

圖2.采用四個(gè)外部肖特基二極管箝位驅(qū)動(dòng)器輸出可保護(hù)ADC免受驅(qū)動(dòng)器輸出過(guò)壓的影響。

圖2所示為MAX44206運(yùn)算放大器,配置為增益 = 1V/V差分放大器配置,采用±5V分離電源,VOCM = 1.65V。每個(gè)輸出均經(jīng)過(guò)直流電平轉(zhuǎn)換至1.65V,即ADC的中軌,以利用ADC的0V至3.3V全轉(zhuǎn)換范圍。±5V 分離電源允許驅(qū)動(dòng)器在整個(gè) 0V 至 3.3V 轉(zhuǎn)換范圍內(nèi)提供輸出電壓擺幅。驅(qū)動(dòng)器輸入端使用的輸入信號(hào)的幅度通常相等,異相180,以實(shí)現(xiàn)最大的差分輸出信號(hào)擺幅。現(xiàn)在每個(gè)輸出都直流電平轉(zhuǎn)換到1.65V,每個(gè)輸出將具有基于180相分離的輸入的等幅信號(hào)擺幅。°°

在我們的實(shí)驗(yàn)中,我們執(zhí)行了兩個(gè)測(cè)試用例:

1. 每個(gè)輸出的輸出電壓擺幅設(shè)置為3.3VP-P帶 1.65V直流偏見(jiàn)

每個(gè)輸入為 3.3VP-P具有180相分離;實(shí)際差分輸入電壓(V°英迪夫) 兩路輸入為 6.6VP-P.由于增益 = 1V/V,因此每個(gè)輸出也是 3.3VP-P具有 180 相分離和 6.6V°P-P輸出兩端的差分電壓(

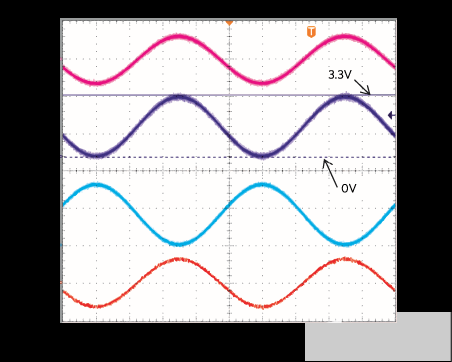

圖 3

)。

圖3.圖2電路的輸出瞬態(tài)響應(yīng)。這里 VIN+= 3.3VP-P和 VHNL= VIN+-180;VOCM =1.65V。°

圖3示波器圖顯示,每個(gè)輸出上尚未開(kāi)始箝位動(dòng)作,因?yàn)槊總€(gè)輸出上的最大和最小電壓分別為3.3V和0V,如V所示外曲線(xiàn)。可以理解的是,二極管尚未導(dǎo)通以保護(hù)ADC。

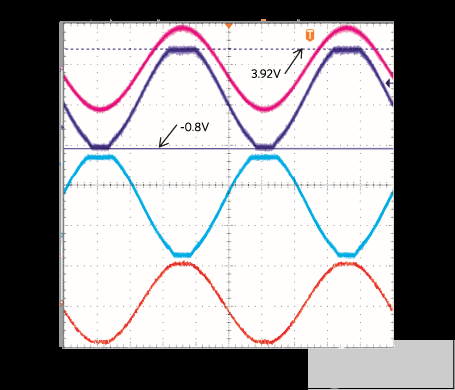

2. 每個(gè)輸出端的輸出電壓擺幅設(shè)置為5VP-P帶 1.65V直流偏見(jiàn)

每個(gè)輸入為 5VP-P具有 a180 相分離(圖 4)。實(shí)際差分輸入電壓(V°英迪夫) 兩路輸入為 10VP-P.由于增益 = 1V/V,每個(gè)輸出應(yīng)為 5VP-P同相分離180次;一個(gè) 10V°P-P預(yù)計(jì)輸出兩端的差分電壓。5VP-P每個(gè)輸出上具有 1.65VDC 偏置意味著輸出擺幅在 4.15V 和 -0.85V 之間。實(shí)際上,只要每個(gè)輸出超過(guò)3.3V加上二極管的正向壓降,二極管就會(huì)導(dǎo)通,開(kāi)始導(dǎo)通,并將驅(qū)動(dòng)器輸出箝位至3.92V。類(lèi)似地,二極管將驅(qū)動(dòng)器輸出箝位至-0.8V。

圖4.圖2電路的輸出瞬態(tài)響應(yīng),具有硬箝位功能。這里 VIN+= 5VP-P和 VHNL= 5VP-P;VHNL= VIN+-180°;V中氯= 3.3V;V中電= 0V;VOCM = 1.65V。

在圖2設(shè)置中,肖特基二極管導(dǎo)通時(shí),硬鉗位狀態(tài)下消耗的電源電流約為15mA。大多數(shù)ADC的輸入電壓的絕對(duì)最大額定值高于供電軌0.3V,低于供電軌0.3V。

硬箝位,無(wú)需外部分立二極管

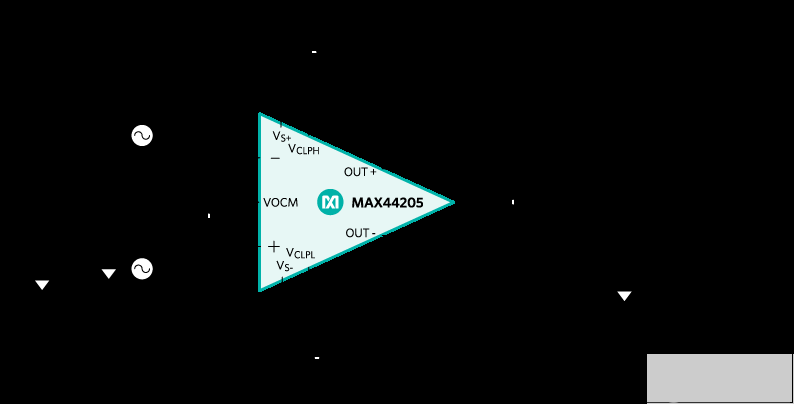

現(xiàn)在,我們將展示一個(gè)電路(圖5),該電路無(wú)需外部二極管即可保護(hù)ADC免受驅(qū)動(dòng)器輸出過(guò)壓的影響。該解決方案不僅節(jié)省了PCB空間,還節(jié)省了肖特基二極管的額外成本。圖5與圖2幾乎相同,只是沒(méi)有四個(gè)二極管。

圖5所示的MAX44205運(yùn)算放大器具有兩個(gè)輸出箝位引腳:V中氯和 V中電可用于將輸出電壓電平限制在預(yù)定電壓。當(dāng)ADC電源軌連接到這些箝位引腳時(shí),驅(qū)動(dòng)器輸出被箝位在ADC電源軌內(nèi),與施加到驅(qū)動(dòng)器的輸入擺幅無(wú)關(guān)。

圖5.在該電路中,驅(qū)動(dòng)器輸出被箝位,無(wú)需外部肖特基二極管或分立元件。

同樣,我們執(zhí)行了兩個(gè)測(cè)試用例:

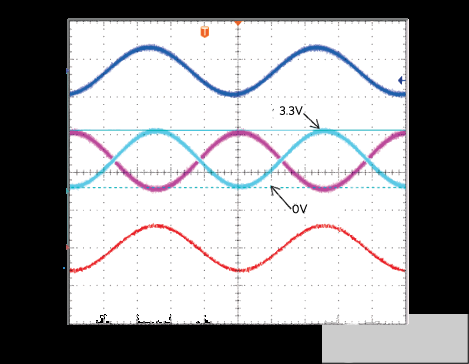

1. 每個(gè)輸出的輸出電壓擺幅設(shè)置為3.3VP-P帶 1.65V直流偏見(jiàn)

同樣,每個(gè)輸入為3.3VP-P具有 180 相分離(圖 6)。由于增益 = 1V/V,因此每個(gè)輸出也是 3.3V°P-P具有 180 相分離。在示波器圖中(圖6),驅(qū)動(dòng)器的每個(gè)輸出擺幅在3.3V至0V之間,與ADC電源軌完全相同,因此,到目前為止沒(méi)有箝位動(dòng)作。°

圖6.圖5電路的輸出瞬態(tài)響應(yīng)(帶V)IN+= 3.3VP-P和 VHNL= 3.3VP-P;VS+= +5V;VS-= -5V;VHNL= VIN+-180;VOCM = 1.65V。°

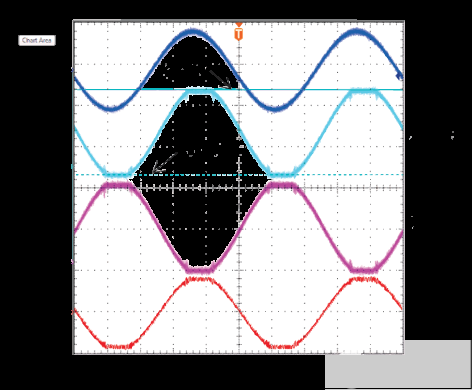

2. 每個(gè)輸出端的輸出電壓擺幅設(shè)置為5VP-P帶 1.65V直流偏見(jiàn)

每個(gè)輸入為 5VP-P具有180相分離;實(shí)際差分輸入電壓(V°英迪夫) 在兩個(gè)輸入端為 10VP-P,如圖 7 所示。由于增益 = 1V/V,每個(gè)輸出應(yīng)為 5VP-P具有 180 相分離。再次,5V°P-P理論上,每個(gè)輸出上的1.65VDC偏置意味著輸出擺幅在4.15V和-0.85V之間。MAX44205運(yùn)算放大器在正擺幅上箝位輸出和限值為3.72V,在負(fù)擺幅上將限值箝位至-0.4V,如V所示輸出+跟蹤(圖7)。

圖7.圖5電路上硬箝位時(shí)的輸出瞬態(tài)響應(yīng)。這里 VIN+= 5VP-P和 VHNL= 5VP-P;VS+= +5V;VS-= -5V;VHNL= VIN+-180;VOCM = 1.65V。°

MAX44205運(yùn)算放大器具有專(zhuān)有的箝位機(jī)制,在硬箝位狀態(tài)下通過(guò)VCLPL僅消耗92μA電流。相比之下,使用圖4中的分立設(shè)計(jì)進(jìn)行箝位時(shí),箝位為10毫安。MAX44205在箝位時(shí)的輸出電壓限值為V中氯+ 0.34 和 V中電- 0.42.不建議精確地箝位ADC的電源軌,因?yàn)轵?qū)動(dòng)器輸出需要擺動(dòng)至任一ADC軌而不會(huì)失真。如果驅(qū)動(dòng)器輸出正好箝位在V中氯和 V中電,當(dāng)輸出位于ADC電源時(shí),箝位可能會(huì)導(dǎo)通,從而導(dǎo)致失真。

審核編輯:郭婷

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8654瀏覽量

149493 -

運(yùn)算放大器

+關(guān)注

關(guān)注

217文章

5687瀏覽量

176256 -

adc

+關(guān)注

關(guān)注

99文章

6671瀏覽量

548712

發(fā)布評(píng)論請(qǐng)先 登錄

全差分運(yùn)算放大器結(jié)構(gòu)框圖解析 常見(jiàn)的全差分運(yùn)算放大器電路分析

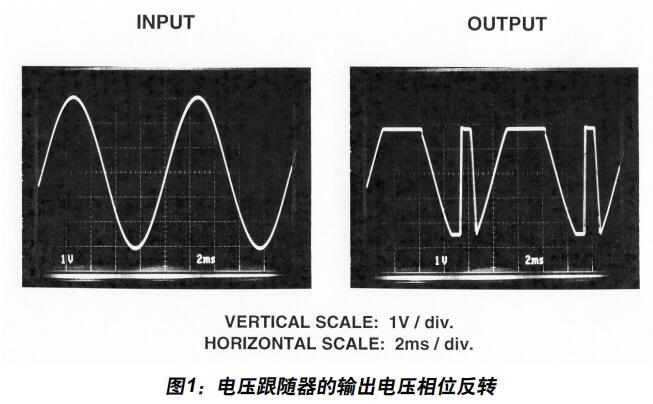

運(yùn)算放大器輸出相位反轉(zhuǎn)和輸入過(guò)壓保護(hù)PDF

基于LTC6363差分運(yùn)算放大器/ADC驅(qū)動(dòng)器的DC2319A-A

【模擬對(duì)話(huà)】運(yùn)算放大器輸入過(guò)壓保護(hù):箝位與集成

運(yùn)算放大器輸入過(guò)壓保護(hù):箝位與集成

低噪聲精密運(yùn)算放大器驅(qū)動(dòng)高分辨率SAR ADC詳解

差分運(yùn)算放大器板的資料分享

高性能運(yùn)算放大器與ADC的接口設(shè)計(jì)

驅(qū)動(dòng)高分辨率 SAR ADC

低噪聲精密運(yùn)算放大器驅(qū)動(dòng)高分辨率 SAR ADC

MT-036:運(yùn)算放大器輸出相位反轉(zhuǎn)和輸入過(guò)壓保護(hù)

運(yùn)算放大器輸出相位反轉(zhuǎn)和輸入過(guò)壓保護(hù)

LTC6362:精密、低功耗軌對(duì)軌輸入/輸出差分運(yùn)算放大器/SAR ADC驅(qū)動(dòng)器數(shù)據(jù)表

低噪聲、高精度運(yùn)算放大器驅(qū)動(dòng)高分辨率SAR/ADC

低噪聲、精密運(yùn)算放大器驅(qū)動(dòng)高分辨率SAR ADC

差分運(yùn)算放大器驅(qū)動(dòng)器可保護(hù)高分辨率ADC免受輸入過(guò)壓影響

差分運(yùn)算放大器驅(qū)動(dòng)器可保護(hù)高分辨率ADC免受輸入過(guò)壓影響

評(píng)論