電磁干擾 (EMI) 和電磁兼容性 (EMC) 測試是汽車應用中串行器/解串器 (SerDes) 器件設計驗證的重要組成部分。EMI和EMC必須在設計周期的早期考慮,以防止不必要的設計修改。以下應用筆記詳細介紹了有關如何準備SerDes系統進行EMI/EMC測試的有用基本概念和指南。

介紹

LCD視頻顯示器在汽車應用中變得越來越普遍。堅固的設計、小尺寸和低成本使其成為安全、導航和信息娛樂系統的理想選擇。LCD 顯示器是數字的,每個像素都使用離散的數字值運行。由于驅動這些顯示器的媒體/圖形源通常也是數字的,因此數字鏈路是將視頻源與顯示器連接的最簡單和最高性能的方法。此視頻鏈路的數字通道必須提供高帶寬。例如,640 x 480 像素的彩色顯示器以 30fps(每秒幀數)的速度運行。每個紅色、綠色和藍色像素只有 6 位分辨率,相應的數據速率為 640 x 480 x 30 x 18 = 166Mbps。實際傳輸速度必須快一點,因為正常運行需要消隱時間。許多顯示器具有更多的像素和/或每比特更多的像素,從而迅速提高此比特率。然后,串行器/解串器(SerDes)芯片組獲取并行數字數據并將其串行化以進行傳輸。有些器件,如MAX9209串行器,將紅色、綠色和藍色數據分開,導致三種原色各有一個串行通道,時鐘各有一個通道。其它器件,如MAX9247串行器,將這些數據組合成一個串行通道,并帶有嵌入式時鐘信號。這兩種方法都顯著提高了傳輸的基頻。雖然頻率的增加會導致問題,但很容易為串行信號提供適當的屏蔽和阻抗匹配的傳輸介質。

電磁干擾測試

EMI測試在汽車應用中是必要的,以確保選定的系統不會損壞它們周圍的其他系統。對輻射發射和傳導發射進行測試。輻射發射測試主要利用天線并檢查系統通過自由空間輻射到其他系統的能力。設計不當的SerDes系統可能無法滿足EMI規范。相比之下,傳導輻射測試主要使用系統電源線上的電壓和電流探頭完成。由于SerDes系統很少直接連接到電源線,因此傳導輻射很少成為問題。

電磁兼容測試

與EMI測試類似,汽車應用中的EMC測試是為了確保系統不會被其他外圍系統損壞。由于當今汽車中有大量的電子系統,所有這些系統都具有寬頻譜的電流、阻抗和工作頻率,這一點非常重要。用于EMC測試的大電流注入(BCI)對被測系統來說特別粗糙。盡管BCI測試規范和方法因汽車制造商而異,但它們通常涉及從幾MHz到1GHz頻率的強大外部場。

像素時鐘頻率選擇

正確的像素時鐘選擇會對EMI產生重大影響。與任何高速數字設備一樣,SerDes視頻鏈路在時鐘頻率的整數諧波下輻射可檢測的EMI水平。在汽車應用中,EMI輻射的極限隨頻率而變化。許多汽車制造商在特定頻段上規定了相當嚴格的限制。例如,433MHz是用于遙控無鑰匙進入(RKE)的頻率,通常是EMI規范中最嚴格的區域之一。考慮到像素時鐘頻率為33MHz的系統,13次諧波位于429MHz,這可能會導致433MHz RKE頻段的干擾。選擇略低的32.7MHz頻率可將13次諧波移至425MHz,從而產生更舒適的頻率裕量。

線路板電磁干擾/電磁兼容測試的常用要素

將任何IC接地都是一項重要的設計實踐。然而,對于SerDes系統來說,它是至關重要的。所有接地引腳必須具有低阻抗,并連接到實心接地層。不建議將PCB分成多個平面。PCB元件側的銅澆注平面,加上緊靠下方的連續銅平面,是標準做法。使頂部銅澆注遠離匹配的阻抗走線。保持差分對的走線到走線間距至少 3 倍是一種好方法。

考慮每個接地連接使用多個過孔。過孔的寄生電感是導致非理想行為的重要因素。接地過孔加倍可降低電感,從而提高性能。

繞過任何 IC 通常都很重要,但對于 SerDes 系統來說,這一點非常重要。與接地建議類似,電源引腳必須看到來自電源的低交流阻抗。對于低壓差分信號 (LVDS) 線路、I/O 電源引腳和用于鎖相環 (PLL) 電路的電源引腳尤其如此。建議每個引腳使用兩個旁路電容。這兩個電容器的值通常相差 10 倍至 100 倍(例如,0.1μF 和 1nF)。最小的電容應最靠近它必須去耦/旁路的電源引腳。

考慮在SerDes系統的電源引腳上使用鐵氧體磁珠。同樣,這對于LVDS線路、I/O電源引腳和PLL電源引腳特別實用,但這可以應用于任何電源引腳。鐵氧體磁珠可減少高頻能量的進出。選擇峰值阻抗為100Ω至600Ω且額定電流至少為100mA的鐵氧體磁珠。

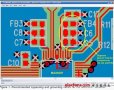

圖1所示為使用MAX9247串行器的PCB布局特寫。感興趣的組件是FB4,C6和C5,它們排列在一列中,其絲網印刷參考標志位于相應組件輪廓的右側。圖1底部是MAX9247的一角。FB4的右側端子通過過孔連接到嵌入式接地層。FB4的左端向下連接C6和C5,然后連接到MAX9247的引腳27,即串行器的V中聯會電源節點。請注意,連接FB4、C5和C6的走線保持寬,以實現較低的電感。為了滿足MAX9247的引腳間距,該走線變窄,因此在C5和MAX9247之間使用一個小的銅多邊形,以保持走線盡可能寬,但又盡可能靠近串行器。此外,C5和C6的接地表明每個電容器都有自己的接地層通孔(每個組件的右側)。頂部銅層充斥著地,提供從C6和C5到MAX9247引腳26的直接低電感路徑,引腳26是串行器的PLLGND。

特定于序列化程序的建議

防止串行器輻射EMI需要一些基本概念。通常,串行器對EMC測試不是特別敏感;但是,其輸出需要具有恒定阻抗的平衡傳輸對。大多數串行器IC針對100Ω阻抗進行了優化。如果由設計中的不可更改元素決定,則接近此范圍的其他值是可以接受的。如果串行器輸出離開盒子并進入汽車的線束,則這些輸出必須承受電池短路。最簡單的解決方案是用一個 0.1μF 電容器對每個輸出進行交流耦合。然而,為此,需要直流平衡串行器,如MAX9209、MAX9217或MAX9247。也可以使用非直流平衡器件,但系統設計必須確保從外部提供所需的偏置電壓,這通常不是一種實用的方法。最后,串行器輸出端通常在串行器離開PCB之前包含一個共模扼流圈。這提供了一定的保護,防止串流器組件發出的共模噪聲。然而,共模扼流圈通常只能提供非常小的改進,并且不應在其插入損耗(標稱值為1dB)可能損害鏈路可靠性的情況下使用。

圖1.推薦MAX9247串行器的旁路和接地細節。

特定于反序列化程序的建議

與串行器一樣,防止解串器輻射EMI需要測試/設計工程師遵循一些基本概念和指南。保護解串器組件免受EMC事件的影響還需要審查一些基本概念,因為解串器可能容易受到EMC的影響,并且還可能輻射EMI。

共模扼流圈通常包含在解串器的輸入端,靠近差分信號進入PCB的位置。共模扼流圈有助于最大限度地減少共模噪聲的拾取。共模扼流圈在系統選擇的工作頻率下必須具有低差分插入損耗。解串器輸入需要具有恒定阻抗的平衡傳輸對。大多數解串器器件針對100Ω阻抗進行了優化,但如果由設計中的不可更改元件決定,則接近此范圍的其他值是可以接受的。

如果解串器輸入需要交流耦合,則可以在共模扼流圈之后完成。同樣,這些電容僅用于直流平衡解串器,如MAX9236和MAX9248。差分對要求端接到盡可能靠近接收器側IC的100Ω差分阻抗。雖然差分阻抗保持在100Ω,但共模阻抗也必須保持較低水平。可以使用戴維南端接系統,也可以使用一對50Ω電阻與中間節點串聯到地。這兩種方法如圖 2 所示。使用一對50Ω電阻是EMI/EMC測試的首選方法,因為:

它允許IC設置自己的直流偏置,

它不注入 V抄送噪聲進入終端,以及

它不消耗任何功率。

圖2.正確LVDS端接的方法(左:戴維寧配置;右:串行50Ω電阻配置)。

連接器和線束

SerDes系統中使用的連接器和電纜被認為是系統的關鍵部分,它們對EMI和EMC測試的影響是巨大的。汽車應用中的常見做法是,PCB插座和電纜連接器通常來自鏈路兩側的單一制造商。連接器必須保持恒定的阻抗,并提供屏蔽接口以優化性能。此外,它們必須只允許單個插入極性和正向鎖定,以保證可制造性和可靠性。

電纜也必須提供恒定的阻抗,其線束需要重屏蔽以防止輻射。如果使用多對電纜,則每對電纜都需要單獨的屏蔽。無處不在的 CAT5 電纜通常不足以用于汽車 SerDes。

許多制造商都提供連接器和電纜系統。

在某些系統中,連接器的屏蔽僅在鏈路的一側接地,另一側通過電容器(通常為0.1μF)接地。這種耦合可防止由于接地電位的差異而導致電纜屏蔽層中的直流電流流動。

其他電磁干擾源

SerDes視頻鏈路中的另一個EMI源是解串器的輸出。這些輸出是具有相對高速邊沿的CMOS邏輯電平。如果CMOS邏輯輸出未正確屏蔽,它們也會引起EMI輻射。降低LCD面板邏輯信號EMI的好方法是使用采用擴頻技術的解串器,如MAX9242、MAX9244、MAX9246、MAX9248或MAX9250。 這些解串器提供多種工作模式、數據寬度和工作頻率,以滿足大多數系統要求。

審核編輯:郭婷

-

顯示器

+關注

關注

21文章

5065瀏覽量

141384 -

emi

+關注

關注

53文章

3715瀏覽量

130341 -

emc

+關注

關注

172文章

4120瀏覽量

186020

發布評論請先 登錄

音頻/視頻接口的EMI/EMC抑制

符合EMIEMC標準的SerDes—基本測試策略和指南

EMI/EMC就緒型SerDes—基本測試策略和指南

EMI/EMC就緒型SerDes—基本測試策略和指南

評論