電源排序是數(shù)字電源架構(gòu)的關鍵組件。在這篇文章中,我們將介紹幾種構(gòu)建排序的方法及其后果。特別是,我們將看到設計選擇如何影響設計過程后期的靈活性。

電源轉(zhuǎn)換的構(gòu)建模塊

讓我們來看看我們的電源構(gòu)建塊和工具,看看我們可以為自己制造什么樣的麻煩。為了簡單起見,讓我們假設我們有一個通用電源模塊(UPB),以及所有常見的罪魁禍首,如FPGA和微控制器以及邏輯。我們的UPB有一個簡單的界面:

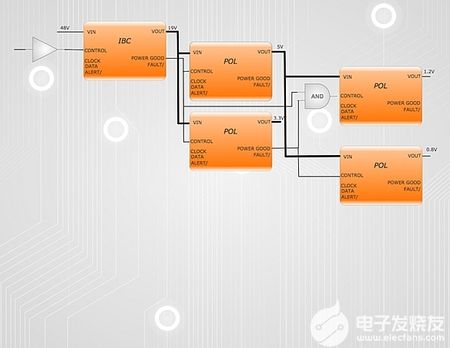

圖1.電源塊

我們簡單的電源轉(zhuǎn)換器具有單V在/V外、一個 PMBus 接口、一個輸入信號:控制,以及兩個輸出信號:電源良好和故障/。

控制

控制信號打開和關閉輸出。它是高電平有效,具有內(nèi)部上拉。

電源良好

當輸出通電時,電源良好信號為高電平,并且在有效范圍內(nèi)。

故障/

FAULT/信號為低電平有效,漏極開路,并在電源模塊發(fā)生故障時置位。如果存在故障,則斷言 ALERT/,并且可以通過 PMBus 讀取故障。并非所有電源轉(zhuǎn)換器都會同時具有電源良好和故障/,我們不需要兩者。在幾乎所有情況下,F(xiàn)AULT/都可以成為POWER GOOD的特技替身。

設計一

現(xiàn)在讓我們構(gòu)建一些東西,這樣我們就可以拆除它并構(gòu)建另一個,每次都變得更好。

假設我們有一個帶有中間總線控制器 (IBC) 和以下導軌的系統(tǒng):

785

295

5.0V

3.3V

1.2V

0.8V

我們決定將軌道構(gòu)建為層次結(jié)構(gòu)。但是,我們需要不同的上電控制結(jié)構(gòu)。

圖2.簡單的電源結(jié)構(gòu)

不要擔心權(quán)力層次結(jié)構(gòu)是否正確,或者邏輯對于任何實際設計是否正確。重要的是這種“類型”結(jié)構(gòu)的影響。讓我們考慮一下這樣做的利弊。

在專業(yè)方面,這很簡單,無論是在概念上還是在實現(xiàn)上。使用 FPGA 或 uP 的 GPIO 添加 LED 指示燈或讀取電源良好非常容易。如果出現(xiàn)問題,電源良好會讓系統(tǒng)知道軌道出現(xiàn)故障。

在缺點方面,如果發(fā)生故障,并且系統(tǒng)必須關閉所有電源,則別無選擇,只能按照上電的順序關閉它們。這意味著大多數(shù)下游電源軌將因斷電而不是控制引腳而斷電。

沒有時序控制,因此必須添加額外的電路以在電源軌之間產(chǎn)生延遲。如果在電源軌之間添加了延遲,則該延遲僅適用于通電,因為在斷電時,饋線導軌上的斷電將在 POWER GOOD 將其斷開之前將其從屬電源軌斷開。

如果你對這種“類型”的結(jié)構(gòu)犯了任何錯誤, PCB將需要重新布局, 當你在等待的時候, 你別無選擇,只能在你的設計上破解電線, 或者去喝一個很長的咖啡休息時間.

設計二

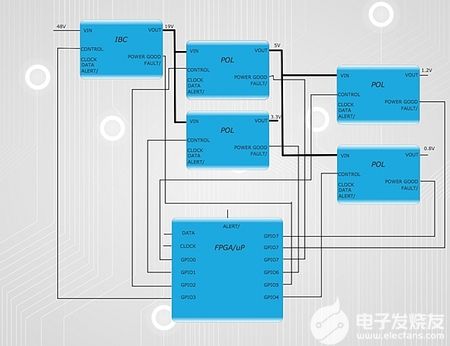

如果我們集中邏輯,我們可以做得更好。可編程器件(如FPGA或uP)可以管理所有邏輯。

帶控制器的電源結(jié)構(gòu)

由于所有邏輯線都路由到 GPIO,控制器可以完全控制排序順序(打開和關閉),并完全控制時序。只要愿意更改Verilog或C代碼,就可以更改它。我已經(jīng)在控制器上指示了 PMBus,但沒有繪制所有連接,但使用 PMBus,控制器現(xiàn)在還可以控制電平和故障行為。

在專業(yè)方面,這種設計很靈活,你不會被困住。如果在控制結(jié)構(gòu)中出錯,可以在不重新布局的情況下修復它。

在缺點方面,您必須更改Verilog或C,并可能重新測試和重新鑒定固件。這種設計還需要大量的路由。每個 POL 需要 5 條控制線,它們分別路由到控制器。假設我們有一個 20 個軌道系統(tǒng),考慮到 PMBus,它需要 42 個 GPIO 引腳。

所以這種設計是靈活的,但需要大量的GPIO和大量的PCB空間。

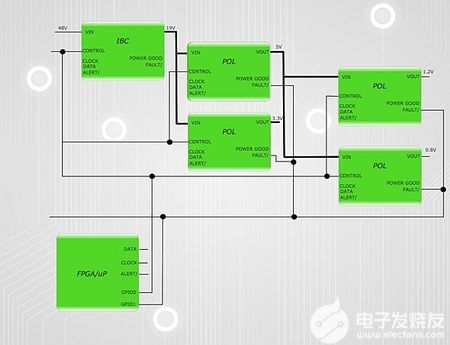

設計三

當與 PMBus 和智能數(shù)字電源 POL 結(jié)合使用時,我們可以通過使用開漏控制的特性來簡化控制器。

簡化的控制器

所有控制引腳都連接在一起,所有故障/引腳連接在一起。這意味著一個 20 個軌道系統(tǒng)只需要 5 個連接。IO 引腳數(shù)量減少了 8 倍。

讓我們看看這是如何工作的。控制引腳為高電平有效。它由 GPIO0 控制,GPIO0 設置為“漏極開路”。由于控制引腳為漏極開路,這意味著POL也可以將其拉低。

當POL復位時,它將控制引腳拉低,直到它準備好響應外部信號。這意味著,如果控制器速度太快,則在全部正確復位之前,所有 POL 都不會打開,最慢的 POL 復位確定系統(tǒng)何時通電。如果控制器速度較慢,則在釋放控制線時控制電源啟動。

您可能想知道排序。我們是否失去了對它的控制?否,因為 PMBus 具有TON_DELAY命令,其值通常存儲在 POL 的 NVM 中。它可以由控制器設置,也可以使用外部工具存儲在 NVM 中。

故障/引腳也是漏極開路,由GPIO1控制,它們既是輸入又是輸出。這意味著當任何電源軌發(fā)生故障時,當FAULT引腳被拉低時,所有電源軌都會得到通知。此外,當故障/被拉低時,警報/斷言。因此,控制器知道存在故障。每個人都知道,這是這個設計的關鍵。

現(xiàn)在,您可以選擇幾個有關故障處理的選項。PMBus 可以使用警報響應地址 (ARA) 響應 ALERT/,該地址獲取具有故障的所有 POL 的地址,然后查詢每個 POL 以獲取故障信息。然后,它可以使用決策樹,并根據(jù)需要以任何順序關閉軌道。或者它可以一次關閉所有電源軌,讓PMBus TOFF_DELAY管理時序。

許多POL具有增強的故障管理功能,可以直接響應故障(請記住,F(xiàn)AULT/也是一個輸入)。典型的響應是:

重試

立即關閉

斜坡關閉

當POL具有這些高級功能時,它減輕了Verilog或C代碼的負擔,因為POL可以使用外部工具(通過PMBus和外部接口和軟件)進行編程。此外,當使用FAULT/引腳時,對故障的響應比處理ALERT/的響應要快得多。

設計三的權(quán)衡

如果您有增強的 POL,則可以進行權(quán)衡。如果故障邏輯對于共享故障/線路來說太復雜,只需添加一個控制器。如果故障邏輯很簡單,則可以使用工具配置故障行為,而無需控制器。或者,您可以使用控制器進行遙測和其他功能,但使用 FAULT/ 引腳進行故障處理,如果您發(fā)現(xiàn)它無法處理所有情況,您可以隨時添加用于故障處理的代碼并進行更改。

控制引腳也有類似的權(quán)衡。您也可以使用 PMBus 來代替它。在這種情況下,CONTROL引腳仍會保持導通狀態(tài),直到所有POL完成復位。

當控制引腳和故障引腳共享時,最大的靈活性,并且PMBus有一個控制器。通過這種設計, PCB制造后具有完全的靈活性.

電源良好

如果你沒有注意到,我沒有使用電源好。在打開另一個軌道之前,您不需要知道一條軌道何時良好。如果一個軌道都由TON_DELAY控制,而a沒有及時準備好,就會出現(xiàn)故障。PMBus 定義了TON_MAX_FAULT_LIMIT,它定義了鋼軌必須爬坡并在公差范圍內(nèi)的時間。如果此時某個導軌不在規(guī)格范圍內(nèi),則會發(fā)生故障,這將阻止其他導軌打開。

設計原則是:沒有消息就是好消息。如果系統(tǒng)需要知道所有電源軌何時啟動,您只需要一個簡單的計時器,設置為所有TON_DELAYs定義的最長時間。或者,控制器可以對最后一個 POL 的狀態(tài)等進行 PMBus 查詢。

在某些器件中,故障/引腳可以重新配置為電源良好引腳。這允許您在確實需要時擁有電源良好,但故障共享引腳丟失。因此,您可能需要控制器來響應警報/。或者在更簡單的系統(tǒng)中,ALERT/可以抓住控制引腳并在出現(xiàn)故障時關閉所有電源軌。

在實踐中,電源良好通常不是必需的。但是,如果您真的想要一個,您通常可以重新配置 FAULT/。畢竟,總有特殊情況。也許總有空間容納“通用適配器套件”。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17836瀏覽量

251796 -

控制器

+關注

關注

112文章

16445瀏覽量

179451 -

總線

+關注

關注

10文章

2903瀏覽量

88394

發(fā)布評論請先 登錄

相關推薦

超聲設計考慮及靈活性實現(xiàn)

實現(xiàn)汽車測功器應用的靈活性

電源系統(tǒng)設計中靈活性和可配置性的好處

多軌電源設計的排序

EVAL-PRAOPAMP-2RMZ,為不同的應用電路和配置提供多種選擇和廣泛的靈活性

EVAL-PRAOPAMP-4RZ,為不同的應用電路和配置提供多種選擇和廣泛的靈活性

嵌入式Linux的靈活性

集成與靈活性是通往最佳電源管理架構(gòu)之路

介紹 LTM9100 的特性及靈活性

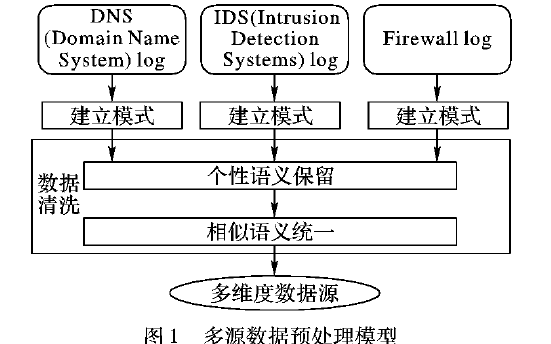

如何解決多源數(shù)據(jù)融合分析過程靈活性差和處理效率低的問題方法說明

數(shù)字電源排序設計選擇如何影響設計過程后期的靈活性

數(shù)字電源排序設計選擇如何影響設計過程后期的靈活性

評論