手機上LPDDR5怎么看不到繞線等長設計?頻率越來越高,為什么DDR繞線等長的要求卻越來越低了?其實從LPDDR3開始,手機上很少有見到夸張的繞線了,都是直接芯片公司提供的DOME板來Copy線的。

最早是做X86架構的電腦主機板的,DDR部分要單獨分出一個人力來繞線的。

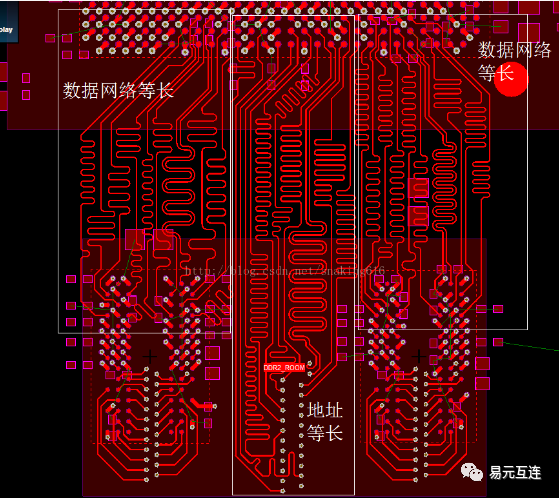

首先,DDR繞線等長要考慮芯片內部長度(Pin Delay),也就是僅僅保證CPU到DDR的Pin to Pin的長度相等是不行的,要考慮CPU和DDR內部的芯片內部焊接長度Pin Delay,而且CLK線的長度要比Data線長出200mil左右。

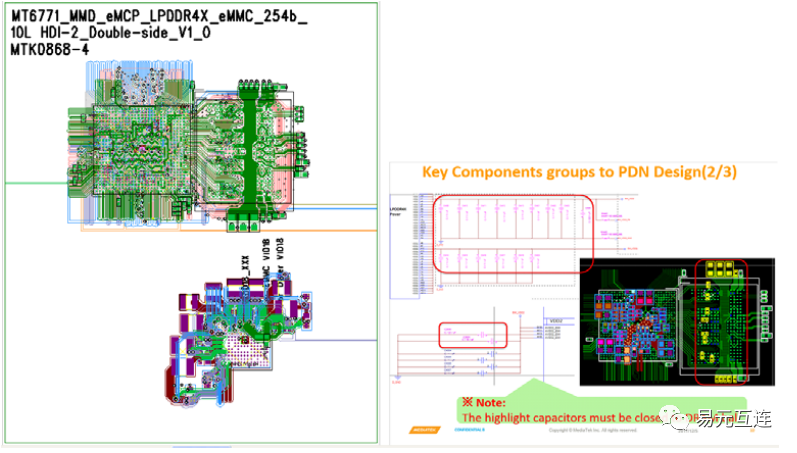

圖 1DDR繞線的PCB圖

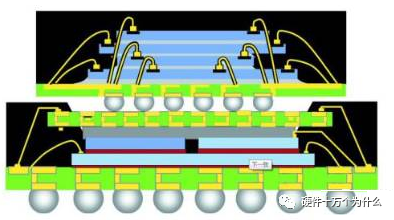

元件堆疊裝配(PoP, Package on Package), 在底部元器件上面再放置元器件,邏輯+存儲通常為2到4層,存儲型PoP可達8層。

外形高度會稍微高些,但是裝配前各個器件可以單獨測試,保障了更高的良品率,總的堆疊裝配成本可降至最低。器件的組合可以由終端使用者自由選擇, 對于3G移動電話,數碼像機等這是優選裝配方案。

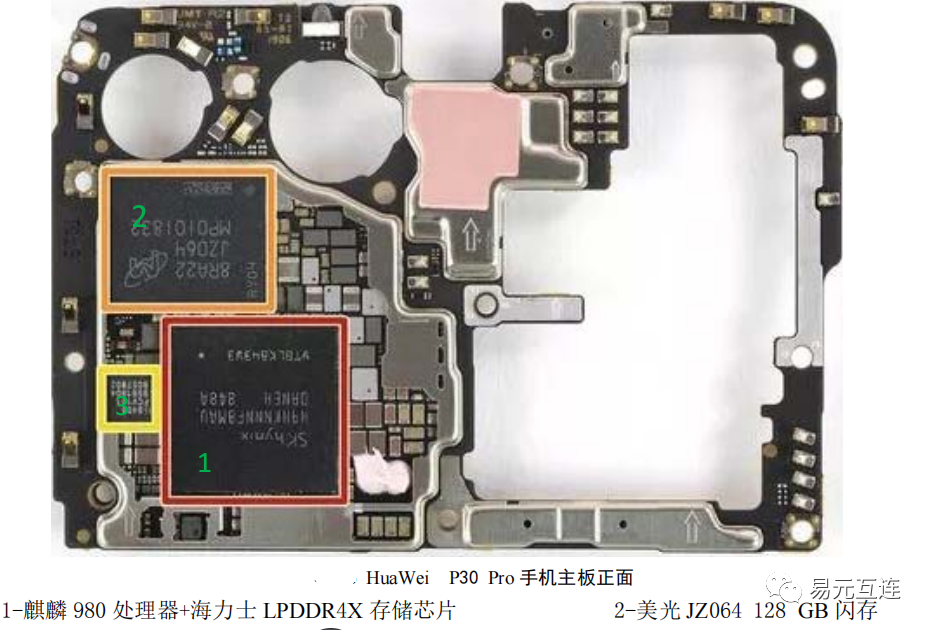

從LPDDR4開始,手機線路板上大多使用POP焊接工藝,直接焊接在CPU的背部焊盤上,很少有見到在PCB板子上的,比如華為的P30,可以看到DDR的空間被一顆EMMC替代,DDR4和CPU已經使用POP工藝立體疊裝在同一個地方了。

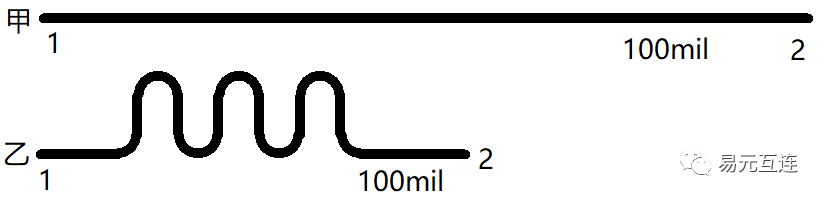

圖 2CPU與DDR的POP立體貼裝工藝 那究竟為什么到DDR5,頻率提高了,反而很少繞線了呢?答案是:不是不繞,而是繞了等長也沒用。為了解答這個問題,不妨先一起來做一個仿真的習題。 【題目】下圖有甲乙兩根都是100mil的信號線,如果各有一個高電位信號開始從1傳輸到2,哪根線的2端先收到信號? 圖 3

圖 3

【A】甲2先收到 【B】乙2先收到 【C】同時收到

如果把信號線當作一個高速公路,電荷是一輛車(當然電荷移動速度是很慢的),那肯定是直線路況最好,車速最快,應該選A;如果考慮到電流的速度都是按照6mil/ps,那就是雖然有拐彎,但整體路線長度是一樣的,到達時間應該也是一樣的,應該選C。

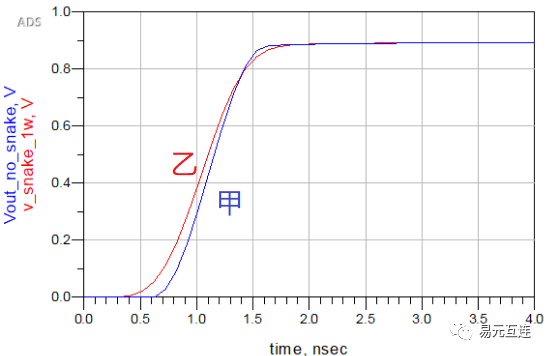

那到底是A還是C呢?使用ADS來對這兩根信號線進行仿真,下圖為仿真結果,藍色和紅色分別是甲和乙的時域波形圖,可以看到乙剛開始一直領先的,在上升到0.8的時候,甲開始追上乙,然后提前到達0.9的高度上。至于為什么沒有達到1那是另外一個問題,咱們不做考慮,那結果就是甲先到達了嗎?當然不是這么簡單的,衡量一個信號至高電平,一般下限為70%,也就是高電平是1V,到達0.7V就可以達到置1的效果,就像咱們考試,達到60分就及格了,不一定非要人人100分,信號也是如此的。

那接下來就要看甲和乙誰先到達0.7V的位置了,從上圖很明顯可以看到紅色線首先到達0.7V的位置,那就說明是乙先到的,所以答案不是A,也不是C,而是B,意不意外?

那接下來咱們就分析下為什么答案選B,首先在PCB上的銅箔走線是有寬度的,我們知道信號有個特性,就是會自動尋找最近的路徑,比如兩點信號總會尋找到最近的回流路徑。可以把甲乙兩根線看成一個跑道,而電子就是一個個的運動員,如果信號的頻率很低,這些電子就可以邁著整齊的步伐跑步了,就像咱們上學時候的早上出操,可以保持隊形。

但進入高頻以后就不一樣了,就像咱們1000米跑步,大家都知道內側的距離最短,都會爭搶著去跑道的內側,這個時候就無法保持原來整齊的隊形了。

電子也是一樣的,它就像賽車手一樣,很聰明的自動尋找內側的最短路徑,如下圖中綠色的路徑,這樣就造成了實際的路徑長度要遠遠小于100mil, 彎曲的部分越多,實際的路徑就越短。

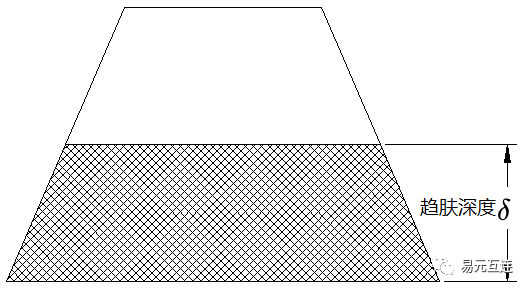

但這個問題還沒有結束,我們知道PCB上銅箔不僅有寬度,還有厚度,由于蝕刻的原因,銅箔的橫截面形成上窄下寬的梯形結構。由于高頻中存在趨膚效應,所有的電子都是走在趨膚深度范圍內的,如下圖所示。陰影部分是電子通過的空間,上部白色部分,實際上是沒有作用的,這也就是高頻板的銅箔為什么都是很薄的,因為厚了也沒什么效果,反而會浪費錢,就像路修的再寬,也沒有車子通過一樣的道理。

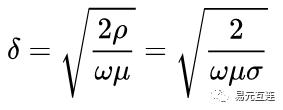

這是趨膚深度的計算公式,可以看到趨膚深度和頻率是反比關系。

頻率越高,趨膚深度就越小,電子回流路徑就越貼近PCB板。

了解了趨膚深度和頻率的關系,我們再回頭看圖6,趨膚深度越小,就意味著銅箔的寬度越寬,因為梯形結構,越往下寬度越大。

線路越寬,也就代表著走內側的路徑就會更短,這個應該可以想象出來的,如果乙的線寬0.1mm,走內的距離是98mil,那如果線寬是0.12mm,那走內側的距離可能就是96mil。

所以,最終得出的結論是:頻率越高,線路彎曲造成的實際傳輸距離差異就越大。

繞線做等長,反而沒有好處,既然繞線等長沒有效果,那如何保證信號同步呢?那這個答案是只有通過仿真。

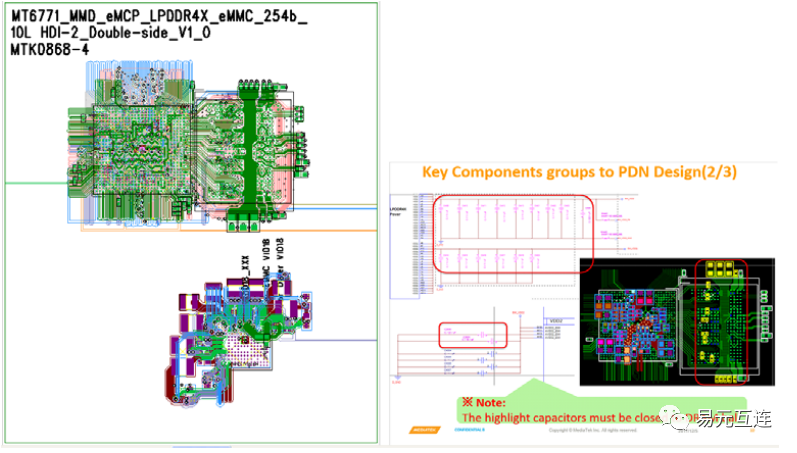

但很多公司都沒有仿真工程師的職位,而且仿真要占據很多的時間。這個時候芯片廠家的 Turn key 服務就很到位,會提供仿真好的CPU和DDR的線路給ODM和品牌商,如下圖是MTK公司提供的MT6771的PCB圖,而且不同的層數和階數也會有不同的PCB圖提供。

MT6771的DDR和CPU走線 有了廠家提供的走線,設計公司只要直接copy過來使用就可以了,包括CPU和DDR的相對位置都要一模一樣,所有的DDR線不能做任何更改,包括刪掉一個GND孔。

這也就是手機設計中EDA工程師不需要自己走DDR線的原因,當然廠家提供的DDR走線肯定也沒有做等長繞線的。

審核編輯:劉清

-

pcb

+關注

關注

4368文章

23492瀏覽量

409800 -

PCB板

+關注

關注

27文章

1474瀏覽量

53488 -

DDR

+關注

關注

11文章

732瀏覽量

66840 -

PoP

+關注

關注

0文章

33瀏覽量

16027 -

LPDDR5

+關注

關注

2文章

90瀏覽量

12591

原文標題:趨膚效應對DDR走線繞等長的影響

文章出處:【微信號:Hardware_10W,微信公眾號:硬件十萬個為什么】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IC datasheet為什么越來越薄了?

PCB設計中DDR布線要求及繞等長要求

極光64b66b中S_AXI_TREADY越來越低

MCU和MPU之間的區別變得越來越模糊

LED展望:光效越來越高 價格越來越低

通信行業的薪資水平為什么越來越低了

為什么DDR繞線等長的要求卻越來越低了?

為什么DDR繞線等長的要求卻越來越低了?

評論