消費(fèi)者對(duì)更快、更智能、更好產(chǎn)品的需求正在將創(chuàng)新推向前所未有的水平。因此,系統(tǒng)設(shè)計(jì)人員面臨著一個(gè)共同的困境:在已知平臺(tái)上設(shè)計(jì)新產(chǎn)品,只進(jìn)行增量更改;或者使用具有最先進(jìn)產(chǎn)品和功能的全新平臺(tái)。前者可能快速且風(fēng)險(xiǎn)低,但回報(bào)較低;而后者提供更好的多功能性、功能和價(jià)值,但風(fēng)險(xiǎn)更高。

現(xiàn)在,一套新的仿真工具支持在軟件中快速原型設(shè)計(jì),最大限度地降低開(kāi)發(fā)風(fēng)險(xiǎn),并使設(shè)計(jì)人員相信他們的新產(chǎn)品將按預(yù)期工作。該軟件提供了對(duì)模數(shù)轉(zhuǎn)換器、時(shí)鐘IC和放大器等單個(gè)產(chǎn)品功能的洞察,并且可以組合器件(例如ADC和時(shí)鐘),而無(wú)需獲取實(shí)際組件。購(gòu)買硬件的決定可以在軟件評(píng)估完成后做出,從而節(jié)省時(shí)間和金錢。

本文演示了ADIsimADC的多功能性,? ADIsimCLK,?以及 VisualAnalog 軟件套件,用于預(yù)測(cè) ADC 與采樣時(shí)鐘結(jié)合使用時(shí)的性能。本示例使用16位、250 MSPS模數(shù)轉(zhuǎn)換器AD9467和低抖動(dòng)時(shí)鐘發(fā)生器AD9523-1。第一部分介紹軟件評(píng)估,仿真ADC隨頻率變化的性能,并展示如何在軟件中連接器件。第二部分詳細(xì)介紹了使用評(píng)估板和SPIController軟件進(jìn)行的實(shí)際硬件設(shè)置。本例為AD9467的時(shí)鐘頻率為245.76 MSPS。AD9523-1評(píng)估板使用交互式GUI配置時(shí)鐘輸出。

使用 ADIsimADC 和 ADIsimCLK 進(jìn)行協(xié)同仿真

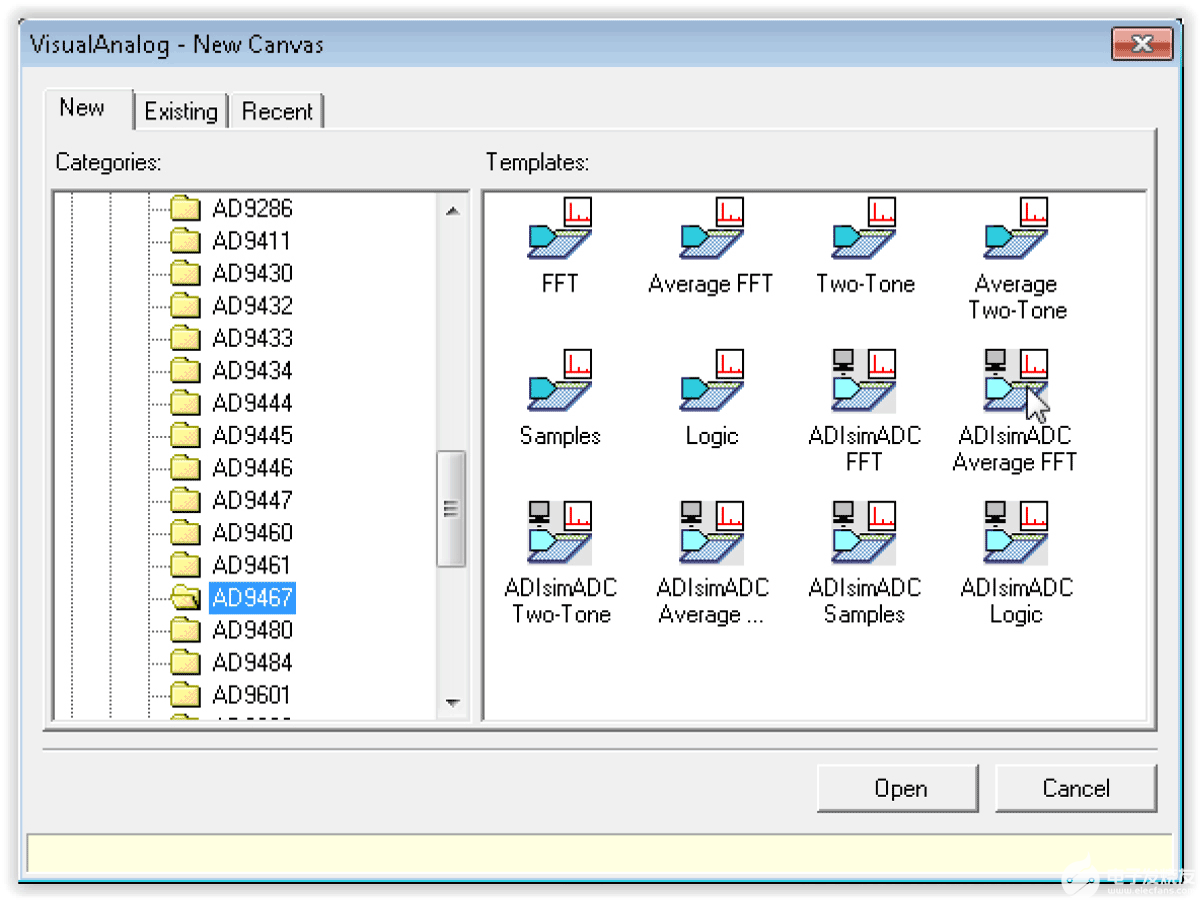

首先,下載并安裝VisualAnalog和AD9523-1評(píng)估軟件。ADIsimADC與VisualAnalog一起封裝。啟動(dòng) VisualAnalog 后,彈出窗口將要求用戶選擇一個(gè) Canvas,如圖 1 所示。

圖1.視覺(jué)模擬新畫布窗口。

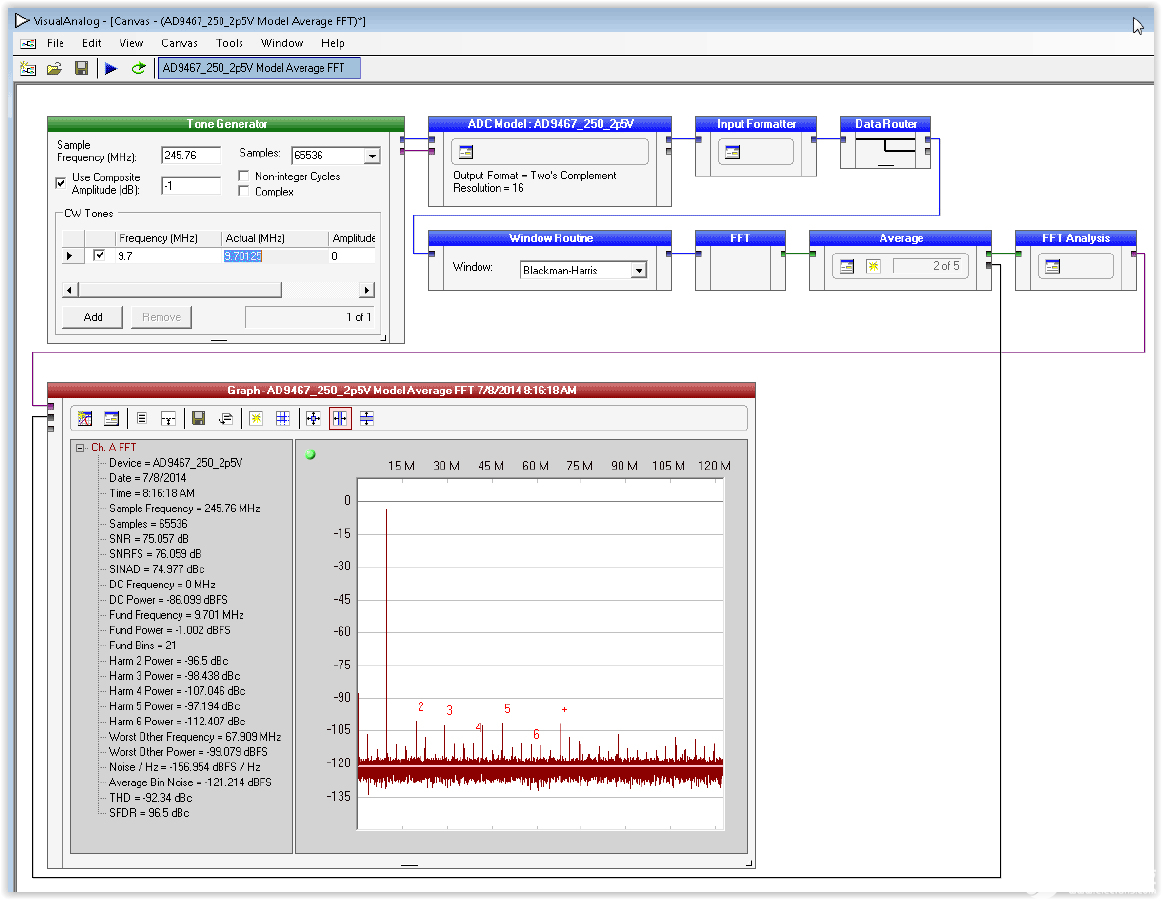

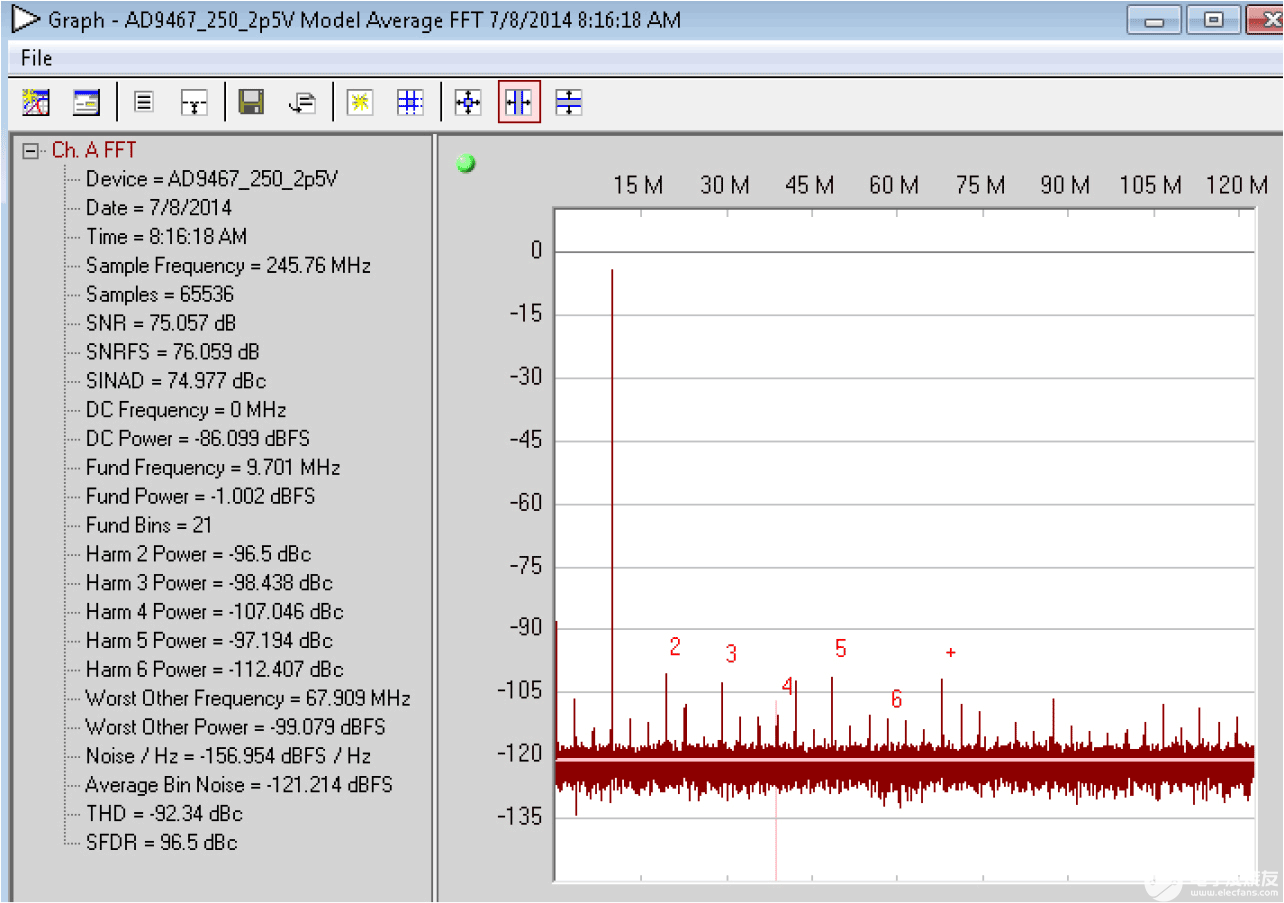

AD9467的ADIsimADC型號(hào)可在ADC→單通道→AD9467菜單選項(xiàng)下找到。圖2顯示了ADIsimADC平均FFT曲線。

圖2.ADIsimADC畫布顯示采用9.7 MHz單音FFT的AD9467。

設(shè)置ADIsimADC以預(yù)測(cè)ADC行為

在音調(diào)發(fā)生器模塊中輸入一個(gè)頻率,然后按 Tab。 ADIsimADC 根據(jù)采樣速率和樣本大小自動(dòng)將此頻率轉(zhuǎn)換為相干頻率。圖3顯示了默認(rèn)設(shè)置下9.7 MHz單音輸入的FFT。

圖3.ADIsimADC單音FFT,頻率為9.7 MHz。

設(shè)置ADIsimCLK以預(yù)測(cè)AD9523-1行為

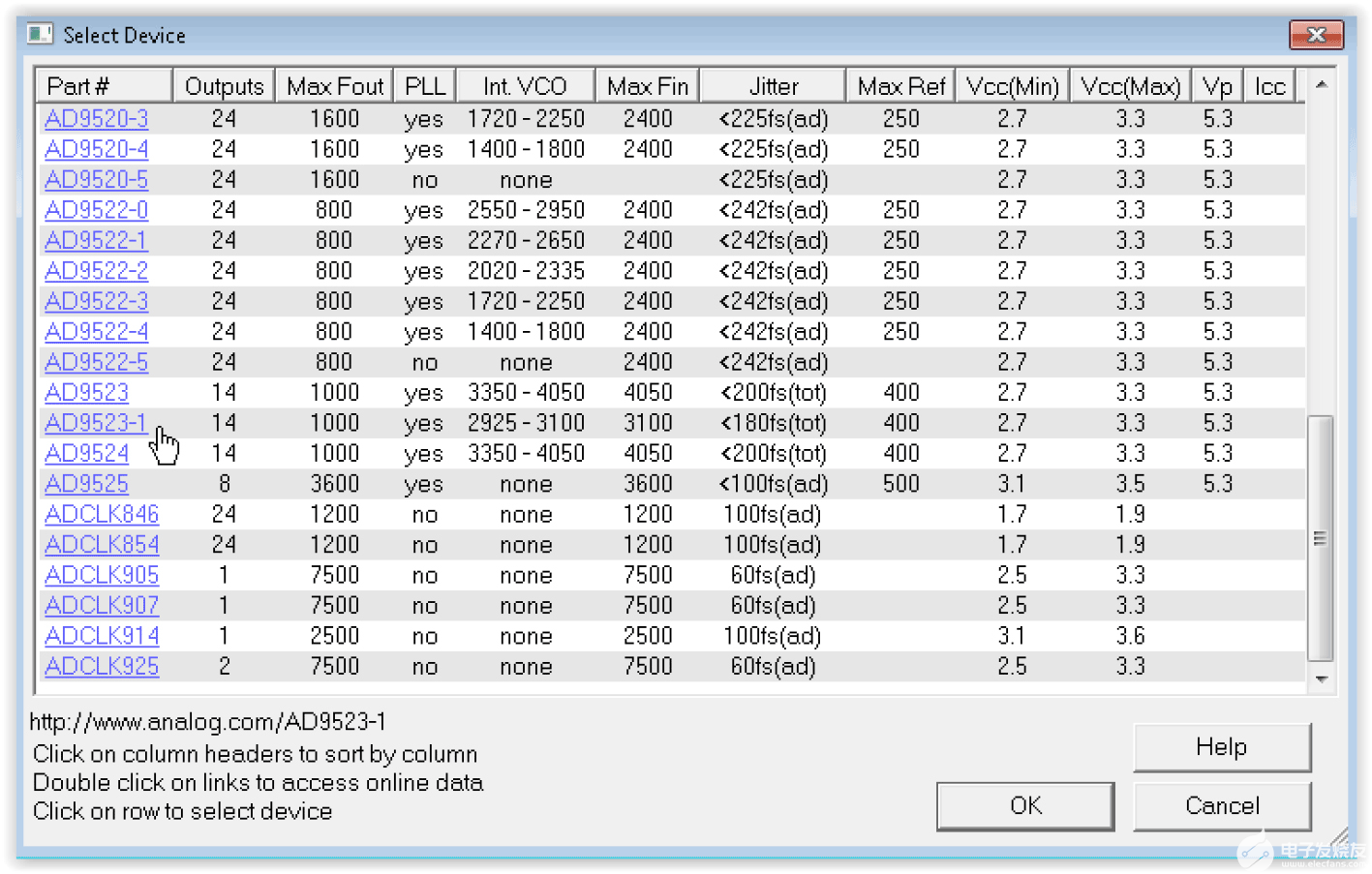

接下來(lái),下載并安裝ADIsimCLK軟件。安裝后,打開(kāi)程序并選擇文件→新建。將出現(xiàn)一個(gè)窗口,其中包含一系列設(shè)備,如圖 4 所示。

圖4.ADIsimCLK器件選擇。

遵循與實(shí)際預(yù)期系統(tǒng)實(shí)現(xiàn)最相似的設(shè)置方法。在本例中,外部 30.72MHz 時(shí)鐘提供對(duì)第一個(gè) PLL 的參考。Crystek CVHD-950用作雙回路PLL第一個(gè)環(huán)路的VCXO。內(nèi)部VCO頻率設(shè)置為2949.12 MHz,內(nèi)部除以3。OUT7 上的 4 分頻提供 245.76MHz 時(shí)鐘。此設(shè)置如圖 5 所示。

圖5.ADIsimCLK中的AD9523-1設(shè)置。

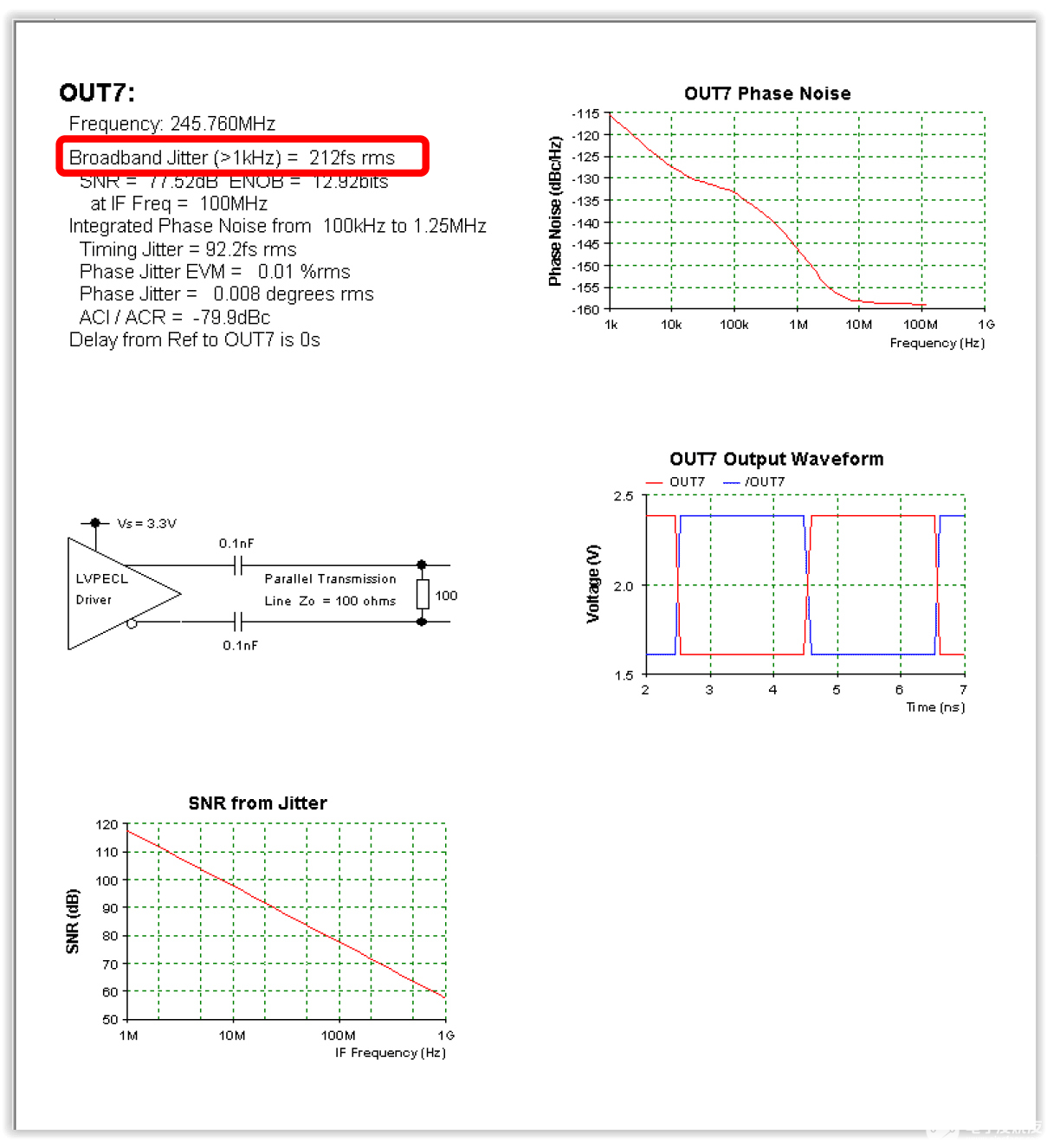

ADIsimCLK還可生成時(shí)鐘輸出報(bào)告,包括各種積分范圍內(nèi)的輸出相位噪聲和抖動(dòng)。這些報(bào)告在與各種輸出相對(duì)應(yīng)的選項(xiàng)卡上可用。在此設(shè)置中,OUT7用于為AD9467評(píng)估板提供時(shí)鐘。報(bào)告頁(yè)如圖 6 所示。突出顯示了關(guān)鍵規(guī)格寬帶抖動(dòng)。

圖6.ADIsimCLK 中的 OUT7 報(bào)告。

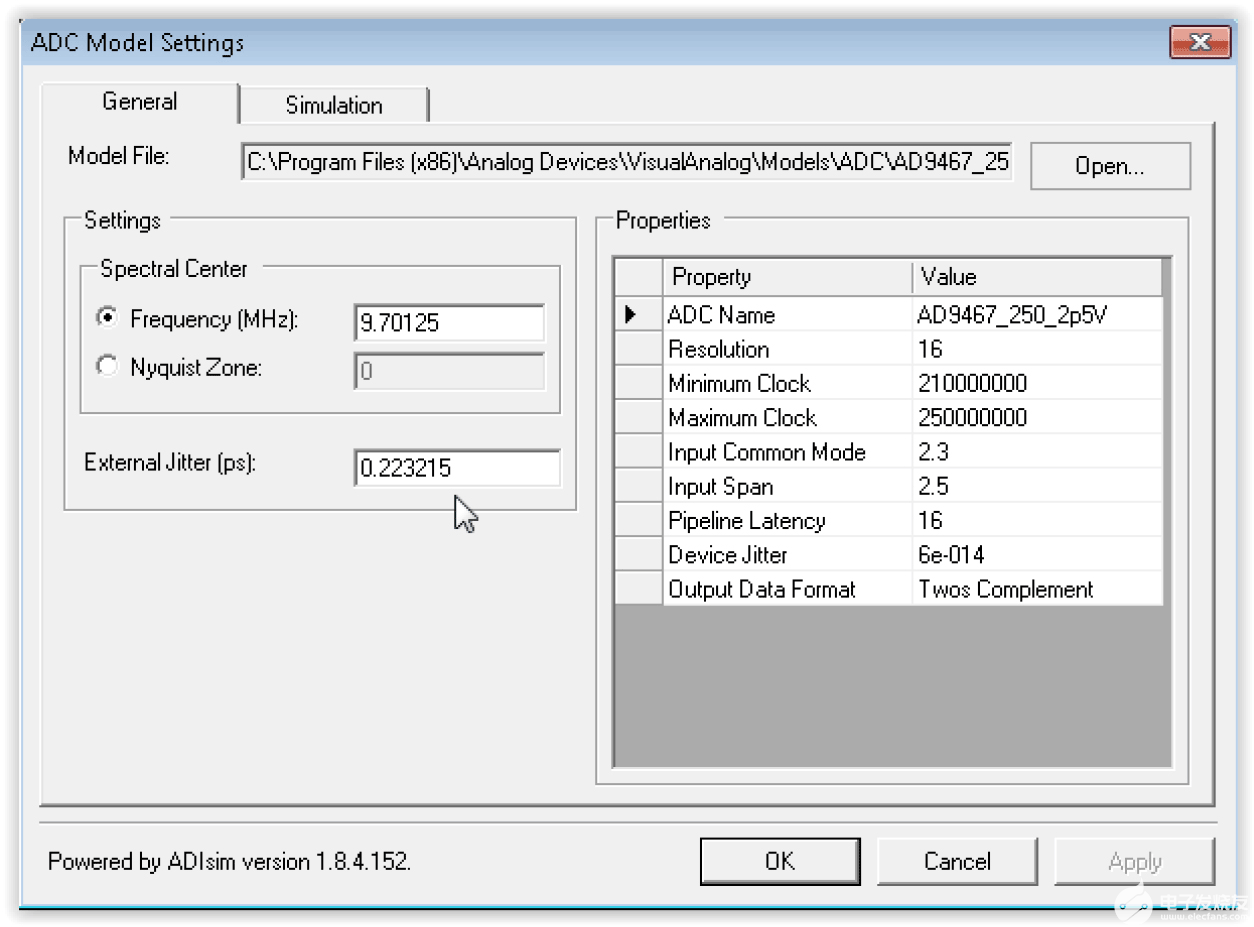

使用AD9523-1仿真AD9467

ADIsimADC可以預(yù)測(cè)AD9467與AD9523-1時(shí)鐘配合時(shí)的性能。ADIsimCLK報(bào)告中的寬帶抖動(dòng)規(guī)格可以傳遞到ADIsimADC畫布。在FFT畫布中,ADC模型模塊使用戶能夠更新總抖動(dòng)規(guī)格,如圖7所示。

圖7.更新ADIsimADC模型中的抖動(dòng)。

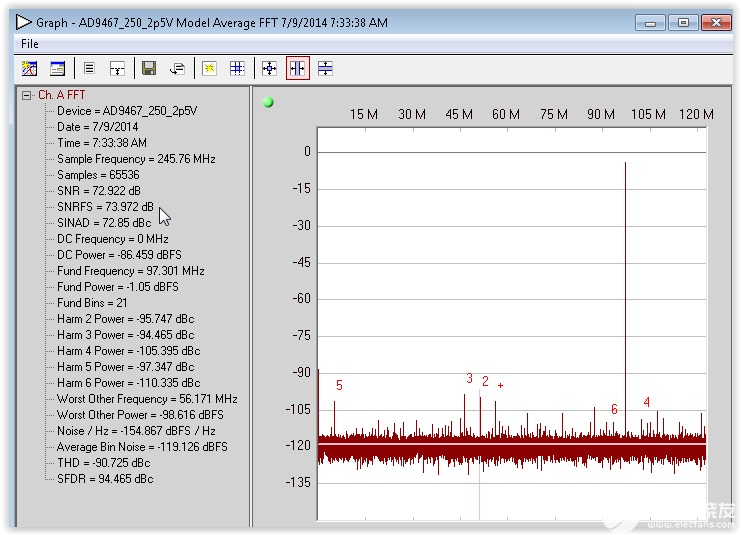

總抖動(dòng)可以計(jì)算為各個(gè)抖動(dòng)分量的和方根 (rss)。在這種情況下,孔徑抖動(dòng)為60 fs,寬帶抖動(dòng)為215 fs。傳遞給ADIsimADC的rss抖動(dòng)為223.2 fs,產(chǎn)生圖8所示的97 MHz單音FFT。利用更新的抖動(dòng),ADIsimADC可以預(yù)測(cè)任何輸入頻率下的預(yù)期性能。

圖8.97 MHz輸入時(shí)的單音FFT,具有ADIsimADC中更新的抖動(dòng)特性。

關(guān)于抖動(dòng)的簡(jiǎn)短說(shuō)明

ADC必須定期對(duì)模擬信號(hào)進(jìn)行采樣。需要一個(gè)穩(wěn)定的采樣時(shí)鐘,因?yàn)槿魏畏抢硐氲臅r(shí)鐘源都會(huì)產(chǎn)生一些相位噪聲。抖動(dòng)是采樣時(shí)鐘載波兩個(gè)指定頻率偏移之間的相位噪聲在時(shí)間段內(nèi)的積分。對(duì)于ADC,寬帶噪聲通常被認(rèn)為是最重要的。ADIsimCLK計(jì)算寬帶抖動(dòng),對(duì)高于1 kHz偏移的相位噪聲進(jìn)行積分。該寬帶抖動(dòng)被傳遞到ADIsimADC模型,以了解抖動(dòng)對(duì)ADC性能的影響。有關(guān)采樣時(shí)鐘抖動(dòng)如何影響ADC性能的更多信息,請(qǐng)參閱AN-756應(yīng)用筆記:采樣系統(tǒng)以及時(shí)鐘相位噪聲和抖動(dòng)的影響。

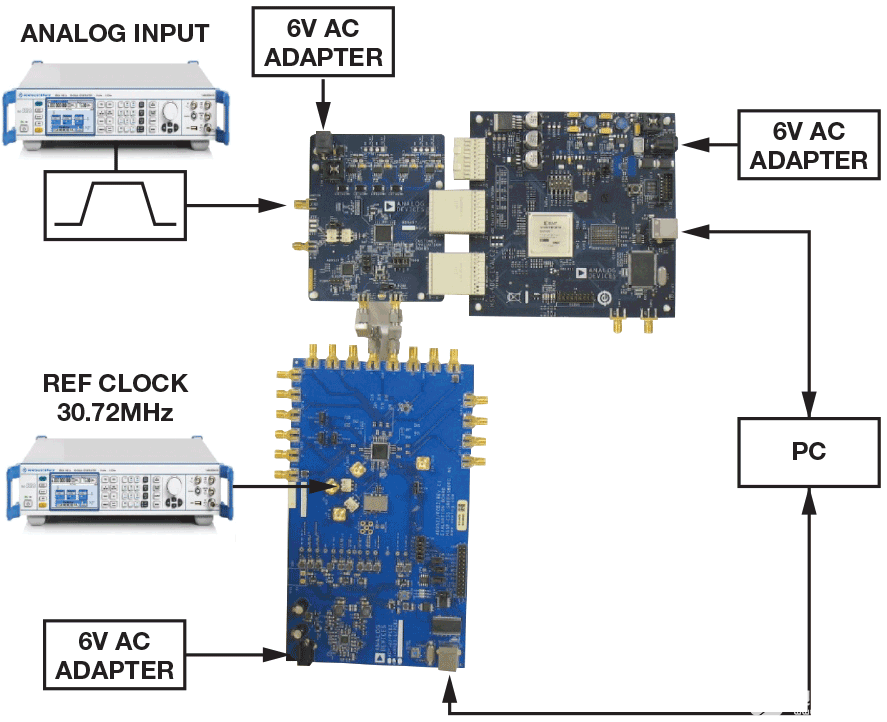

測(cè)量的性能

ADIsimADC預(yù)測(cè)使用AD9467評(píng)估板和AD9523-1評(píng)估板進(jìn)行測(cè)試。AD9523-1配置為在OUT7上產(chǎn)生245.76 MHz LVPECL時(shí)鐘。該輸出耦合到AD9467評(píng)估板,該評(píng)估板經(jīng)過(guò)修改,可接受J200和J201上的差分時(shí)鐘輸入。此設(shè)置如圖 9 所示。

圖9.顯示AD9523-1和AD9467評(píng)估板的硬件設(shè)置。

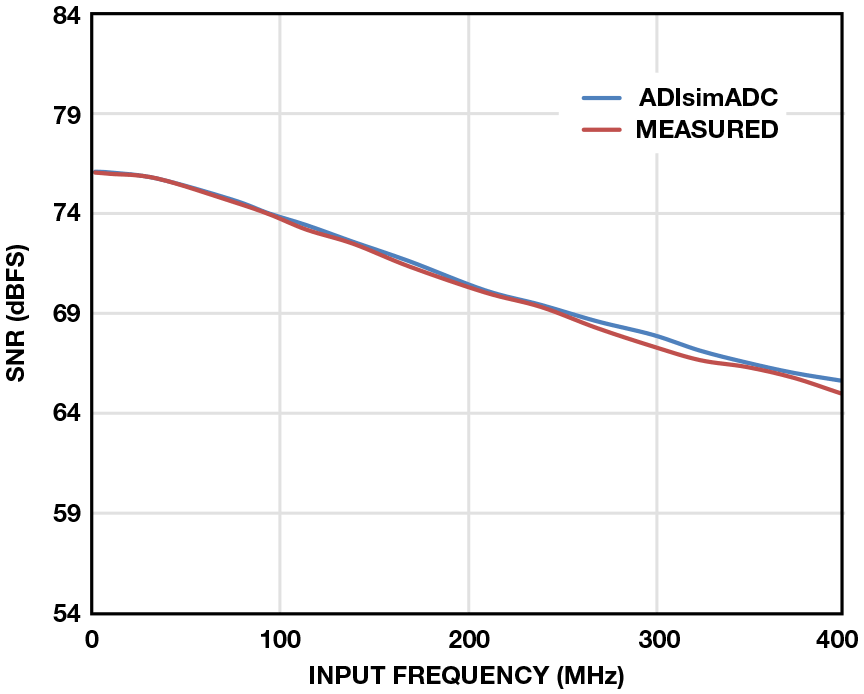

該設(shè)置使用2 MHz至400 MHz的模擬輸入頻率收集數(shù)據(jù)。 使用VisualAnalog捕獲單音FFT,并根據(jù)ADIsimADC預(yù)測(cè)編譯和繪制數(shù)據(jù)。圖10顯示了SNR與頻率的關(guān)系。請(qǐng)注意模擬與實(shí)際測(cè)量值的匹配程度。

圖 10.SNR與模擬輸入頻率的比較ADIsimADC和實(shí)際測(cè)量數(shù)據(jù)

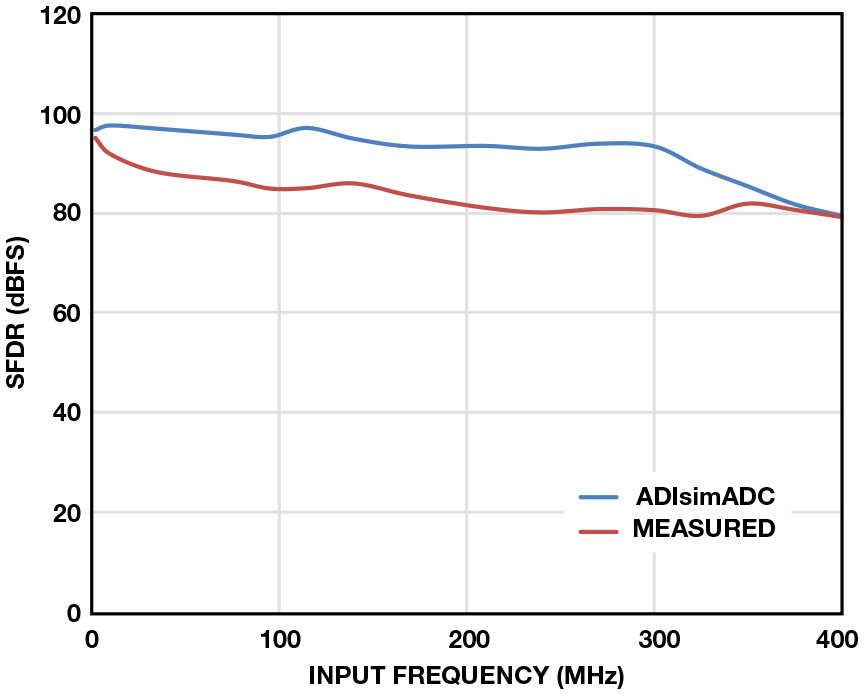

圖 11 顯示了 SFDR 數(shù)據(jù)。這些數(shù)字并不完全一致,但不同頻率的模擬數(shù)據(jù)和測(cè)量數(shù)據(jù)之間的總體趨勢(shì)非常吻合。SFDR高度依賴于PC板布局,組件,時(shí)鐘幅度,這可以解釋差異。

圖 11.SFDR與模擬輸入頻率的比較ADIsimADC和實(shí)際測(cè)量數(shù)據(jù)

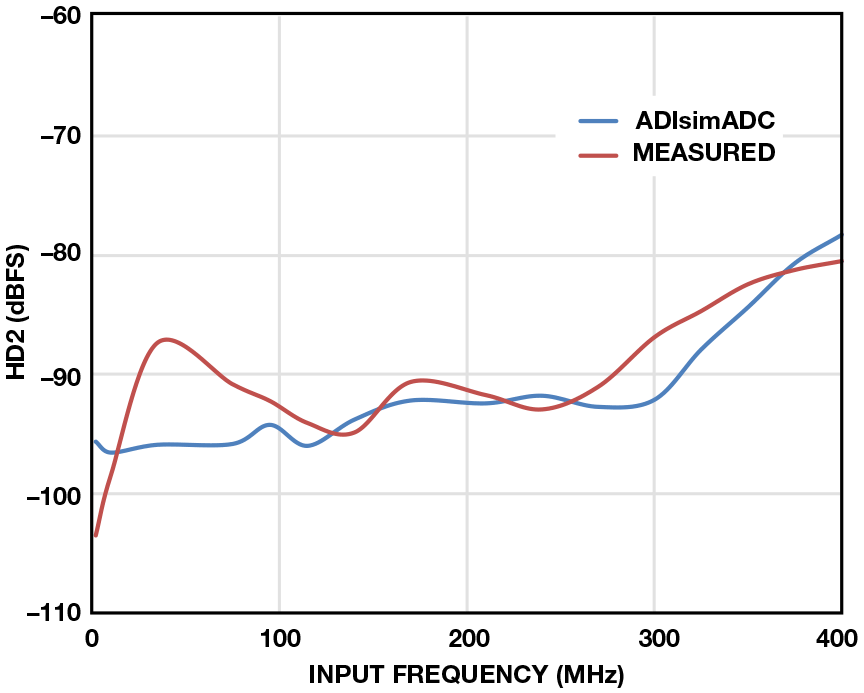

更好的失真測(cè)量方法是比較二次和三次諧波失真的仿真和測(cè)量數(shù)據(jù),如圖12和圖13所示。仿真和測(cè)量的HD2性能非常匹配,證明進(jìn)入評(píng)估板ADC的差分信號(hào)在幅度和相位方面非常平衡,并且評(píng)估板的布局足夠好,不會(huì)顯著影響差分信號(hào)平衡。

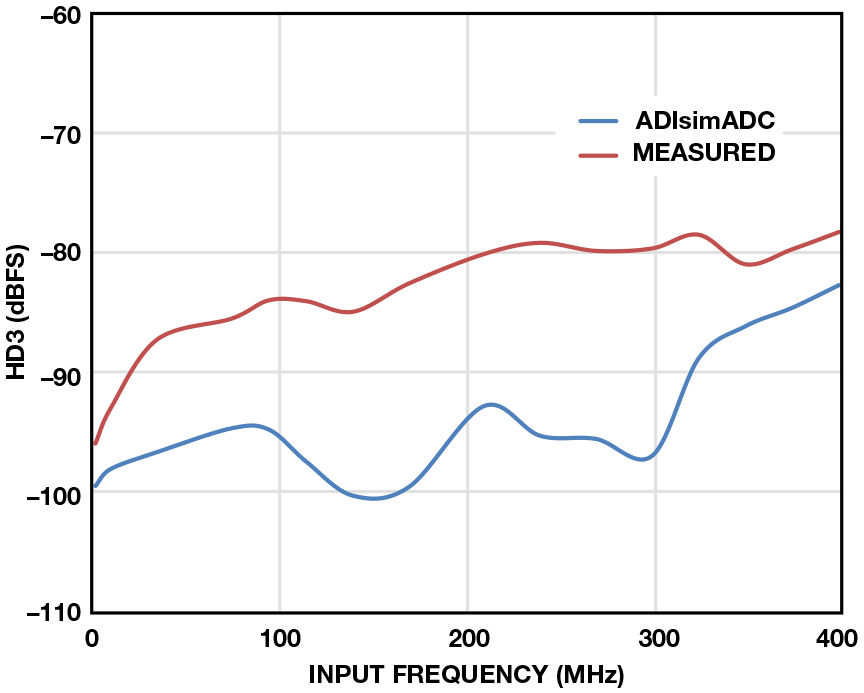

另一方面,預(yù)測(cè) HD3 性能隨頻率變化可能很棘手。ADIsimADC模型是通過(guò)查看特性化過(guò)程中的ADC性能和DNL數(shù)據(jù)而開(kāi)發(fā)的。該算法使用插值和外推技術(shù)來(lái)預(yù)測(cè)特定頻率下的動(dòng)態(tài)范圍,但無(wú)法準(zhǔn)確預(yù)測(cè)HD3在所有點(diǎn)的性能。

圖 12.HD2與模擬輸入頻率的比較,比較ADIsimADC和實(shí)際測(cè)量數(shù)據(jù)。

圖 13.HD3與模擬輸入頻率的比較,比較ADIsimADC和實(shí)際測(cè)量數(shù)據(jù)。

HD3的實(shí)際性能在很大程度上取決于實(shí)際因素,如電源電壓、元件選擇、ADC輸入緩沖器和時(shí)鐘信號(hào)質(zhì)量。

HD3 預(yù)測(cè)可能并不總是正確的,但頻率的總體趨勢(shì)在模擬數(shù)據(jù)和測(cè)量數(shù)據(jù)之間提供了良好的一致性。

在許多系統(tǒng)設(shè)計(jì)中,主要的性能指標(biāo)是SNR。SFDR和動(dòng)態(tài)范圍取決于許多其他因素。仿真和測(cè)量數(shù)據(jù)之間的SNR值匹配得非常好,這使系統(tǒng)設(shè)計(jì)人員對(duì)ADC和時(shí)鐘的選擇充滿信心。

結(jié)論

對(duì)更短設(shè)計(jì)周期的需求給系統(tǒng)設(shè)計(jì)人員帶來(lái)了巨大的壓力,要求他們?cè)u(píng)估新產(chǎn)品的設(shè)計(jì)。硬件評(píng)估幾乎總是必要的,但選擇錯(cuò)誤的硬件組合最終可能會(huì)花費(fèi)金錢和時(shí)間。軟件評(píng)估可以作為對(duì)ADC產(chǎn)品的快速簡(jiǎn)便的初步了解。ADIsimADC和ADIsimCLK為系統(tǒng)設(shè)計(jì)人員選擇ADC和時(shí)鐘IC提供了一種簡(jiǎn)單有效的方法。這些軟件工具允許系統(tǒng)設(shè)計(jì)人員混合搭配各種ADC和時(shí)鐘IC,從而對(duì)所選組件產(chǎn)生足夠的信心,以執(zhí)行硬件評(píng)估。

審核編輯:郭婷

-

放大器

+關(guān)注

關(guān)注

145文章

14117瀏覽量

216482 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8975瀏覽量

150986 -

adc

+關(guān)注

關(guān)注

99文章

6653瀏覽量

548473

發(fā)布評(píng)論請(qǐng)先 登錄

lavbiew 加快讀取txt的速度

怎么設(shè)計(jì)射頻器件建模工具?

ADC 建模工具加快評(píng)估過(guò)程

如何對(duì)系統(tǒng)進(jìn)行最佳建模

請(qǐng)問(wèn)放大器參數(shù)評(píng)估工具是如何工作的?

并聯(lián)穩(wěn)壓器可加快電源供應(yīng)啟動(dòng)速度

學(xué)生發(fā)明可加快傷口愈合設(shè)備

安森美行業(yè)首創(chuàng)的云聯(lián)接平臺(tái)Strata Developer Studio簡(jiǎn)化并加快您的研發(fā)、評(píng)估和設(shè)計(jì)

用于評(píng)估ADC的產(chǎn)品及其評(píng)估板的模型及工具軟件

五個(gè)免費(fèi)UML建模工具介紹

如何用ADIsimADC完成ADC建模

C2000 MCU的ADC輸入電路評(píng)估(使用TINA-TI仿真工具)

ADC建模工具可加快評(píng)估速度

ADC建模工具可加快評(píng)估速度

評(píng)論