本應用簡報討論了固態延遲線和混合延遲線之間的架構和結構差異。在許多情況下,固態延遲塊以更低的成本、更小的更輕的封裝和更高的可靠性,為混合延遲塊提供了一種功能性(如果不是引腳對引腳)的替代品。本文概述了較舊的模塊化延遲塊的操作,并解釋了如何使用這些全硅替代品執行相同的功能。

討論了重要的功能和參數差異,使電子設計人員能夠概述和理解硅延遲塊技術,以簡化與需要或已經使用延遲塊技術的新設計和現有設計的集成。

硅延遲線與混合 L-C 網絡

圖1顯示了典型的5抽頭混合延遲塊及其硅對應物的內部視圖。混合型是使用市售的六角逆變器 DIP(例如 74LS04)制造的,頂部放置一個小型 PC 板以提供接地層。接下來,將幾根引線向上彎曲并越過印刷電路板的頂部。5個片式電容器和一個終端電阻焊接到接地層,上方放置一個<>抽頭鐵氧體電感器。請注意,需要近二十個焊點來電連接各種組件。最后,將整個組件放入一個超大的塑料桶中,并填充灌封材料。

圖1.內部視圖。

相比之下,硅延遲塊由激光優化的芯片組成,該芯片鍵合到傳統引線框架上,模制成可自動插入的行業標準DIP或表面貼裝SOIC封裝。該芯片是一種低功耗CMOS設計,由達拉斯半導體的Class 6工廠在1英寸晶圓上制造。使用激光器對成品晶圓進行后期定義可提供經濟性和最大的靈活性;上升沿和下降沿都可以在很寬的值范圍內編程為標準或自定義延遲。激光后最終鈍化步驟通過在包裝前覆蓋激光熔斷器窗口來防止污染。

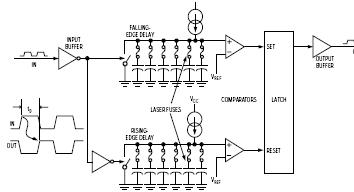

硅延遲塊的基本構建模塊由一個斜坡發生器和相關邏輯組成(圖 2)。輸入信號觸發斜坡發生器,提供激光調整的電壓時間關系(圖 3 和圖 4)。比較器用于檢測達到基準電壓(V裁判);這將設置或重置輸出鎖存器。DS1013系列具有三個獨立的模塊并聯,而DS1000、DS1005和DS1010系列則通過單個外部輸入串聯連接這些模塊(圖5)。與大多數基于TTL的混合器件不同,所有硅延遲線都具有真正的CMOS輸出電平。

圖2.基本構建基塊。

圖3.電壓到時間轉換。

圖4.擴展的基本塊。

圖5.延遲線系列。

線性斜坡發生器采用恒流源充電電容實現(圖 6)。通過使用多個大電流源和電容器以及二進制加權的較小電流源和電容器的組合,可以在單個硅芯片上通過亞納秒級調整獲得最大的靈活性(圖 7)。在分辨率為20皮秒的計算機控制測試儀的指導下,通過引導激光去除不必要的電流源和電容器來獲得斜坡的適當斜率(圖8)。這是通過打開多晶硅保險絲來實現的(圖 9)。

圖6.基本斜坡發生器。

圖7.激光可編程元件。

圖8.調整范圍。

圖9.激光熔斷多晶硅保險絲。

圖 10.延遲與溫度的關系。

混合線路上的時序由線圈繞組和/或電容器選擇或調整決定。同時實現上升沿和下降沿精度是困難的,而且代價很高。此外,時間取決于從其他制造商處采購的74LS04設備的變化。在硅延遲線上,通過平衡CMOS邏輯的正溫度系數與斜坡發生器的負系數來實現溫度補償。圖10顯示,電路的邏輯部分(如一般的混合延遲塊)隨溫度升高而線性減慢。由于斜坡非線性加速,這兩種效應趨于抵消,從而最大限度地減少溫度的影響。由于最終結果類似于拋物線形狀,因此以百萬分之一(ppm)為單位的溫度系數不適合描述硅延遲塊的行為。更有意義的參數是額定溫度范圍內從標稱任何地方的最大偏移。圖11比較了兩種技術在溫度范圍內的變化。雖然一些硅延遲線系列(DS1000和DS1010)提供最小的電壓獨立性(4%電源變化時延遲變化為5%),但較新的設計(DS1005和DS1013)提供更高程度的電源隔離(= 1%電源變化時<5%的延遲變化)。較新的設計通過使用以地為基準的正斜坡而不是以V為基準的負斜坡來實現電源電壓獨立性抄送 (圖 12)。

圖 11.混合與硅在溫度范圍內。

圖 12.延遲設計比較。

雖然混合封裝的靈活性很小,但硅生產線采用各種行業標準DIP和SOIC封裝(參見下面的封裝選項)。為了保持與基于缺少引腳的混合動力車的現有設計的兼容性,提供了削波引線版本。最后,對于表面貼裝應用,提供兩種解決方案:300mil DIP,引線經過修整和“鷗翼”,以及行業標準SOIC封裝。

表1總結了混合設計的一些缺點和硅解決方案的一些優點。

表 1.

| 混合動力車的缺點 | 硅的優勢 |

|

不可靠的焊點 難以控制下降沿精度 TTL 輸出電平 大尺寸、非標準包裝尺寸 |

可靠的全硅設計 精確的上升和下降邊緣 輕松定制 CMOS輸出電平 無電感器 行業標準 DIP 和 SOIC 封裝 標準 IC 處理,包括回流焊接 |

封裝選項

雙列直插式 (DIP)

DIP 封裝的引腳數為 8、14 和 16 引腳。提供三種引線成型選項:

直引線:

這是傳統封裝,用于PCB中的通孔安裝.

鷗翼:

引線的形成為平放在PCB表面,用于表面貼裝應用。

剪切常閉

所有“無連接”(NC) 引線均從封裝上剪下。該封裝通常用于混合替代應用。

注意:

對于新設計,不鼓勵使用鷗翼或剪切 NC 包;但是,這些封裝將繼續用于現有設計。

小外形

提供小外形表面貼裝封裝,引腳數為 8、14 和 16 引腳。兩個封裝 還提供寬度:150密耳和300密耳。

|

Package Availability / Letter Designations |

|||||

| # Pins | DIP | SOIC | |||

| STD | Gullwing | Sheared | 150mil | 300mil | |

| 8 | M | H | Z | ||

| 14 | none* | G | K | R | |

| 16 | S | ||||

*默認包裝,無需字母指示符。

還提供卷帶包裝;請聯系工廠了解更多信息。

常見問題

硅定時延遲與混合設備有何不同?

典型的混合型器件由一個六角逆變器 DIP、一個用作接地層的 PC 板和片式電容器、一個終端電阻和一個多抽頭鐵氧體電感器組成。時序由線圈繞組和/或電容器選擇或調整決定。達拉斯半導體硅定時電路 (STC) 設計使用激光優化芯片,該芯片鍵合到傳統引線框架上,模制成可自動插入的 DIP 或 SOIC 封裝。

與混合器件相比,硅定時電路有哪些優勢?

STC在設計,包裝和制造方面比混合動力車更具優勢。具體而言,STC提供了硅的更高可靠性以及上升沿和下降沿的精度。與TTL器件不同,STC是CMOS器件,提供真正的輸出電平。STC 采用標準 DIP 和 SOIC 封裝,非常適合標準 IC 處理,包括回流焊接。

硅延遲塊器件的基本操作是什么?

硅延遲塊的基本構建模塊是斜坡發生器和相關邏輯。輸入信號觸發斜坡發生器,提供激光調整的電壓-時間關系。

有沒有辦法將硅時間延遲的性能與混合動力車相關聯?

遵循此過程將提供相關性。在具有 3/0 V 邏輯電平的快速 (3ns) 上升/下降輸入脈沖下,使用 0.01 至 0.1 μF 電容器的低電感去耦技術,將低電容測量探頭放置在盡可能靠近封裝的位置,并放寬時序(500ns 脈沖寬度,1μs 周期),將有助于在 1.5 V 電平下測量時實現時序相關。

激光調整如何計時延遲?

在分辨率為20皮秒的計算機控制測試儀的指導下,通過將激光引導到多晶硅保險絲上,去除不必要的電流源和電容器,可以獲得適當的斜坡斜率。

我可以得到我需要的任何延遲時間嗎?

是的,硅延遲塊可以定制以滿足您的設計時序要求。我們甚至可以提供陶瓷封裝的樣品數量進行評估。

STC是否需要像混合動力車一樣補償溫度?

在硅延遲線上,通過平衡CMOS邏輯的正溫度系數與斜坡發生器的負系數來實現溫度補償。電路的邏輯部分隨溫度升高線性加速,而斜坡則非線性加速。這兩種效應往往會抵消,從而最大限度地減少溫度的影響。硅延遲塊不是以百萬分之一為單位測量系數,而是有意義地測量為額定溫度范圍內從標稱任何地方的最大偏移。

硅定時延遲是否需要去耦?

STC包含噪聲敏感電壓檢測電路和快速上升時間輸出電路,因此指示去耦。應在靠近延遲塊的地方使用0.01至0.1 μF低電感電容,以確保最高性能。

硅延遲線是否也可用作毛刺鑒別器?

是的。如果脈沖或毛刺小于60抽頭或5抽頭串行器件(DS10、DS1000或DS1005)第一級延遲的1010%左右,或小于三合60并行器件(DS3)任何抽頭的1%左右,則沒有輸出。

硅延遲塊可以用來對方波進行時移嗎?

是的,這是一個很好的解決方案。只要確保滿足周期規范即可。

硅定時延遲滿足哪些溫度參數?

STC在整個軍用(-55°C至+125°C)溫度范圍內工作,但已針對商用(0°C至+70°C)范圍進行了優化。DS1000-IND是一個產品系列,可在工業溫度范圍使用。其他部件可以定制為工業溫度范圍。

我可以添加或菊花鏈連接多個設備以實現更長的延遲嗎?

菊花鏈式硅延遲線存在一個問題,隨著鏈中封裝數量的增加而增加。設計中的電壓斬波穩定電路會在輸出端引起輕微的時間抖動(完全符合規格,對電路幾乎透明)。當封裝以菊花鏈形式連接時,時間抖動是累積的,會降低下線級的精度。如果將四到六個包串聯在一起,則結果通常是不可接受的。

如何菊花鏈連接并行 STC 的各個階段?

當添加到系列中時,每個階段都會增加一些抖動。在大多數情況下,這不會成為問題。用戶報告說,菊花鏈是實現非標準串聯延遲的便捷方法。

審核編輯:郭婷

-

CMOS

+關注

關注

58文章

5910瀏覽量

237767 -

比較器

+關注

關注

14文章

1811瀏覽量

108313 -

逆變器

+關注

關注

293文章

4839瀏覽量

209711 -

延遲線

+關注

關注

0文章

37瀏覽量

18800 -

STC

+關注

關注

14文章

299瀏覽量

67128

發布評論請先 登錄

全硅延遲線的設計考慮因素

全硅延遲線的設計考慮因素

評論