本應用筆記包含將非多路復用總線處理器連接至以下達拉斯半導體T1或E1成幀器和單芯片收發(fā)器(SCT)所需的信息:DS2141A、DS2143、DS2151或DS2153。這些器件最初設計用于與使用多路復用總線配置的處理器接口。通過一些額外的外部邏輯和對軟件的微小更改,任何非多路復用處理器都可以連接到這些設備。對設計人員來說,顯而易見的好處是處理器的范圍更廣,能夠與這些設備接口。應用筆記包含一張圖表,說明了如何將多路復用地址和數(shù)據(jù)總線連接到處理器獨立地址和數(shù)據(jù)總線。它包含必要的達拉斯半導體總線時序圖。最后,它提供了有關(guān)如何編寫軟件的信息,該軟件將允許總線接口讀取和寫入達拉斯半導體器件。目標是為設計人員提供使硬件和軟件與設備通信所需的所有信息。

DS2141A、DS2143、DS2151和DS2153包含一些內(nèi)部電路,使其能夠更容易地連接至具有非多路復用地址/數(shù)據(jù)總線的外部控制器。在DS2141A、DS2143、DS2151和DS2153等多路復用方案中,存在一個信號(通常稱為地址選通或地址鎖存使能),表示總線上存在有效地址。該信號是必需的,因為地址和數(shù)據(jù)線共享同一總線。在非多路復用方案中,控制器可能無法提供此信號,因為地址和數(shù)據(jù)線是分開的。DS2141A、DS2143、DS2151和DS2153包含一些板載電路,如果采用非多路復用總線,可在內(nèi)部創(chuàng)建地址鎖存器。

此內(nèi)部地址鎖存器的創(chuàng)建過程如下。在Intel時序設置中,當DS2141A、DS2143、DS2151和DS2153上的ALE引腳為高電平時,如果WR引腳變?yōu)榛顒与娖剑吹碗娖剑瑒t地址將鎖存于WR的上升沿。在摩托羅拉時序設置中,當AS引腳為高電平而R/W引腳為低電平時,如果DS引腳變?yōu)榛顒与娖剑锤唠娖剑瑒t地址將鎖存于DS的下降沿。

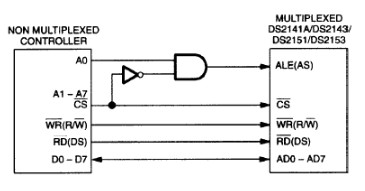

例如,在非多路復用系統(tǒng)中,A0可以連接到ALE(或AS)輸入。請參見圖 1。DS2141A、DS2143、DS2151和DS2153的每次讀取或?qū)懭攵及瑑蓚€操作。要寫入DS2141A、DS2143、DS2151和DS2153,控制器首先寫入地址,然后寫入數(shù)據(jù)。為了讀取DS2141A、DS2143、DS2151和DS2153,控制器首先寫入地址,然后讀取數(shù)據(jù)。控制器會將地址視為數(shù)據(jù)。地址將駐留在奇數(shù)字節(jié)中,而數(shù)據(jù)將駐留在偶數(shù)字節(jié)中。有關(guān)計時信息,請參見圖 2 至 4。DS2141A、DS2143、DS2151和DS2153數(shù)據(jù)資料中列出的參數(shù)也適用于非多路復用總線工作。

圖1.非頁面模式內(nèi)存接口。

圖2.非多路復用英特爾讀取計時。

圖3.非多路復用英特爾寫入計時。

圖4.非多路復用摩托羅拉計時。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19677瀏覽量

232666 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3549瀏覽量

107010 -

總線

+關(guān)注

關(guān)注

10文章

2935瀏覽量

89101

發(fā)布評論請先 登錄

相關(guān)推薦

DS2141A, DS2143, DS2151, DS215

DS2141A, DS2143, DS2151, DS215

DS2151, DS2153 Interfacing to

DS2151, DS2153 Interfacing to

DS2141A, DS2143, DS2151, DS215

DS2141A, DS2142, DS2151, DS215

DS2141A, DS2143, DS2151 and DS

DS2151, DS2153 Interfacing to

DS2141A, DS2143, DS2151, DS215

DS2141A , DS2143 , DS2151 , DS

DS2151, DS2153 Interfacing to

DS2141A, DS2143, DS2151, DS215

DS2141A, DS2143, DS2151 and DS

DS2151,DS2153連接的ADSP-2181-DS21

ds2141a,ds2143,ds2151,ds2153接口的西門子peb2045

DS2141A、DS2143、DS2151、DS2153與非多路復用總線接口

DS2141A、DS2143、DS2151、DS2153與非多路復用總線接口

評論