任何一個電子元件,不論是一個三極管還是一個集成電路(Integrated Circuit, IC),想要使用它,都需要把它連入電路里。一個三極管,只需要在源極、漏極、柵極引出三根線就可以了,然而對于擁有上百或上千個引腳的超大規模集成電路 (Very Large Scale Integration Circuit, VLSI)來說,靠這種類似于手動把連線插到面包板的過程是不可能的。直接把IC連接到 (未經封裝的集成電路本體,裸片,Die)電路中也是不可能實現的,因為裸片極容易收到外界的溫度、雜質和外力的影響,非常容易遭到破壞而失效。

所以電子封裝的主要目的就是提供芯片與其他電子元器件的互連以實現電信號的傳輸,同時提供保護,以便于將芯片安裝在電路系統中。

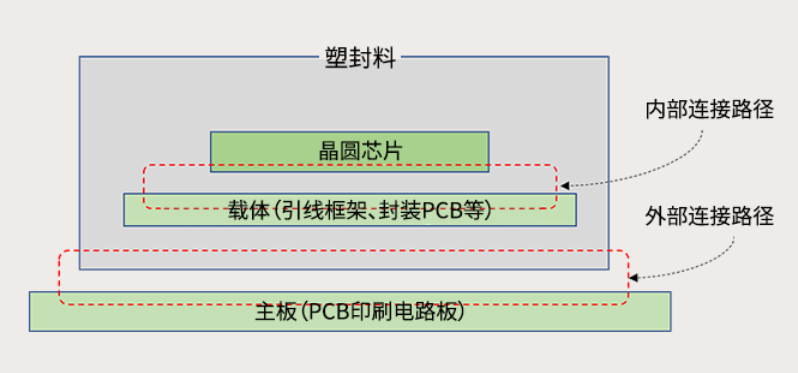

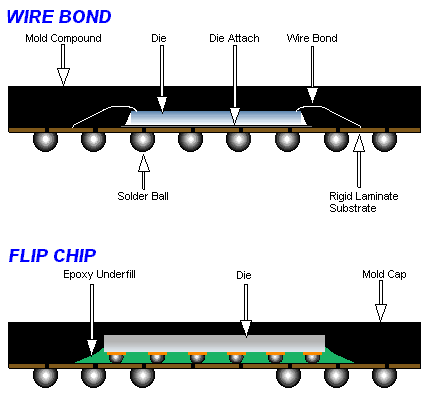

一般的半導體封裝都類似于下面的結構,將裸片安裝到某個基板上,裸片的引腳通過內部連接路徑與基板相連,通過塑封將內部封裝好后,基板再通過封裝提供的外部連接路徑與外部電路相連,實現內部芯片與外界的連接,就像上面兩個圖一樣,裸Die和封裝內部復雜的連接等都埋在里面,封裝好后就是對外就是一些規整的引腳了。

不論是多復雜的封裝,從黑盒的角度來看其實現的基本功能都是一樣的,最簡單的就是封裝一個分立器件,給出幾個引腳;復雜一點想要封裝具有多個I/O接口的IC,以及多個IC一起封裝,在封裝的發展過程中也發展出了很多封裝類型和很多技術,比如扇出技術、扇入技術這些。這些概念和縮寫非常多,尤其是當談到先進封裝(Advanced Packaging)的時候,為了實現高密度集成以及快速信號傳輸這些需求,不得不在每一個地方都發展一些新的技術,很多情況下會把它們都并入到先進封裝技術里來介紹,這有時候會引起一些困惑,這里主要整理一下IC封裝里的互連技術。在IC封裝種幾種典型的互連技術包括引線鍵合(Wire Bonding,WB)、載帶自動焊(Tape-automated Bonding,TAB)、倒裝芯片(Flip Chip,FC)、晶圓級封裝(Wafer-Level Packaging,WLP)、以及硅通孔(Through Silicon Via,TSV)。像模塊化設計一樣,同一種封裝類型中也可能采用不同的互連技術,比如常用在手機芯片里的BGA封裝有引線鍵合形式和倒裝形式,不同的互連技術也可能同時出現在一個復雜封裝中。

封裝互連技術

引線鍵合

引線鍵合是最經典使用最廣泛的互連技術,使用金屬線,利用熱、壓力、超聲波能量將金屬引線與基板焊盤緊密焊合,從而實現芯片與基板間的電氣互連和芯片間的信息互通。

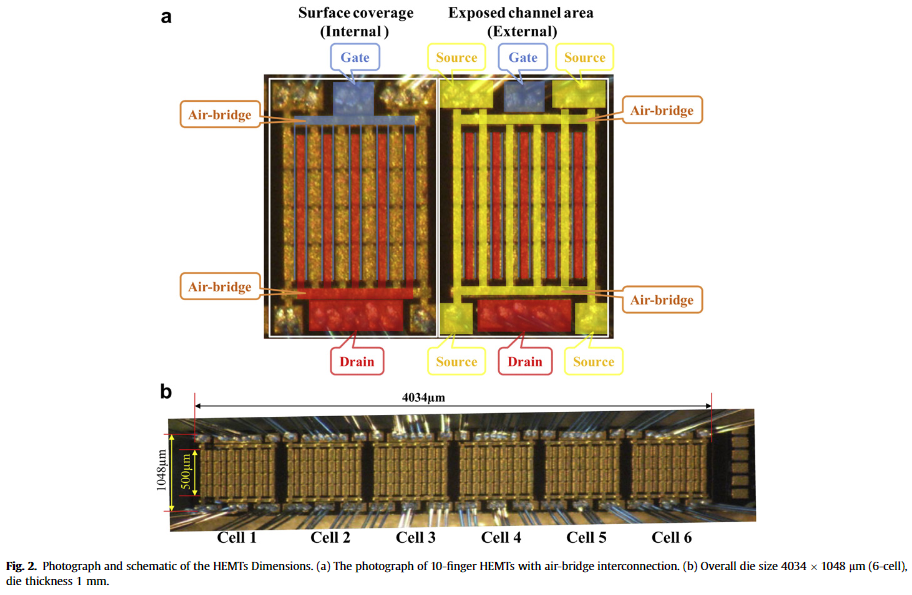

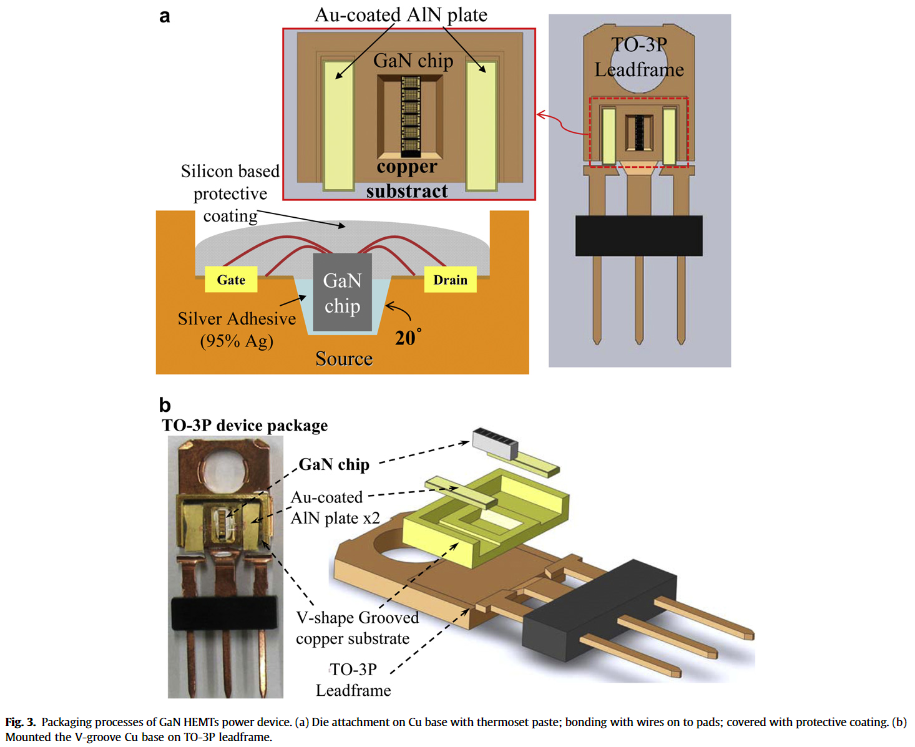

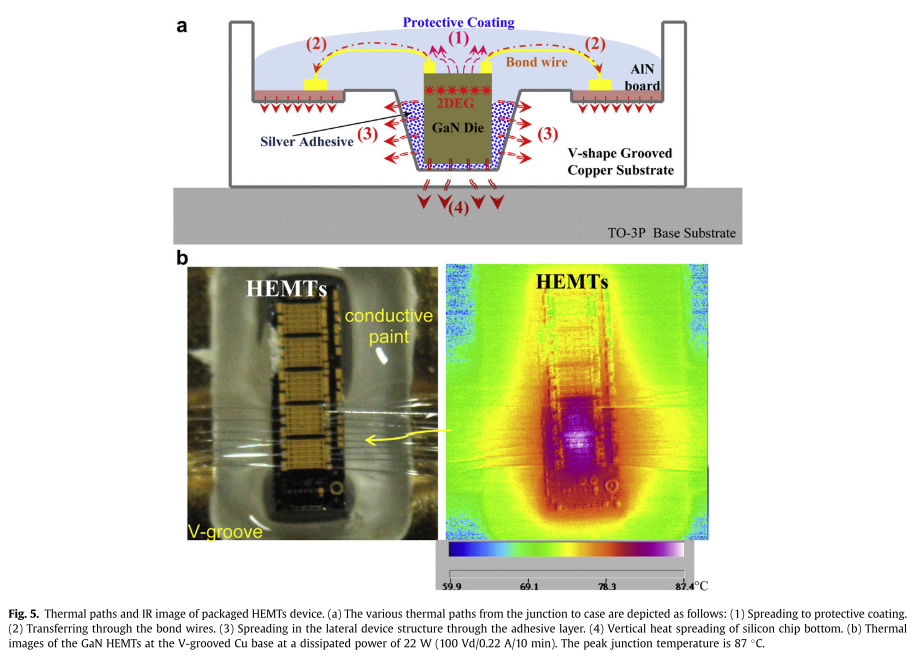

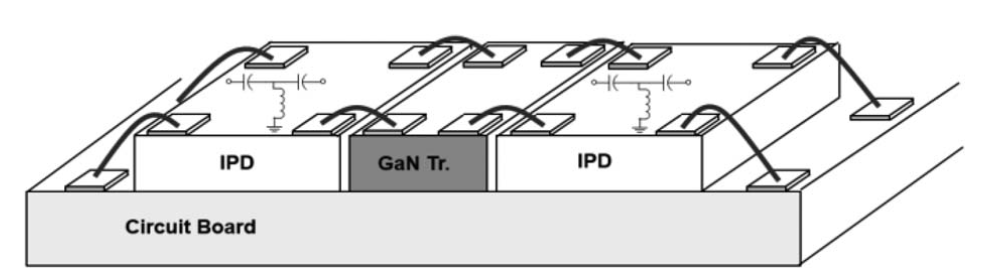

在GaN器件的封裝中,引線鍵合也是最常采用的互連技術。以GaN HEMTs的某個典型封裝為例,(Applied thermal engineering 51.1-2 (2013): 20-24.),內部裸Die的部分就是連到一起的6組每組10個finger的GaN晶體管,共計60個晶體管構成了一個多柵GaN器件。

通過引線鍵合,把這60個晶體管的柵極和漏極,統一連接到柵極pad和漏極pad上,這兩個pad再分別和左右兩邊的引腳相連,源極的部分和中間一整片引腳相連,最后封裝好后對外界體現出來的,就是一個三端子的HEMT黑盒,這種長著三個引腳的封裝形式稱為晶體管外形封裝(Transistor Outline,TO)。

中間的GaN Die部分,就是文章里常說的近結區域(Near-junction Region),整個GaN器件起到作用的部分就是這里。

載帶自動焊

從上面的動畫里也能看出來,引線鍵合必須對每一個觸點分別打線,效率比較低,一個改進的想法就是只操作一次,就能同時連好所有的線。TAB技術就是先根據裸片的I/O接口分布,制作一條特制的載帶,載帶可以被看成是最早的柔性電路,在有機薄膜上,裸片引腳的對應位置提前加工好金屬比如銅引腳,然后只要把載帶貼到裸片上,一次性就實現了所有接口的連接。

倒裝芯片

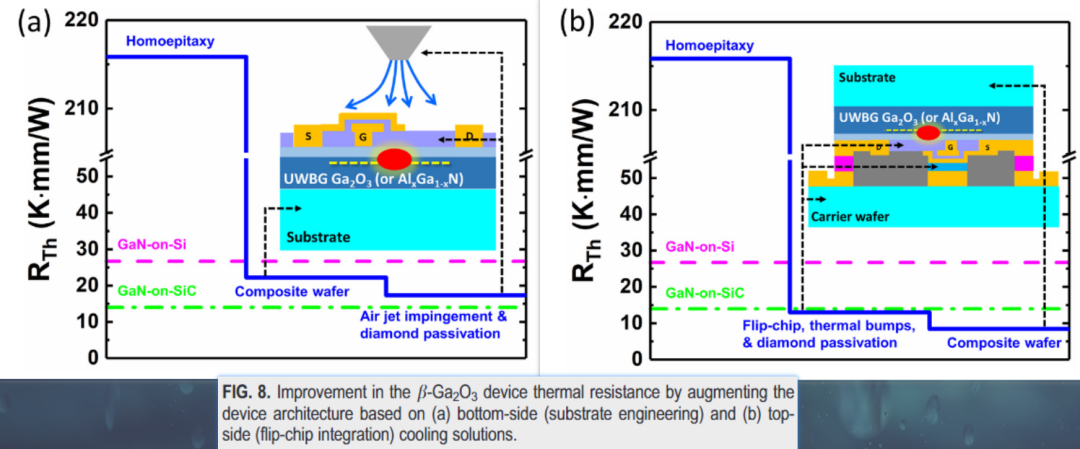

像上面一樣,在標準封裝中,芯片正面朝上貼裝到基板上,通過線來將芯片與基板上對應結點相連接。相對地,在倒裝技術中,不再通過連線實現裸片和基板的相連,而是將裸片倒過來放置,通過金屬焊球直接實現連接,這種方案減小了信號傳輸的距離,提高了信號傳輸速度。

倒裝對傳熱也有一定的幫助(Applied Physics Letters* 119.17 (2021): 170501.),傳統封裝是把襯底貼到封裝上,這時候下部的導熱路徑太長,上部的導熱路徑太短,把裸片倒過來放,讓下面貼到封裝上,把襯底放到上面,下面可以繼續加一些熱泵或者塞一些高熱導率的填充物把熱點連到擴熱板上,上方的襯底也可以換成高熱導率材料,這時候兩條路徑都可以實現熱量輸運。

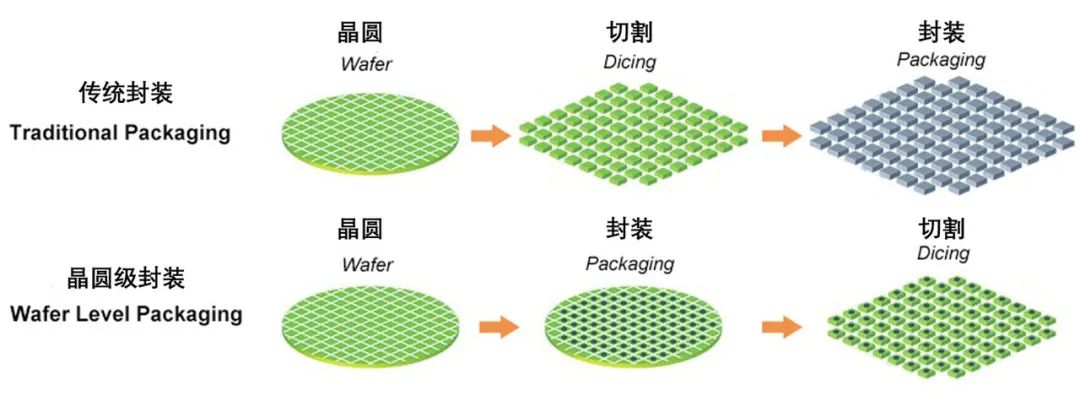

晶圓級封裝

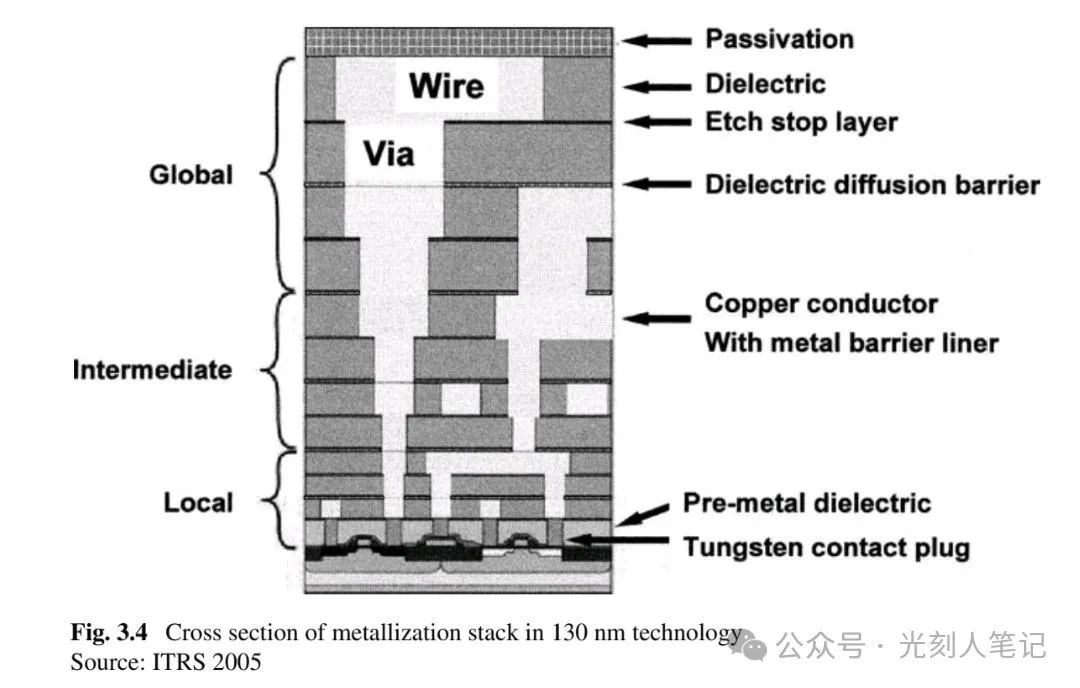

晶圓級封裝實際上是一種封裝類型,但是為了互連,封裝中存在重布線層(Redistribution Layer),通過焊球進行連接。在潔凈室的IC制造分為兩道工序,前道工序(Front End of Line,FEOL)負責形成CMOS晶體管結構,在金屬互連層沉積之前的工序都可歸為FEOL;在晶體管結構加工完畢了,需要進行金屬布線來給晶體管進行供電并實現信息交換,這部分屬于后道工序(Back End of Line,BEOL)。在后道工序結束后,把做好的晶圓交給封測廠,封測廠進行晶圓測試,把晶圓切割成單個芯片,然后再進行對每一個芯片進行單獨封裝,這部分工序一般稱為(back-end process,or post-fab)。fab就是fabrication的縮寫,IC fabrication,在集成電路領域fab指的就是晶圓廠,post-fab,就是晶圓廠之后的事了。晶圓級封裝就是在晶圓的狀態就對芯片進行封裝,封裝好了以后再切割成單個芯片,保護層以及對外的電路連接接口在切割前就已經完成。這種封裝方式可以做到幾乎和裸片一樣的封裝尺寸,且由于連線較短,信號傳輸速度也較高,同時也能降低工業成本以及縮短生產周期。

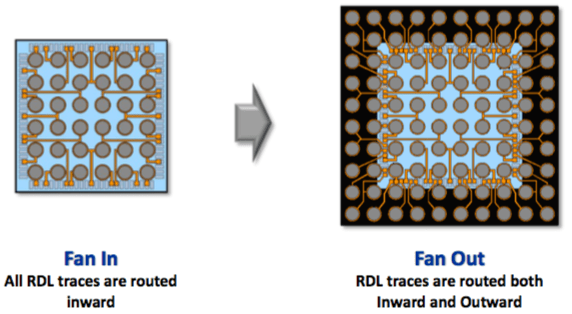

晶圓級封裝又可以分為扇入型晶圓級封裝(FIWLP)和扇出型晶圓級封裝(FOWLP)。裸片上存在IO接口,但是這些IO接口的位置可能不太好,對于某些復雜的封裝工藝這些接口可能很難與封裝的接口相連接,于是RDL工藝就誕生了,RDL是一層金屬互連線,與裸片的IO接口相連,重新排布這些IO接口的位置,以便裸片更容易地與載體相連接。

扇入(Fan In,FI)就是在原芯片尺寸內部將所需要的IO接口重排布完成,封裝尺寸基本等于芯片尺寸,在IO接口數量比較小的情況下可以采用這種技術。而當IO接口數量很大,在現有芯片的尺寸內已經放不下這些錫球了,就可以扇出(Fan Out,FO)技術,通過特殊的填充材料人為擴大芯片的封裝尺寸,在擴充后的整個范圍內走線和排布IO。

FIWLP就是對晶圓上的每個芯片做Fan In封裝,FOWLP就是先把整個晶圓上的不同芯片切下來,然后把他們整體移植到一個更大的晶圓上,然后對更大的晶圓做晶圓級封裝。

硅通孔

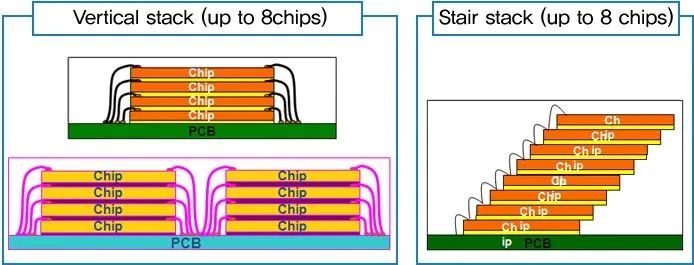

想要將很多芯片疊起來,實現他們之間的互聯,可以采用下面這個方案,每一層都通過引線鍵合連到最下面的基板上,通過基板來實現芯片間的互連。

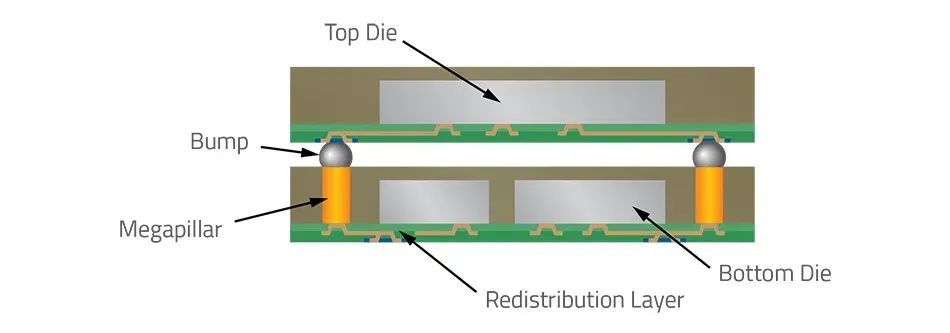

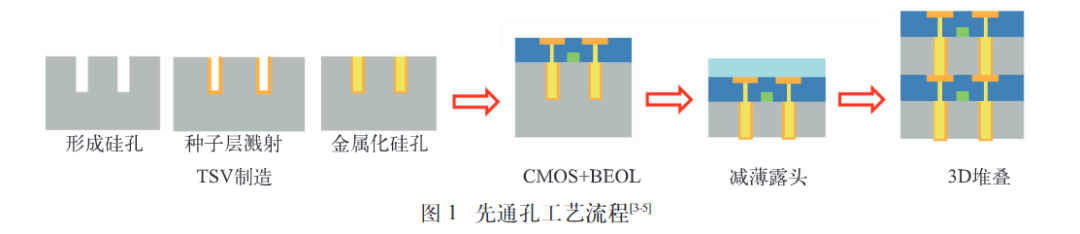

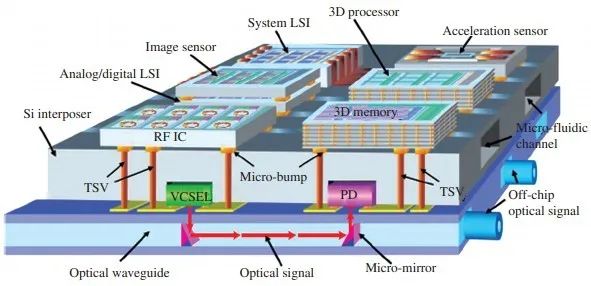

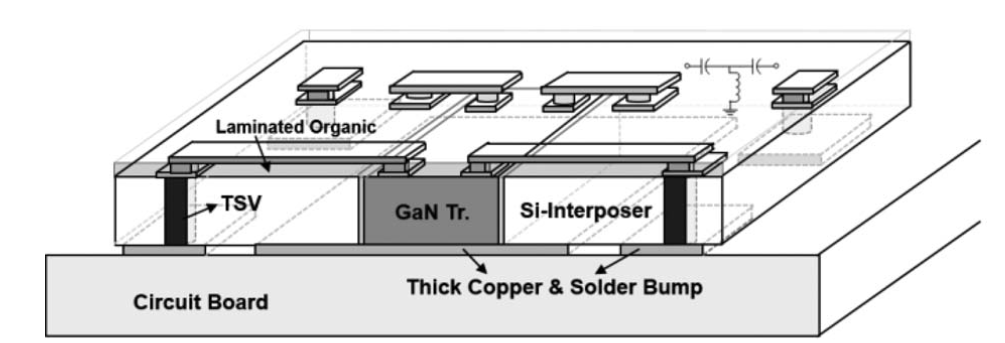

但是這種方案沒有很好地利用垂直空間,引線太多且比較長,信號傳輸比較慢。一個想法就是把堆疊的芯片之間相互垂直聯通,于是TSV就產生了,把裸片放在硅中介層(Si interposer)上,加工一些列的貫通孔,在孔中沉積銅、鎢等導電物質,覆蓋結構的頂部,實現通過硅通孔的垂直電氣導通,實現堆疊芯片間的互聯。TSV的引入使得裸片之間可——+以直接互連,而不需要通過大量的引線在基板上再實現互連,可以提高更高密度的集成、以及更快的信息傳輸速度。

GaN Hybrid-IC 也有采用TSV來替代打線來構造回路(Microw. Opt. Technol. Lett., 59: 1087-1092.)。

審核編輯:湯梓紅

-

集成電路

+關注

關注

5423文章

12038瀏覽量

368237 -

三極管

+關注

關注

145文章

3657瀏覽量

124571 -

封裝

+關注

關注

128文章

8651瀏覽量

145361 -

互連技術

+關注

關注

0文章

28瀏覽量

10521 -

GaN

+關注

關注

19文章

2204瀏覽量

76698

原文標題:【半導光電】封裝互連技術

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文詳解銅互連工藝

一文詳解半導體封裝的封裝互連技術

一文詳解硅通孔技術(TSV)

一文詳解封裝互連技術

一文詳解封裝互連技術

評論