大型鋼結構建筑,汽車,山脈,甚至人類都能在真正的大氣閃電中幸存下來。人類也可以創造自己的微型閃電(火花)并生存下來。然而,當這些火花到達IC時,會產生重大故障。在本教程中,我們將討論保護印刷電路板(PCB)免受ESD破壞的方法。我們將展示具有較大幾何尺寸的模擬器件是保護具有較小幾何尺寸的現場可編程門陣列(FPGA)的最佳選擇。通過采取這些措施,FPGA中的IC可以保持更可靠,并提供一致的質量性能。

介紹

閃電可以是有趣和娛樂的,也可以是危險的和破壞性的。也許所有這些事情同時發生——這取決于你在哪里,你在做什么,以及你的身高。對于IC來說,閃電從來都不是好事。

幾年前,我們在一棟10層高的鋼結構酒店大樓里。下午的閃電風暴穿過一大片空地。由于建筑物的鋼框架,我們感到舒適安全。我們的電腦沒有插電,所以這無關緊要。當風暴過去時,這是一場壯觀的表演,持續了大約 10 分鐘。

大型鋼結構建筑,汽車,山脈,甚至人類都能在真正的大氣閃電中幸存下來。人類也可以創造自己的微型閃電(火花)并生存下來。然而,當這些火花到達IC時,會產生重大故障。納米高的晶體管需要保護才能在人類的火花中生存。在本教程中,我們將討論保護印刷電路板(PCB)免受ESD破壞的方法。我們將展示具有較大幾何尺寸的模擬器件是保護具有較小幾何尺寸的現場可編程門陣列(FPGA)的最佳選擇。通過采取這些措施,FPGA中的IC可以保持更可靠,并提供一致的質量性能。

兩個視角的火花

人類產生的火花從何而來?它們是由摩擦電荷引起的。這是一個大詞。當兩種材料接觸(摩擦幫助)然后分離時,就會發生這種情況。一些電子會轉移到其中一個項目上。有多少電子移動以及移動到哪個表面取決于材料的成分。這是一種普遍現象,因為幾乎所有材料、絕緣體和導體都表現出摩擦電特性。我們熟悉許多常見的來源。撫摸貓的皮毛,在頭發上摩擦氣球,在地毯上行走都可以表現出摩擦電效應。

靜電放電基礎知識教程1說明了人類在各種活動中產生的電壓。表1列出了這些電壓與相對濕度(RH)的關系。

| 典型電壓電平 | ||

| 生成方式 | 10% 至 25% 相對濕度 | 65% 至 90% 相對濕度 |

| 走過地毯 | 35,000V | 1,500V |

| 走過乙烯基瓷磚 | 12,000V | 250瓦 |

| 在未接地的長凳上工作 | 6,000V | 100瓦 |

| 從長凳上拿起塑料袋 | 20,000V | 1,200V |

| 坐在帶有聚氨酯泡沫的椅子上 | 18,000V | 1,500V |

難怪當我們走過地毯并觸摸門把手時會很痛!一般規則是,5,000V 可以在 0% RH 空氣中跳躍約 4 厘米(50.<> 英寸)。對于五六英尺高的人來說,這是一個火花;這很痛苦,但我們活了下來。現在改變你的觀點。這種火花會對幾微英寸高的東西造成什么破壞,比如集成電路(IC)中的晶體管?在這種情況下,厘米的火花是一個巨大的、可怕的閃電顯示。

現在,我們可以轉向IC。長期以來,微處理器一直引領著數字半導體的密度改進。制造技術導致了越來越小的晶體管。1971 年,英特爾? 4004 計算機處理單元 (CPU) 以 10μm 的幾何形狀推出。在 1980 年代和 1990 年代,該過程制造的零件比細菌還小。2012年,IC的密度接近1年技術小000倍,芯片上的功能比病毒還小。1971 年,人們可以在一個封裝中購買具有 2012 納米功能和 28 億個晶體管的 FPGA。2未來有望在未來幾年內將這一密度翻一番。小型晶體管緊密封裝在一起,需要在低電壓(通常為1V及以下)下工作以控制產生的熱量。

要透視28nm,請注意零:它是28億分之一米(0.000000028)。設舊金山和紐約市之間的距離表示一米(約 4000 公里或 2500 英里)。現在28nm(36萬分之一)是0.11米或4.4英寸。閃電必須有多大才能損壞如此小的幾何設備,以及如何保護如此必要且有用的FPGA?

簡單的答案是使用連接數字和模擬世界的I/O接口設備。模擬混合信號IC采用相對較大的幾何形狀(比數字尺寸大10至100倍)和更高的電壓(通常為20V至80V或更高),這使得它們比微型數字晶體管更堅固。雖然當今的模擬混合信號器件通常可以容忍ESD,但它們確實受益于分立式ESD器件。3

了解火花造成的損害

半導體制造商非常重視電氣過應力(EOS)和靜電放電(ESD)。首先,出于顯而易見的原因,EOS和ESD會在制造,封裝組裝和測試過程中破壞零件。但更重要的是,這些負面力量直接影響客戶手中電路的質量和壽命。

起初,電應力過大的部件可能看起來功能正常。它甚至可能以略微降級的方式運行,但仍通過自動測試設備(ATE)的檢查,但后來在現場失敗。EOS和ESD故障是可以預防的,毫無疑問,這是關鍵的質量控制問題。

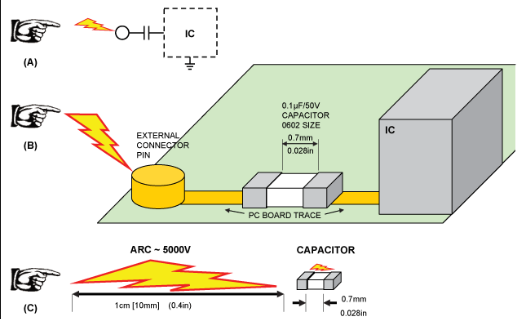

在制造業中構建IC是EOS和ESD損壞的第一個地方。圖1A顯示了PCB的原理圖。我們可能認為IC由串聯電容器保護。事實并非如此。損壞的第二個機會是當客戶將IC安裝在PCB上以構建產品時。仔細觀察圖1B,我們發現電容器的工作電壓為50V,但兩個金屬端連接之間的距離僅為0.28英寸(7mm)。由于火花剛剛跳躍0.4英寸(1厘米),因此電容器周圍的小間隙很容易受到影響。結果可能是IC付出了壽命(圖1C)。最后,當客戶在其環境中操作產品時,可能會發生EOS或ESD損壞。

圖1.板級EOS和ESD問題的根源。

當然,造成重大損害的機會很多。我們實際上可以看到IC內部EOS和ESD破壞的結果。為此,必須去除包裝環氧樹脂材料。這通常是在雙手套隔離盒中使用熱酸完成的。這個過程是非常危險的。煙霧是致命的。一口氣會導致痛苦的死亡;人體皮膚上的一滴酸充其量會導致手或手臂截肢,或者最壞的情況是死亡。

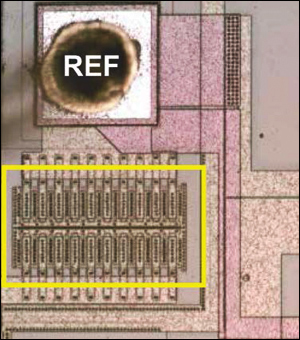

縮微照片圖2A顯示沒有明顯的損壞。提供了標有 REF 的鍵合線和焊盤,以便我們可以定位自己并比較照片。液晶材料涂在模具上(粉紅色),類似于情緒戒指和兒童額頭溫度計中使用的液晶。它隨著溫度的微小變化而改變顏色。當IC通電時,消耗過電流的區域(此處用黃色框標記)會加熱并改變顏色。這是一個熱點。這很有趣,但是是什么導致了問題?

圖 2A.可見光下的電路沒有明顯的EOS或ESD損壞。電路的液晶區域(用黃色標記)因受熱而損壞。

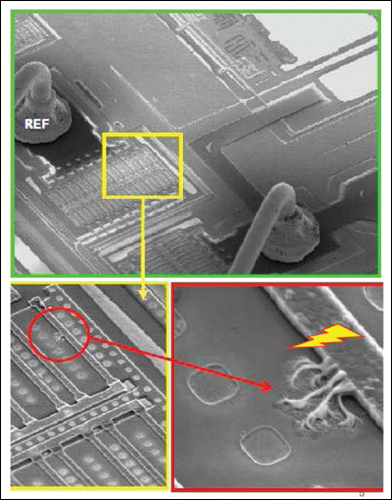

REF鍵合線(圖2B)表示該圖像旋轉了45度。隨著我們逐漸放大,我們看到電遷移。EOS在電應力的影響下損壞越來越大,因此引起了短路。這個過程可能會隨著時間的推移而發生,并在許多短應力期間進行,直到零件突然失效

圖 2B.電路的掃描電子顯微鏡照片如圖2A所示。

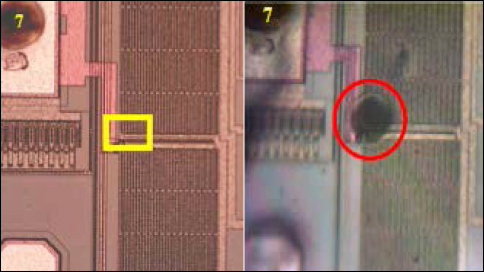

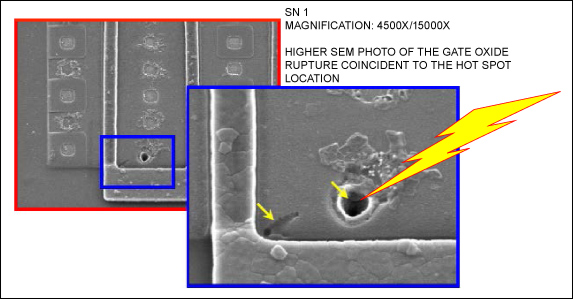

為了進行比較,現在我們研究另一個IC,其中閃電導致快速破壞(圖3)。

圖3.可見光下的電路(左)顯示閃電沒有明顯的損壞。顯微鏡下的同一電路(右)顯示了損壞的熱點。

圖 7 中每個圖像左上角的“3”用于方向。在可見光下看不到太多東西,但在放大鏡下,液晶顯示出溫升和產生的EOS。

圖4繪制了圖3中電路的數據,我們看到已知良好的器件呈現出清晰、可重復的曲線。施加4.5V時,垂直軸上的電流增加。當電流接近250μA時,形成拐點;隨著電壓的增加,電流保持在250μA。 圖4還顯示,有缺陷的部分繼續在膝蓋上方吸收更多的電流。

圖4.圖3所示電路的半導體曲線示圖。曲線示圖器電流/格為 50μA;電壓/格為1V。

仔細檢查后,部件序列號 1 (SN1) 顯示柵極氧化物上有一個孔(圖 5)。閃電使基板的柵極短路,導致過大的電流流動。當然,晶體管付出了生命的代價。典型的柵氧化層厚度為5nm至15nm,具體取決于制造工藝。在致密的數字微處理器部件中,氧化物的厚度可以是1.2nm至3nm。為了說明這有多薄,在硅中,1.2nm是~5或6個原子厚。因此,對于幾納米高的門來說,幾乎任何火花都是一個巨大的閃電。

圖5.圖3所示電路的掃描電子顯微鏡照片。閃電在柵氧化層上造成一個孔,使電路短路。

對抗火花并保護電路

我們將快速討論如何保護IC和PCB免受火花和EOS / ESD的影響。

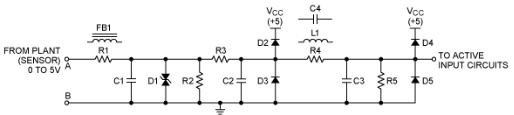

火花的上升時間非常快,因此我們可以減慢它的任何方法都會降低峰值電壓。ESD結構(圖6和圖7)通常用于系統中的兩個位置:板級輸入和串聯電阻輸出;電感器以及接地電容,可用作低通濾波器。因此,通過分立硅(小信號或參考)肖特基二極管、雪崩(齊納二極管)、瞬態電壓抑制(TVS)二極管、氣管放電器件、電阻器、電感器和金屬氧化物壓敏電阻(MOV)的組合,可以保護PCB免受EOS/ESD。

圖6.建議的分立元件清單,可以防止不必要的電氣漏洞。

圖7.簡化的靜電放電結構。

圖7A至C的ESD結構位于IC內部。用于EOS/ESD保護的外部分立元件往往在物理上更大,并承載更大的電流。除了許多產品內置的ESD保護外,設計人員還可以使用MAX14541和MAX3203等專用ESD保護器件。

需要注意的是,許多電路具有內置的EOS/ESD保護功能,盡管這不是它們的主要功能。考慮一下MAX5481系列10位非易失(NV)電位器、MAX5134四通道16位DAC和MAX6001系列低功耗、低成本電壓基準。仔細查看數據手冊會發現沒有提到ESD。但ESD規格取決于IC制造工藝,并在每個部件的可靠性報告中說明。您可以從Maxim網站上每個器件的概覽頁面開始查找ESD信息。頁面底部附近是技術文檔區域和可靠性報告。4單擊此處將顯示可靠性報告頁面。如果可靠性報告未聯機,則可以請求。

總結

無論大小,鋼結構建筑、汽車、山脈,甚至人都能在真實的大氣閃電中幸存下來。五到六英尺高的人類可以并且經常這樣做,創造自己的微型閃電(火花),甚至幾乎沒有注意到。納米高的晶體管從來不是這種情況。它們需要保護才能在人類的火花中幸存下來。正如我們所看到的,防止電路板電路和IC的EOS和ESD破壞對于可靠、優質的產品性能至關重要。電路設計人員應警惕在其設計中使用EOS/ESD保護電路,或確保從一開始就使用具有內置ESD保護的電路。忽視任何看似微不足道的火花都是一個嚴重的疏忽......不管你有多高...或者不是。

審核編輯:郭婷

-

FPGA

+關注

關注

1643文章

21979瀏覽量

614510 -

ESD

+關注

關注

49文章

2268瀏覽量

175207 -

PCB

+關注

關注

1文章

2057瀏覽量

13204

發布評論請先 登錄

閃電或火花造成的傷害—這取決于你的身高!

閃電或火花造成的傷害—這取決于你的身高!

評論