芯片要工作就需要讀取指令,解析指令然后運(yùn)行指令,需要在某種固定的周期性運(yùn)動(dòng)的設(shè)備驅(qū)動(dòng)下有條不紊的進(jìn)行,它就是頻率。

默認(rèn)情況下I.MX6ULL工作在默認(rèn)頻率下(396MHz),工作頻率相對(duì)保守。為了更好發(fā)揮I.MX6ULL的性能,需要對(duì)它的時(shí)鐘頻率進(jìn)行配置。I.MX6ULL開發(fā)手冊(cè)標(biāo)注的內(nèi)核最高頻率支持528MHz,實(shí)際上它還可以超頻到696MHz。

配置內(nèi)核頻率

I.MX6ULL支持24MHz與32.768kHz兩個(gè)OSC,32.768為低頻率,目前使用的所有時(shí)鐘來(lái)源都是24MHz。

從上面這張圖可以看出,

從上面這張圖可以看出,pll1_sw_clk是進(jìn)入到內(nèi)核頻率的,通過CCSR的pll1_sw_clk_sel來(lái)選擇到底使用哪一路作為最終進(jìn)入ARM內(nèi)核頻率。step_clk在這里通過CCSR的step_sel選擇為與OSC相同頻率24MHz,它主要是用于在配置pll1_main_clk時(shí)的備用頻率使用。

- 讀取

CCSR的第2位值,如果是0表示當(dāng)前選擇的是pll1_main_clk,需要將它切換到step_clk,同時(shí)將step_clk選擇成24MHz頻率

/// CCM->CCSR的第二位判斷是否選擇的是pll1_main_clk(值是0)

if (((CCM->CCSR >> 2) & 0x1) == 0)

{

/// 需要先切換時(shí)鐘源到24MHz晶振

CCM->CCSR &= ~(1 << 8);

CCM->CCSR |= (1 << 2);

}

-

/// bit 13: enable register /// 配置(696MHz) CCM_ANALOG->PLL_ARM = (1 << 13) | (58); /// 分頻器配置為1 CCM->CACRR = 0; /// 將時(shí)鐘源切換回CCSR的第二位判斷是否選擇的是pll1_main_clk CCM->CCSR &= ~(1 << 2);這里配置了一個(gè)超頻數(shù)值696MHz

8路FPD配置

BYPASS_CLK_ SRC(15 - 14)配置成0x0,即選擇使用24MHz作為時(shí)鐘源ENABLE(13)配置成1即使能時(shí)鐘頻率輸出DIV_SELECT按公式(PLL output frequency = Fref * DIV_SEL/2)配置CCM的CACRR的1-3位配置分頻器的值- 配置完成切換回

pll1_main_clk

到目前為止,會(huì)使用到的PLL除了內(nèi)核以外還有PLL2與PLL3。PLL2與PLL3是固定的頻率,但他們都各分出去了4路FPD是可以靈活配置的。 上面紅色框里面看到的就是。分別有兩個(gè)寄存器控制,

上面紅色框里面看到的就是。分別有兩個(gè)寄存器控制,PLL2是CCM_ANALOG_PFD_528n, PLL3是CCM_ANALOG_PFD_480n。配置的公式是 528(480) * 18 / 實(shí)際頻率,具體配置代碼如下:

/// 配置PPL2(528MHz)的PFD0 ~ FPD3

int reg = CCM_ANALOG->PFD_528;

/// PFD0: 352MHz

reg |= (27 << 0);

/// PFD1: 594MHz

reg |= (16 << 8);

/// PFD2: 396MHz

reg |= (24 << 16);

/// PFD3: 297MHz

reg |= (32 << 24);

CCM_ANALOG->PFD_528 = reg;

/// 配置PPL3(480MHz)的PFD0 ~ FPD3

reg = CCM_ANALOG->PFD_480;

/// PFD0: 720MHz

reg |= (12 << 0);

/// PFD1: 540MHz

reg |= (16 << 8);

/// PFD2: 508.2MHz

reg |= (17 << 16);

// PFD3: 454.7MHz

reg |= (19 << 24);

CCM_ANALOG->PFD_480 = reg;

配置完成后,燒寫后可看到實(shí)驗(yàn)07中的LED0與BEEP閃燈與響聲的頻率更高了,這是由于內(nèi)核工作在了更高的頻率。

-

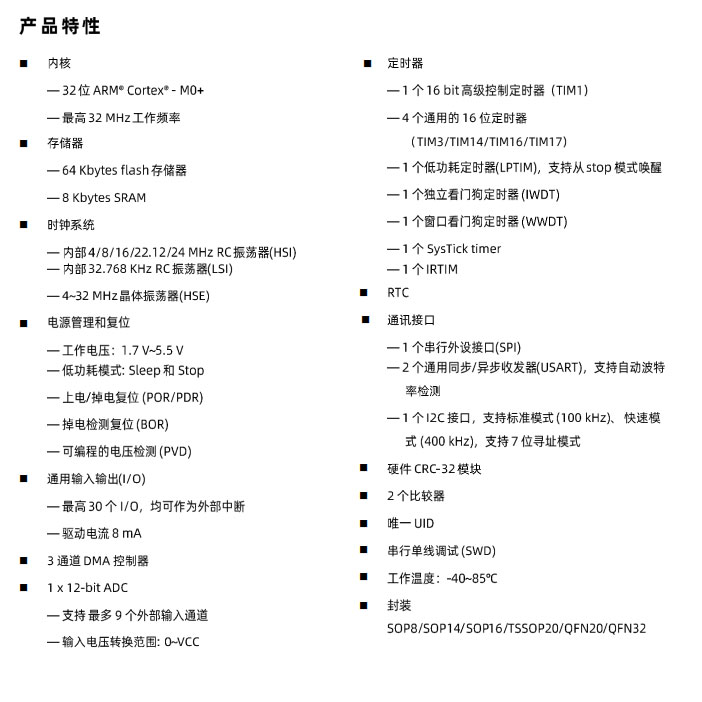

芯片

+關(guān)注

關(guān)注

460文章

52529瀏覽量

441306 -

頻率

+關(guān)注

關(guān)注

4文章

1562瀏覽量

60395 -

指令

+關(guān)注

關(guān)注

1文章

616瀏覽量

36501

發(fā)布評(píng)論請(qǐng)先 登錄

arm內(nèi)核結(jié)構(gòu)

賽靈思發(fā)布1GHz頻率ARM內(nèi)核的FPGA

48 第14.3講 主頻和時(shí)鐘配置實(shí)驗(yàn)-8路PLL和8路PFD時(shí)鐘設(shè)置 - 第1節(jié)

48 第14.3講 主頻和時(shí)鐘配置實(shí)驗(yàn)-8路PLL和8路PFD時(shí)鐘設(shè)置 - 第3節(jié)

48 第14.3講 主頻和時(shí)鐘配置實(shí)驗(yàn)-8路PLL和8路PFD時(shí)鐘設(shè)置 - 第4節(jié)

ADRF6850 PFD頻率泄露frequence leakage

「正點(diǎn)原子Linux連載」第十六章主頻和時(shí)鐘配置實(shí)驗(yàn)

對(duì)于輸入頻率130MHz左右的pll設(shè)計(jì),應(yīng)該選擇哪種結(jié)構(gòu)的PFD比較好?

I.MX6ULL時(shí)鐘樹的相關(guān)資料推薦

如何對(duì)RK3399 CPU arm64的內(nèi)核進(jìn)行配置

XN31202雙路PLL頻率合成器

arm內(nèi)核全解析_arm內(nèi)核體系結(jié)構(gòu)分類介紹

32位ARM?Cortex?-M0+內(nèi)核單片機(jī)XL32F003系列MCU

ARM內(nèi)核及8路PFD頻率怎么配置

ARM內(nèi)核及8路PFD頻率怎么配置

評(píng)論