UltraScale是基于20nm工藝制程的FPGA,而UltraScale+則是基于16nm工藝制程的FPGA。盡管兩者工藝制程不同,但內部結構是一致的。若無特殊聲明,下文闡述的UltraScale架構也適用于UltraScale+。

全局時鐘管腳

在UltraScale中,每個輸入/輸出區域(I/O Bank)都位于單一的時鐘區域CR(Clock Region)內,且都包含52個輸入/輸出管腳。在這52個管腳中,有4對(8個)全局時鐘管腳GC(GlobalClock I/O)。其使用方法與7系列FPGA是一致的。

不同之處在于,這4對GC地位是等同的,不再有MRCC和SRCC之分。UltraScale+新增了高密度輸入/輸出區域(HD I/O Bank, High Density I/O Bank),位于此區域內的全局時鐘管腳HDGC只能通過BUFGCE連接到MMCM或PLL。

時鐘緩沖器

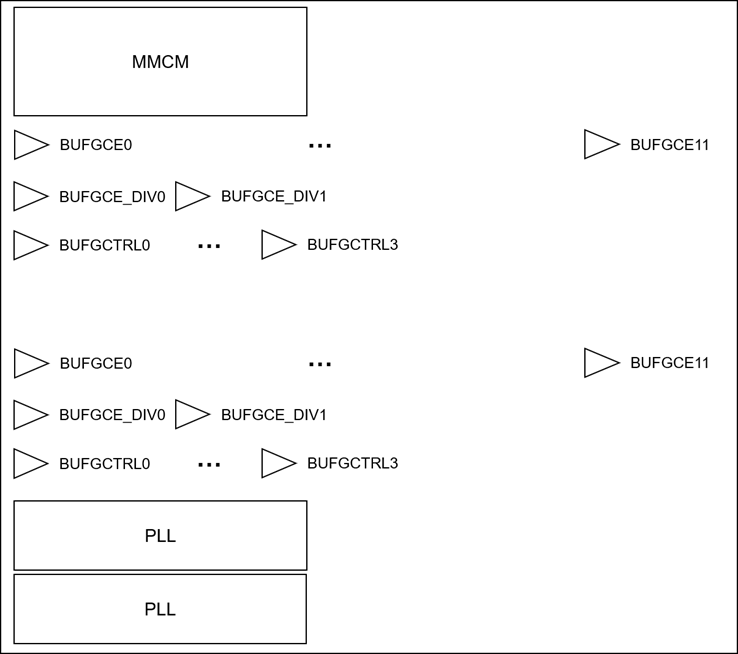

7系列FPGA既包含全局時鐘緩沖器,又包含區域時鐘緩沖器。UltraScale簡化了時鐘緩沖器,即只有全局時鐘緩沖器。包含輸入/輸出列的時鐘區域內有24個BUFGCE、4個BUFGCE_DIV和8個BUFGCTRL,但同時只能使用其中的24個,如下圖所示。

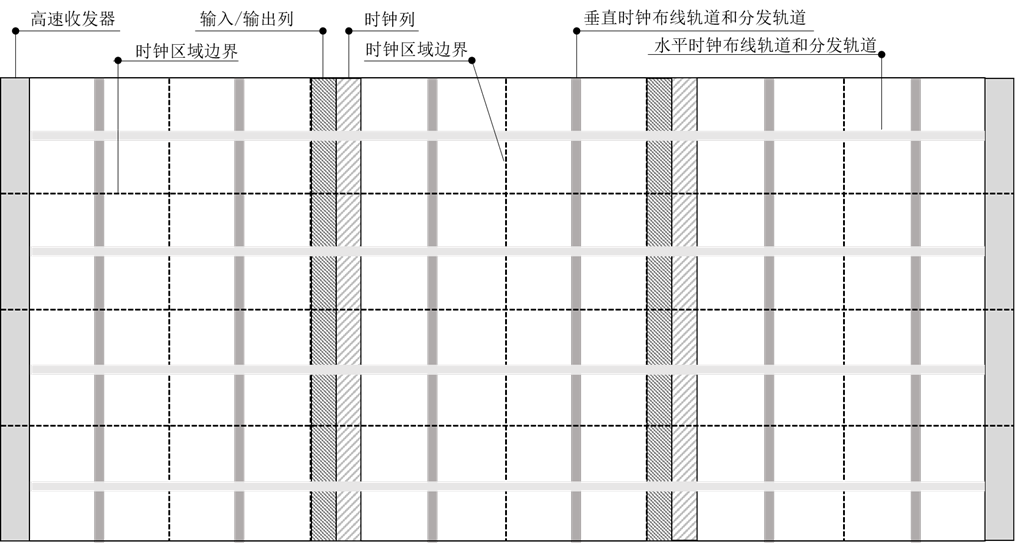

這些全局時鐘緩沖器位于時鐘列,可驅動水平時鐘布線/分發軌道和垂直時鐘布線/分發軌道,其中分發軌道是7系列FPGA所沒有的。這些軌道均位于時鐘區域的中心位置,如下圖所示(有的芯片只有一側會有高速收發器)。不難看出,每個時鐘區域的寬度相比于7系列FPGA有所縮減,不再是半個芯片的寬度,高度由7系列中的50個CLB變為60個CLB。時鐘區域的粒度更加細化。

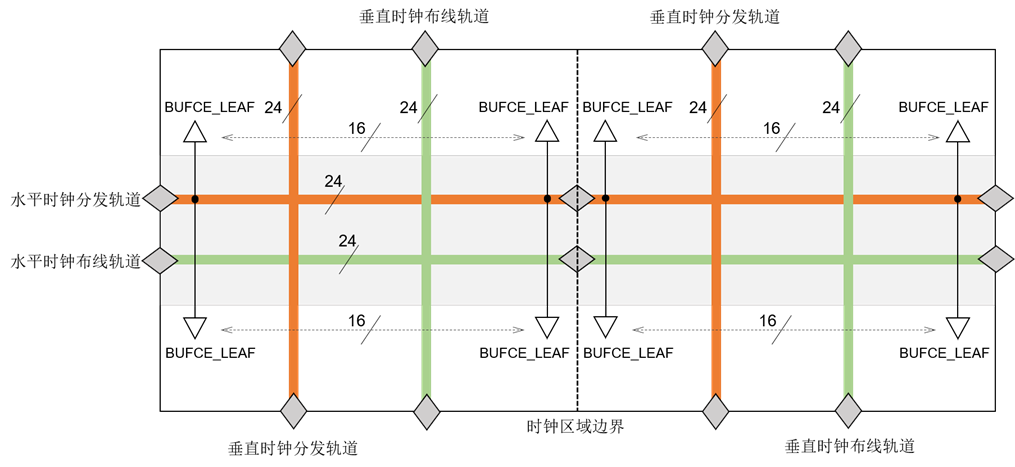

無論是水平時鐘布線/分發軌道還是垂直時鐘布線/分發軌道,都是以時鐘區域作為邊界,這意味著如果某個時鐘區域內的資源未使用時鐘,工具就會關閉相應的軌道,從而節省功耗。布線軌道可驅動相鄰時鐘區域內的布線軌道和分發軌道,但分發軌道只能驅動相鄰時鐘區域內的水平分發軌道。

布線軌道的目的是將時鐘從全局時鐘緩沖器布線到某個中心點。在這個中心點,時鐘經分發軌道連接到其負載的時鐘端口。分發軌道可進一步移動這個點以改善時鐘的局部偏移。這個點我們稱之為時鐘根節點(ClockRoot)。

每個時鐘區域有24個水平時鐘布線/分發軌道和24個垂直時鐘布線/分發軌道。在水平時鐘分發軌道上,有32個BUFCE_LEAF,稱之為葉時鐘緩沖器。時鐘從水平時鐘分發軌道上下來之后經BUFCE_LEAF到達邏輯資源的時鐘端口,如下圖所示。BUFCE_LEAF只能由Vivado自動使用,而不能在代碼中實例化。

UltraScale有獨立的BUFGCE,無需通過BUFGCTRL配置而成。但BUFGCTRL仍是可配置的,例如,BUFGCE_1、BUFGMUX和BUFGMUX_1都是通過BUFGCTRL配置生成的。BUGCE_DIV取代了BUFR,但比BUFR具有更強大的驅動能力,因為它已成為全局時鐘緩沖器。

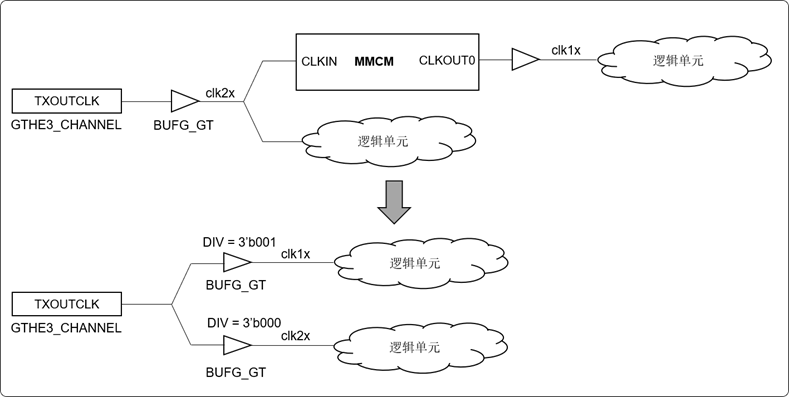

同時,BUFGCE_DIV還具有分頻功能,分頻因子可以是1~8(包含1和8)的整數。只是當分頻因子為奇數時,輸出時鐘的占空比將不再是50%。UltraScale新增了BUFG_GT。BUFG_GT只可以由高速收發器或RFSoC中的ADC/DAC模塊驅動。

BUFG_GT_SYNC是BUFG_GT的同步器,當Vivado推斷出BUFG_GT時會自動在設計中插入BUFG_GT_SYNC。和BUFGCE_DIV類似,BUFG_GT也具有分頻功能,可用的分頻因子為1~8(包含1和8)之間的整數。分頻因子由DIV端口輸入。

DIV位寬為3,當其為3’b000時,對應分頻因子為1。在包含高速收發器的時鐘區域內有24個BUFG_GT。 在Zynq UltraScale+ MPSoC中新增了一種全局時鐘緩沖器BUFG_PS(Zynq 7000系列FPGA中是沒有的)。該緩沖器位于內部ARM處理器的旁邊。

PS側的輸出時鐘需經此緩沖器訪問PL(Programmatic Logic)側的時鐘布線資源,從而驅動PL側的邏輯資源。BUFG_PS的個數因不同的芯片而異。例如ZU4EG有96個BUFG_PS,而ZU2CG有72個BUFG_PS。

應用案例:使用BUFG_GT執行簡單分頻

BUFG_GT具有分頻功能,可支持的分頻因子為1~8(包含1和8)的整數,分頻因子控制字由位寬為3的輸入端口DIV提供。當DIV為3’b000時,對應分頻因子為1。借助BUFG_GT的分頻功能可生成分頻時鐘,從而節省了MMCM,如下圖所示。使用BUFG_GT時要注意其時鐘源。

?

?

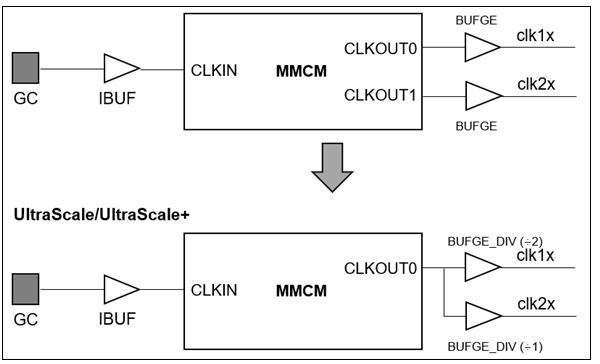

同樣具有分頻功能的時鐘緩沖器還包括BUFGCE_DIV,如下圖所示。BUFGCE_DIV的輸入可來自于MMCM的輸出,圖中clk2x的頻率是clk1x的2倍。使用BUFGCE_DIV可有效降低同步跨時鐘域路徑的時鐘偏移(Clock Skew)。 ?

?

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614719 -

緩沖器

+關注

關注

6文章

2037瀏覽量

46716 -

時鐘緩沖器

+關注

關注

2文章

142瀏覽量

51260 -

時鐘

+關注

關注

11文章

1886瀏覽量

132917

原文標題:時鐘資源(2):UltraScale/UltraScale+ FPGA

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于20nm工藝制程的FPGA—UltraScale介紹

基于20nm工藝制程的FPGA—UltraScale介紹

評論