2022年,集成電路半導體行業最熱的頭條是“EDA被全面封鎖”。如何突破EDA封鎖,成為行業發展的關鍵詞,也是群體焦慮。在全球市場,有人比喻EDA是“芯片之母”,如果沒有了芯片,工業發展和社會進步將處處受制,EDA的重要性也上升到了戰略性高度。盡管國際封鎖形勢嚴峻,但睿智的中國科技人擅于把危機化為機會,從《加快自主研發應用,讓工業軟件不再卡脖子》,到《破解科技卡脖子要打好三張牌》,即一要打好“基礎牌”,提升基礎創新能力;二要打好“應用牌”,加強對高精尖國貨的應用;三是要打好“人才牌”,讓人才留得住、用得上、有發展……,各種政策、舉措和實際行動,處處彰顯了我們中國科技的發展韌性。

我們EDA探索頻道,今天迎來了第13期的內容——MOSFET Scaling-3D Era,下面就跟著小編一起來開啟今天的探索之旅吧~

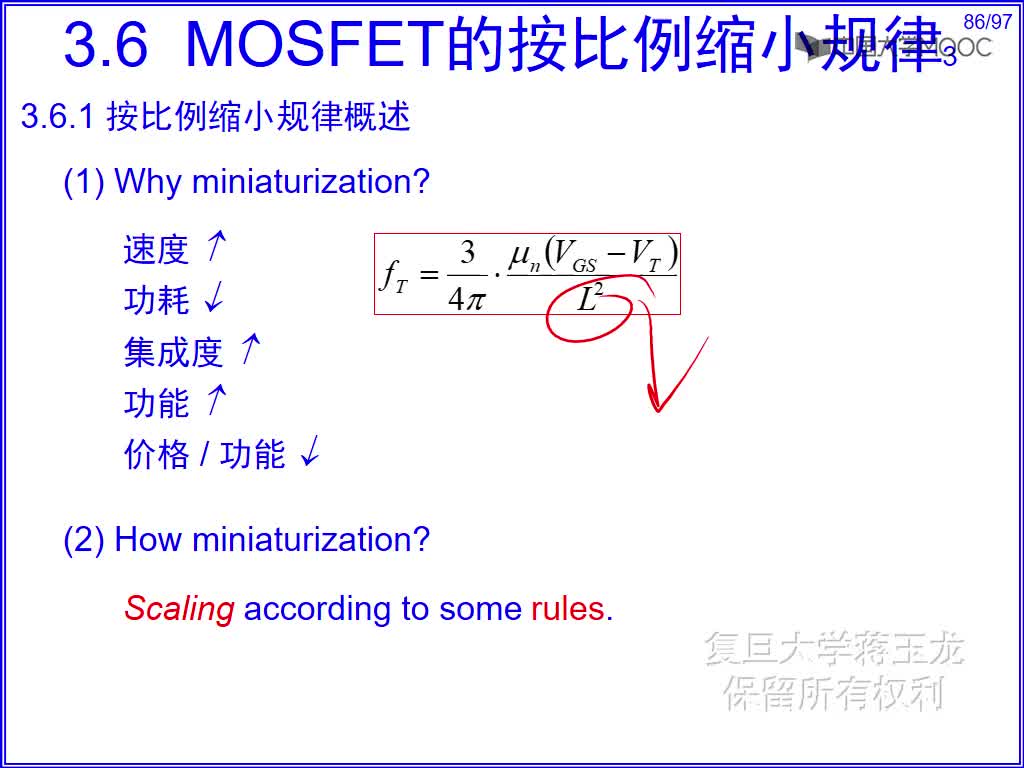

在使用了應力工程和HKMG技術之后,平面MOSFET技術達到了登峰造極的狀態。追求MOSFET的微縮需要對器件的結構做出重大的改變。

全耗盡器件

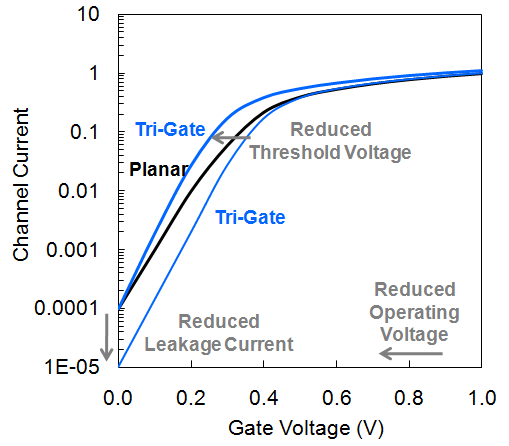

MOSFET性能的基本矛盾點是Ion與Ioff的平衡。粗略地說,提升器件性能或者實現器件微縮有兩個基本的路徑,即保持漏電基本不變的情況下提升驅動電流和保持驅動電流基本不變的情況下抑制漏電。

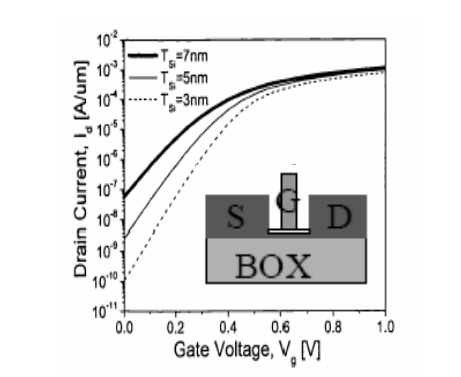

當器件的尺寸越來越小時,漏電的問題會變得越來越明顯。回顧我們之前提到的漏電途徑,DIBL,源漏穿通等等,都指向于淺結深和隔絕體效應。如果把器件做到只有幾十納米甚至幾納米的厚度,則這些次生的效應都將大大削弱甚至消失,那么漏電流就會極大地被抑制。這便是Ultra-Thin-Body MOSFET(UTBMOSFET)的思路。在這種狀態下,溝道在關斷時可以達到完全的耗盡狀態,所以又可以稱為全耗盡器件(Fully Depleted)。

圖:UTB-MOSFET示意圖。硅的厚度越小,漏電也越小。來自Chenming Hu,Modern Semiconductor Devices for Integrated Circuits

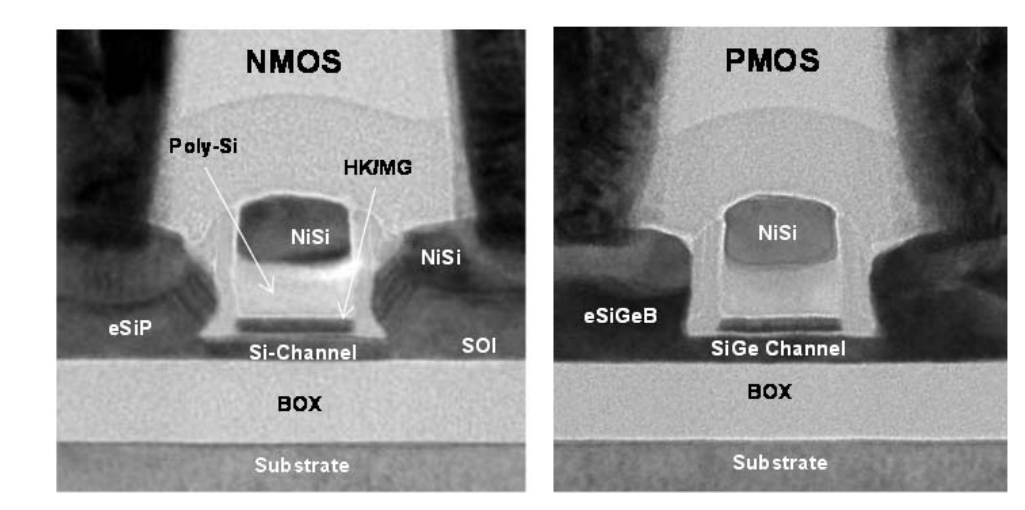

目前主流的實現方式是使用絕緣體上硅(Silicon on Insulator)技術。使用等離子體浸沒注入或者晶圓鍵合技術制造SOI Wafer,在硅下面制造一個氧化硅的埋層,使器件與襯底絕緣。結合器件和制造層面的兩個主要特點,可以把這種方式稱為FDSOI技術。

圖:Global Foundries公開的22nm FDSOI截面照片。來自Carter et al. 22nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications, IEDM 2016

FDSOI實際上也是一種三維器件的集成技術,如SOI的引入、源漏的外延工程都是在三維上操作的,但是由于后續工藝流程制造方式與傳統的平面工藝基本沒有區別,所以一般討論三維器件時并不經常提到FDSOI,而是我們下面要講的FinFET。

FinFET

FDSOI以較低的成本實現了對漏電流的控制。然而對于驅動電流的提升卻貢獻寥寥。目前主要用于一些低功耗的場合。而對于高性能計算芯片的微縮,還是要靠FinFET實現,無論是大電流還是小漏電。

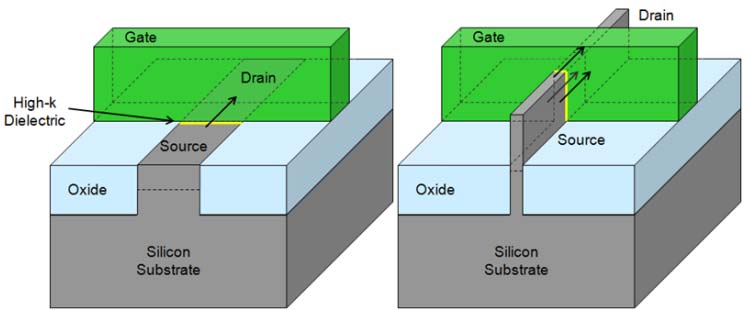

Intel把FinFET稱為Tri-Gate,即三柵器件(屬于多柵器件的一族,包括了雙柵,三柵等類型,篇幅限制不再展開)。相比于平面器件,FinFET把溝道立了起來,三面都有柵極包圍。這使得柵極對于溝道的控制大大增強。從抑制漏電的角度來看,同樣也可實現全耗盡。所以FinFET同時也是一種全耗盡器件。

圖:平面器件和FinFET的示意圖。來自Mark Bohr,The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era, IEDM 2011

另一方面,FinFET實際上實現了更大的W,即電流的通路,隨著器件技術的發展,Fin的高度也越做越高,這樣就給電流更大的流過面積。

結合平面時代就有的應力硅技術,HKMG技術等。FinFET把集成電路的電流密度再次帶上了一個臺階。

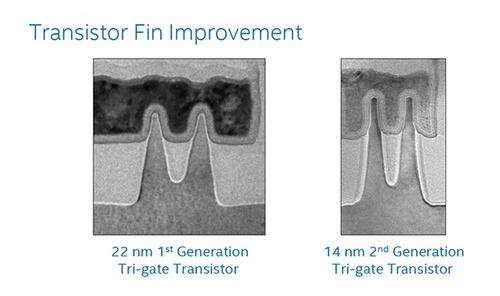

Intel的FinFET截面照片,圖片來自

https://www.eetimes.com/intel-ibm-dueling-14nm-finfets/

圖:FinFET相比于平面器件性能的提升,能實現更小的漏電或更小的閾值電壓。來自Mark Bohr,The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era, IEDM 2011

Intel從22nm技術時代引入了FinFET并沿用至今,代工廠在16/14nm引入了FinFET技術,并且正是在FinFET技術上,臺積電對Intel實現了技術反超。未來臺積即將量產的“3nm”技術仍是基于FinFET的基礎器件設計。然而也正是到了這個節點,FinFET能提供的性能也到了發展的極限。三星對外宣稱的”3nm”技術已經采用了名義上更先進的技術。這就是我們下一期要討論的內容了。

審核編輯 :李倩

-

MOSFET

+關注

關注

150文章

8625瀏覽量

220604 -

晶圓

+關注

關注

53文章

5166瀏覽量

129845 -

eda

+關注

關注

71文章

2932瀏覽量

178070

原文標題:EDA探索丨第13期:MOSFET Scaling-3D Era

文章出處:【微信號:hzwtech,微信公眾號:鴻之微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

EDA簡介(Eng)

FFTC問題求解答!!!動態scaling

探索性數據分析(EDA)及其應用

探索如何打開我國3D打印的應用之路

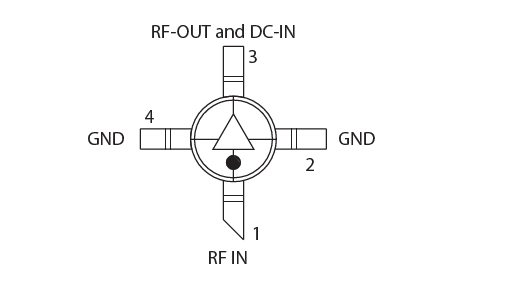

ERA-3SM+寬帶放大器的數據手冊免費下載

3D IC先進封裝對EDA的挑戰及如何應對

EDA探索之MOSFET收縮,Happy Scaling Era

EDA探索之MOSFET的微縮-nanosheet era

EDA探索之MOSFET的微縮- Moore’s Law介紹

在立創EDA中建立器件的3D模型

EDA探索:MOSFET Scaling-3D Era

EDA探索:MOSFET Scaling-3D Era

評論