在使用cadence進行電子電路設計時,我們時常會對到原理圖進行反復修改,并且修改電子元器件的規格型號占很大比重,由于大多數電子元器件的封裝都是自身特定型的,而不是通用型的,因此就很容易涉及到新建和更新其原理圖封裝。

下面筆主就以cadence 16.6為例,詳細介紹一下新建和更新原理圖封裝是如何操作的:

1、新建原理圖封裝

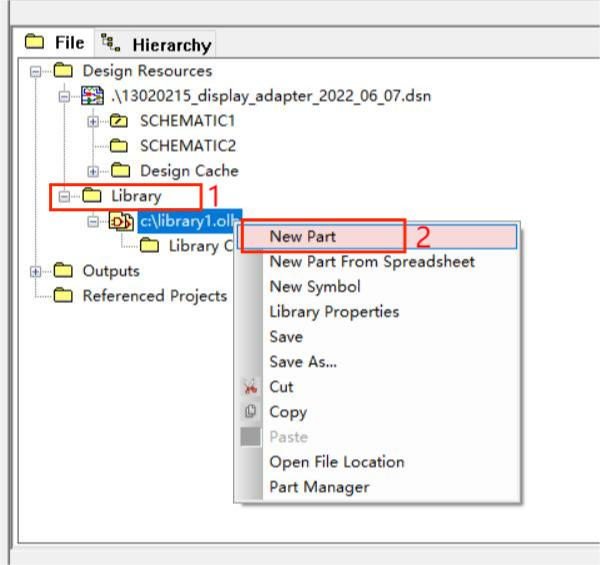

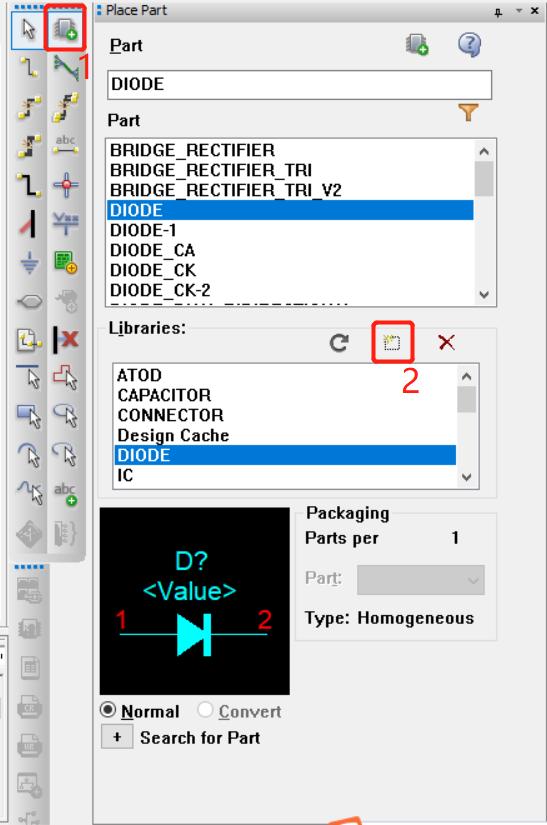

首先打開需要的原理圖文件(即DSN文件),然后找到Library并展開,然后單擊鼠標右鍵,在彈出的對話框中點擊New Part;

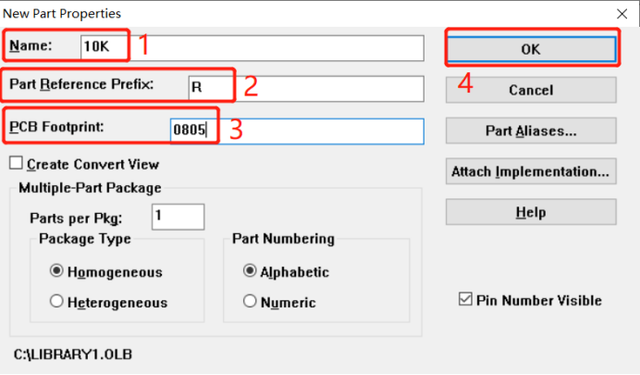

然后在彈出的對話框中,在Name項目下填入元器件的“名稱”,在Part Reference Prefix項目下填入元器件的“電氣代表符號”,在PCB Footprint項目下填入元器件的“PCB封裝名稱”,最后點擊OK;(備注:這里以新建一個封裝為0805的電阻為實例)

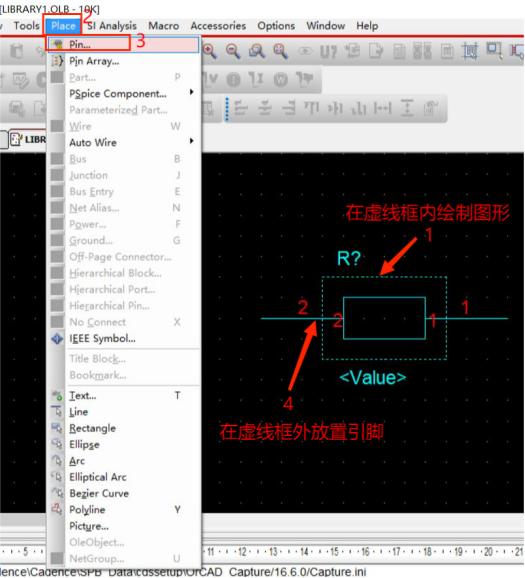

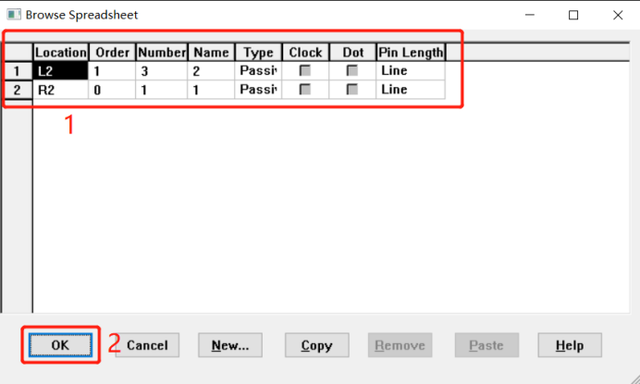

在新建的頁面內,先在虛線框內繪制好元器件封裝的圖形,然后再點擊Place→Pin,在虛線框外放置引腳;

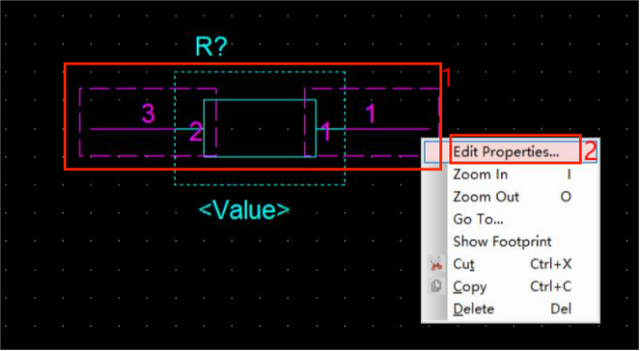

如果需要修改引腳信息,就選中引腳,然后單擊鼠標右鍵,選擇Edit Properties;

在彈出的對話框中修改好需要的引腳信息,然后點擊OK即可。

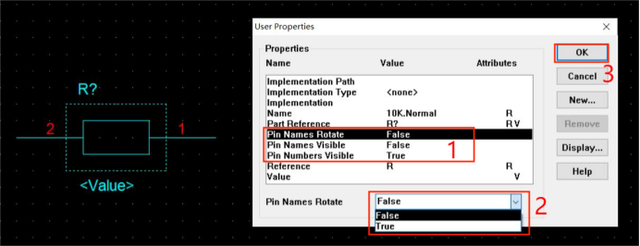

如果需要隱藏引腳名稱或者編號,就鼠標雙擊任意空白處,在彈出的對話框中,將Pin Names Rotate、Pin Names Visible、Pin Numbers Visible全改為“False”;

如果再需要將引腳或者編號顯示出來,則將將Pin Names Rotate、Pin Names Visible、Pin Numbers Visible全改為“True”,最后再點擊OK即可。

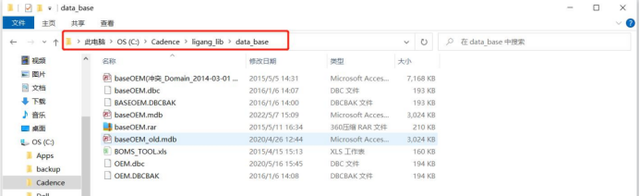

這樣一個原理圖封裝就新建好了,將其添加到封裝庫里面就可以使用了(添加封裝庫的具體步驟可以參考上一篇文章)。

2、更新原理圖封裝

相比于新建原理圖封裝來說,更新已有的原理圖封裝就要簡單很多了。

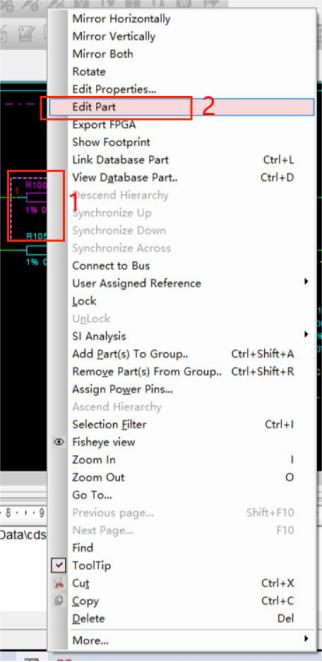

首先在原理圖中選中需要更新的元器件,然后單擊鼠標右鍵,選擇Edit Part;

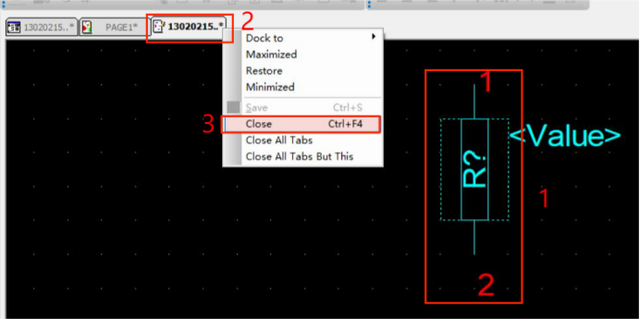

然后在彈出的頁面中,繪制好需要更新的圖形,然后鼠標右鍵單擊頁面,選擇Close;

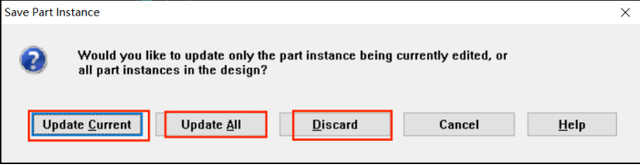

在彈出的對話框中,若選擇Update Current,則為更新當前選中的原理圖封裝;若選擇Update All,則為更新所有使用的原理圖封裝;若選擇Discard,則為不更新原理圖封裝。

以上就是有關新建和更新cadence原理圖封裝的詳細步驟,希望能幫助到需要的朋友們。

-

原理圖

+關注

關注

1323文章

6414瀏覽量

239539 -

元器件

+關注

關注

113文章

4814瀏覽量

94556 -

封裝

+關注

關注

128文章

8590瀏覽量

144966 -

Cadence

+關注

關注

67文章

967瀏覽量

143960 -

電子電路

+關注

關注

78文章

1243瀏覽量

67747

發布評論請先 登錄

cadence新建和更新原理圖封裝的詳細步驟

cadence新建和更新原理圖封裝的詳細步驟

評論