隨著FPGA的不斷發(fā)展,F(xiàn)PGA本身自帶的PCIE硬核的數(shù)量越來越多,本文以ZU11EG為例介紹,如何進(jìn)行對(duì)應(yīng)的硬件引腳分配。

設(shè)計(jì)目標(biāo):ZU11EG FFVC1760封裝,掛載4組NVME,接口為PCIE X4 ,

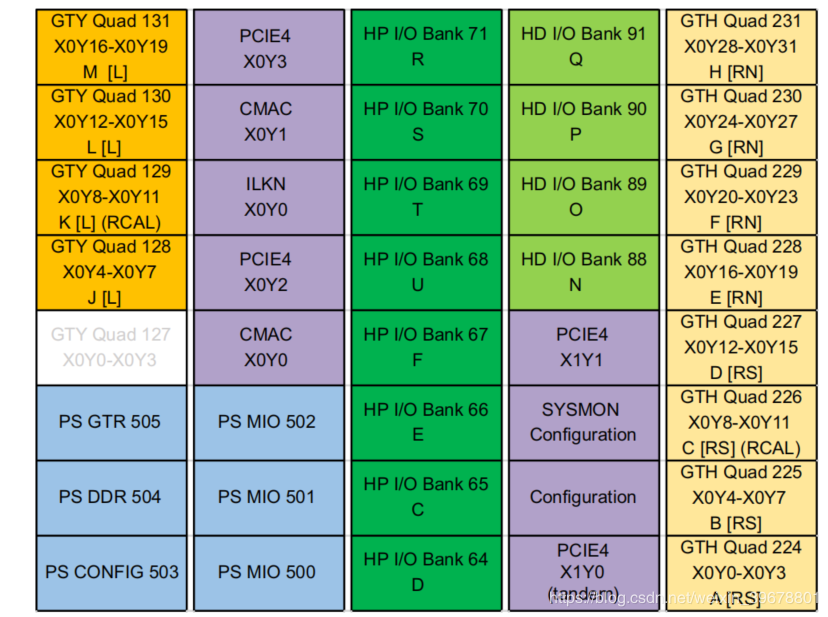

先我們先對(duì)ZU11EG的資源進(jìn)行分析,在UG1075中我們可以清楚的看到其包含4個(gè)PCIE塊,分別位于X0Y2,X0Y3,XIY1,XIY0.

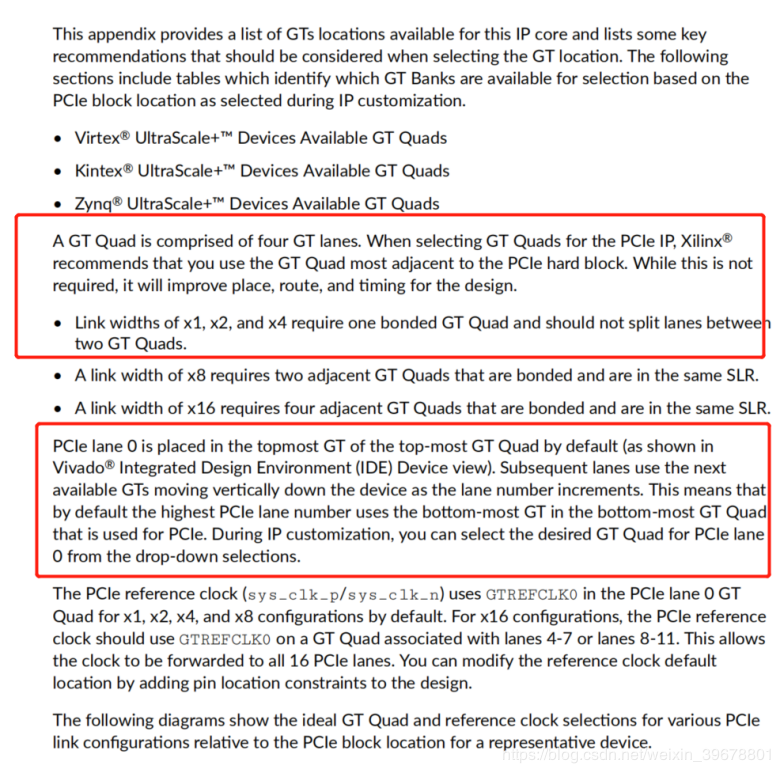

在文檔PG213上我們可以看到如下:

總結(jié)上文:在硬件設(shè)計(jì)引腳分配的時(shí)候我們需要知道:

1、一個(gè)GT Quad由四個(gè)GT車道組成。為PCIe IP選擇GT Quads時(shí),Xilinx建議您在最靠近PCIe硬塊的地方使用GT Quad。雖然這不是必要時(shí),它將改善設(shè)計(jì)的位置,路線和時(shí)間。

2、需要注意PCIE lane 0的位置

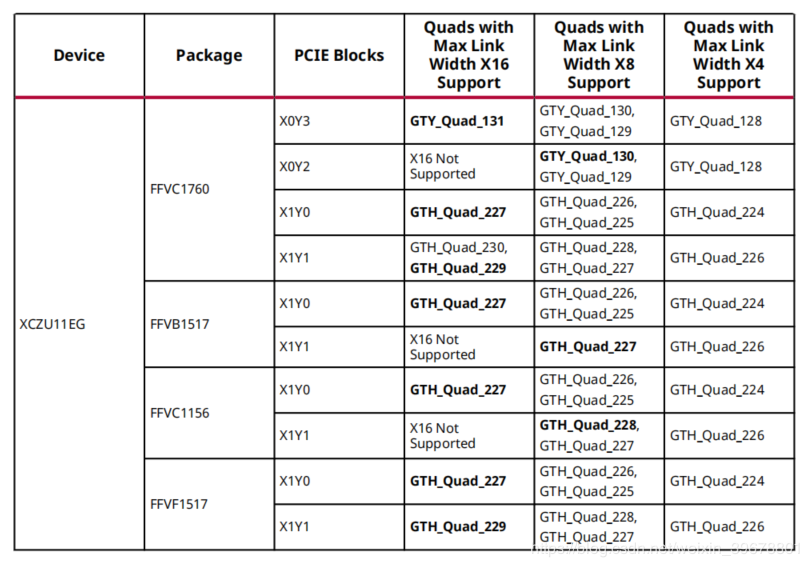

3.根據(jù)些表格,這些表格根據(jù)以下內(nèi)容確定哪些GT庫(kù)可供選擇:IP自定義期間選擇的PCIe塊位置。

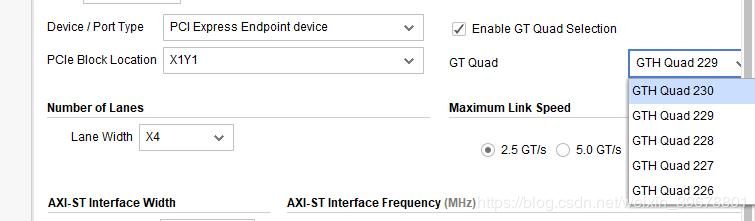

那如何驗(yàn)證自己的分配結(jié)果呢?最終在實(shí)際使用的時(shí)候我們會(huì)應(yīng)用到相關(guān)的IP核,最簡(jiǎn)單也是最靠譜的方法,是采用vivado新建工程,生成PCIE的IP核進(jìn)行驗(yàn)證,如下圖所示,可以清楚的知道對(duì)應(yīng)的那些可用。

在FPGA硬件設(shè)計(jì)中,引腳分配是最重要的一步,也是最關(guān)鍵的一步。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618813 -

封裝

+關(guān)注

關(guān)注

128文章

8694瀏覽量

145559 -

硬件設(shè)計(jì)

+關(guān)注

關(guān)注

18文章

434瀏覽量

45212

發(fā)布評(píng)論請(qǐng)先 登錄

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡解決方案

基于Xilinx XCKU115的半高PCIe x8硬件加速卡

XCKU115板卡資料:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡

FPGA硬件設(shè)計(jì)教程資料

基于Xilinx FPGA的Memcached硬件加速器的介紹

FPGA硬件基礎(chǔ)之FPGA時(shí)鐘資源的工程文件免費(fèi)下載

FPGA硬件基礎(chǔ)之FPGA的邏輯單元的工程文件免費(fèi)下載

FPGA硬件基礎(chǔ)之FPGA的RAM存儲(chǔ)課件和工程文件

Xilinx 7 系列FPGA中的Serdes總結(jié)

XILINX FPGA的硬件設(shè)計(jì)總結(jié)之PCIE硬件設(shè)計(jì)避坑指南

Xilinx 7系列FPGA收發(fā)器架構(gòu)之硬件設(shè)計(jì)指導(dǎo)(一)

FPGA PCIe加速卡開源硬件及例程介紹

基于FPGA的硬件引腳分配設(shè)計(jì)總結(jié)

基于FPGA的硬件引腳分配設(shè)計(jì)總結(jié)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

基于XILINX FPGA的硬件設(shè)計(jì)總結(jié)之PCIE硬件設(shè)計(jì)避坑

基于XILINX FPGA的硬件設(shè)計(jì)總結(jié)之PCIE硬件設(shè)計(jì)避坑

評(píng)論