前言

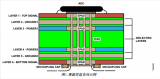

InFO(Integrated-FanOut-Wafer-Level-Package)能夠提供多芯片垂直堆疊封裝的能力,它通過RDL層,將芯片的IO連接扇出擴展到Die的投影面積之外,增加了bump的放置靈活性和IO數量。與CoWoS-S相比,既減少了硅制造成本,又通過異構集成獲得了性能的提升,以及更小的體積。

在InFO封裝設計中,其主要的難點在RDL自動化布線的實現,如何做到高效、DRC-clean以及高質量(電氣、可靠性)實現?

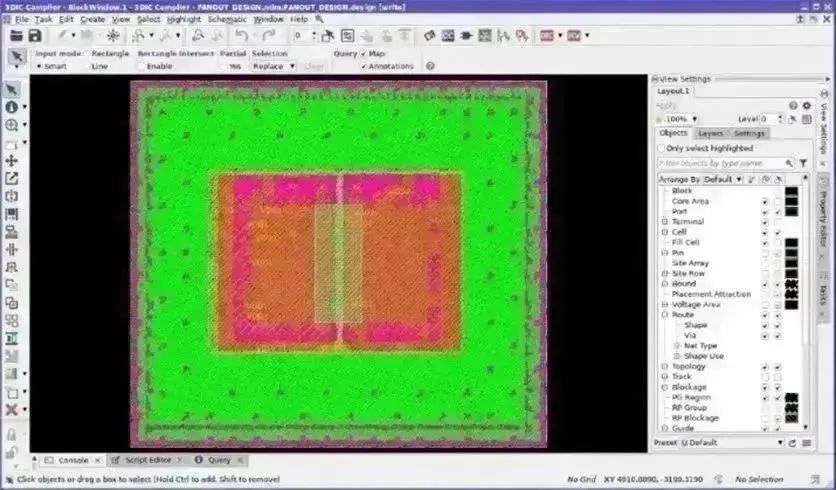

圖 1

InFO_3D封裝

芯和半導體的3DICCompiler(以下簡稱“3DICC”)設計平臺,全面支持2.5D/3D chiplets集成設計和仿真。

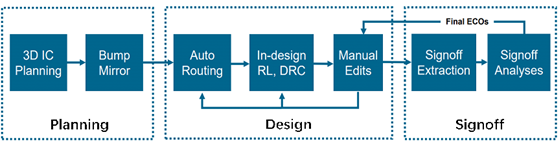

本文介紹如何基于3DICC設計平臺實現Fanout集成方式的布局布線,整個流程包含芯片創建、頂層創建、FanOut substrate創建和實現,以及系統規則檢查和dummy填充、degassing hole添加,如下:

圖2

FanOut設計流程

案例介紹

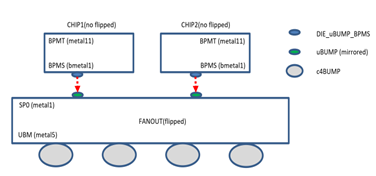

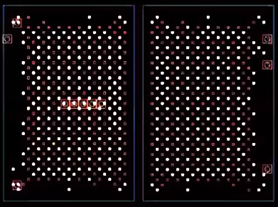

圖 3

FanOut示例

1. 創建芯片模型,讀入設計數據

首先,我們需要為每個芯片創建一個基本模型。為die定義floorplan的boundary,然后讀入CSV文件,建立front-side的microbump pattern,這些microbump將與fanout substrate連接。

如下圖:

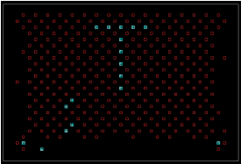

圖4

(a)Die1 bump arrary (b) die2 bump array

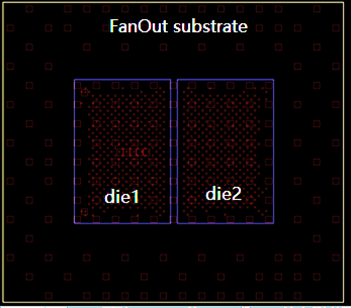

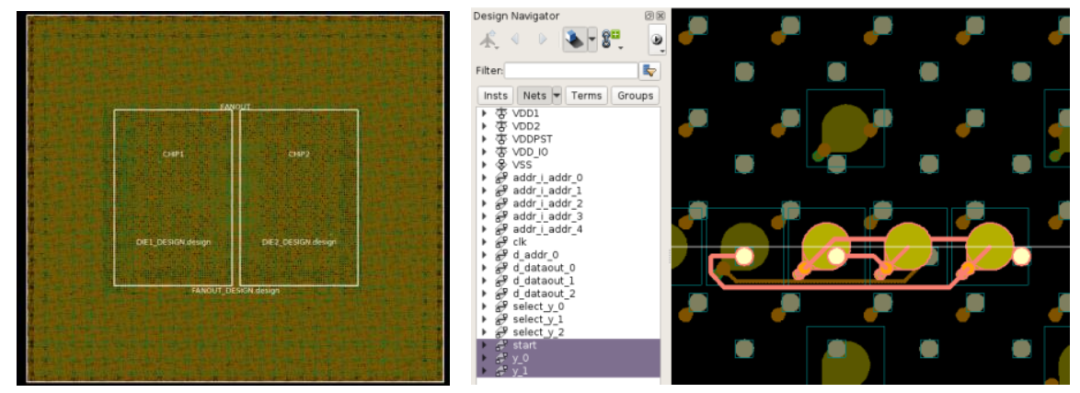

2. 創建FanOut substrate

讀入C4 bump的CSV文件,建立僅包含boundary信息的substrate floorplan。

圖5

(a)FanOut substrate boundary

(b) FanOut substrate的C4 bump陣列

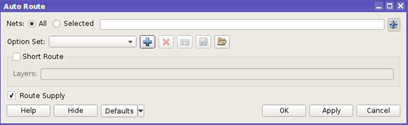

3.創建系統頂層

1)讀入兩個top die和substrate的NDM庫,進行布局放置。

圖6

FanOut設計頂層創建

2)Microbump鏡像創建。通過3DICC的bump mirroring功能,將top die的microbump陣列鏡像到substrate上,自動創建對接的microbump陣列。

圖7

top dies的bump鏡像實現

3)基于頂層netlist和鏡像后的bump陣列,自動追溯芯片間和芯片與封裝基板間的互連關系,創建substrate的netlist和所有互連通道和映射關系,完成top level系統建立。

圖8

系統互連的自動創建

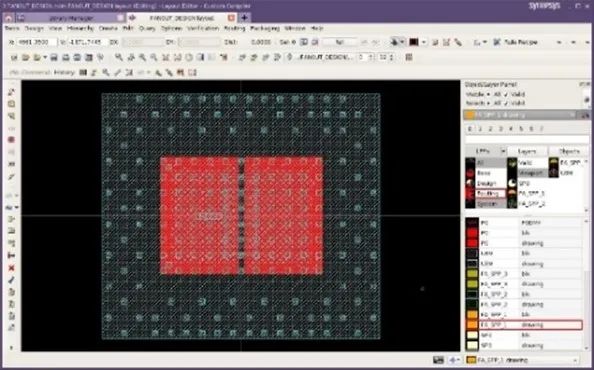

4.Fanout substrate自動布線

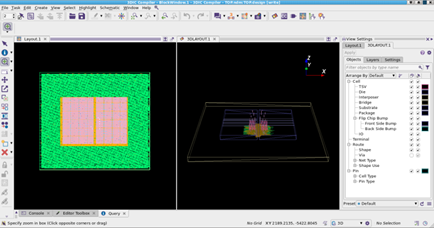

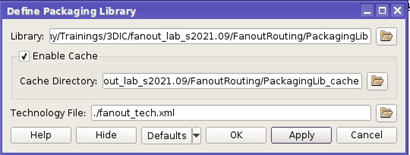

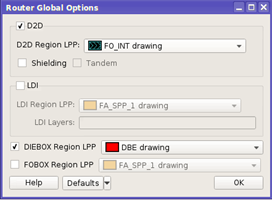

RDL substrate的自動布線將通過3DICC的add-on Custom Compiler進行。在進行布線之前,定義可調用的PDK庫,其中包含定制的各種特殊圖形PCell,如橢圓形、長方形等。點擊OK后,系統將把這個庫添加進入lib.defs文件中。另外,在版圖編輯器中選擇Packaging > Router Global Options,在Router Global Options中設定如下,完成自動布線器的全局規則設定。

圖9

PDK庫和自動布線全局規則設定

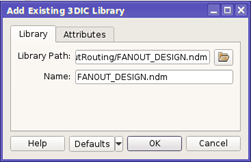

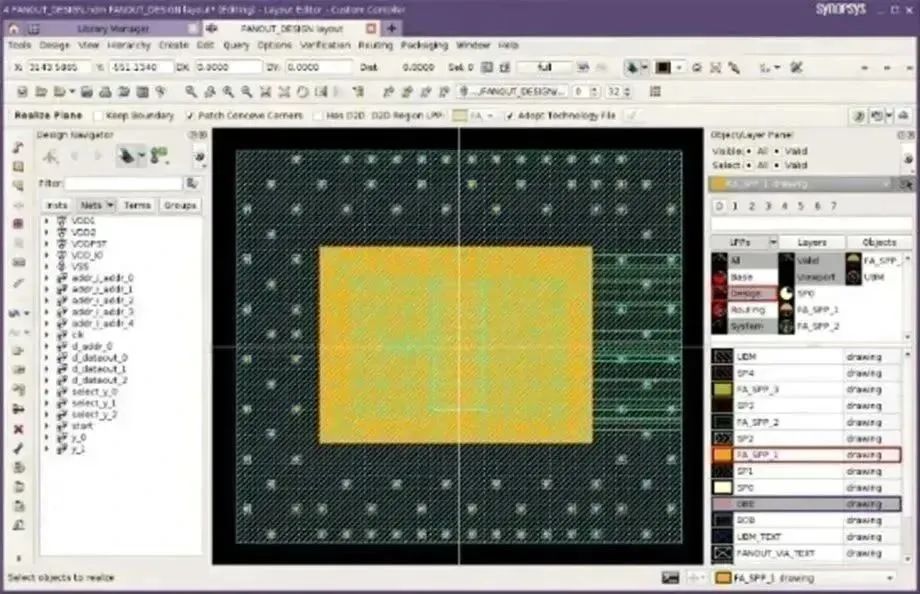

1)打開3DICC設計庫,導入頂層設計版圖。

圖10

頂層設計版圖

2)多層任意角度自動布線。

在Hierarchy工具欄設定stop level(可見的level深度)為1,使得布線器可以看到層次化設計中的pins和blockages。在Packaging > Auto Route中設定如下:

圖11

布線設定

完成布線后,回到top view的結果如下:

圖12

多層自動布線

3)PG平面創建。

設定用于PG平面創建的nets和布線層,如下:

| Nets | PG Plane layers |

| VDD1, VDD2, VDDPST | FA_SPP_1 |

| VDD_IO | FA_SPP_3 |

| VSS | FA_SPP_2 |

為VDD1創建PG平面邊界。在Object/Layer Panel選擇FA_SPP_1 drawing LPP。選擇Packaging > Create Plane Boundary,在Create Plane Boundary工具欄,鍵入VDD1到Nets欄,在版圖上用FA_SPP_1層畫一個矩形區域,將VDD1 bumps/pins覆蓋住。

圖13

VDD1平面邊界創建

新創建的平面邊界將目標網絡和目標LPP信息存儲為屬性,這些屬性將被布線器使用。接下來,重復以上步驟,為所有PG網絡創建平面邊界。

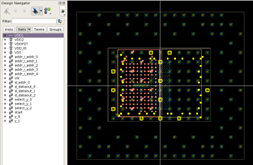

4)調整PG平面邊界

檢查各個PG平面邊界中是否有將其他電源域的pin或者net包覆進來,如有,則進行平面調整,避免引起短路或開路。如下圖中,可以看到VDDPST(黃色亮點)的bump也被VDD1平面邊界覆蓋。由于VDD1、VDD2、VDDPST共享同一層FA_SPP_1,為了確保不造成任何開路或短路,必需對平面邊界進行調整。

圖14

初版PG平面邊界

在Object/Layer Panel選擇FA_SPP_1 drawing LPP,關閉除FA_SPP_1 和border drawing之外的所有可視層。在Design Navigator選擇VDD1.該net被highlight出來。選擇Packaging > Create Plane Boundary。其中仍然被包覆的其他bump(黃色高亮的VDDPST)可以通過繼續切割進行處理。

圖15

VDD1 PG平面邊界調整

繼續進行VDD2和VDDPST的平面邊界調整。結果如下:

圖16

VDD2和VDDPST PG平面邊界調整

接下來,在Object/Layer Panel中使所有LPP層可視可選,Edit > Select > By LPP中選擇border drawing。到Packaging > Realize Plane。執行結果如下:

圖17

PG平面邊界調整結果

5.布線結果檢查,dummy fill,de-gassing hole添加

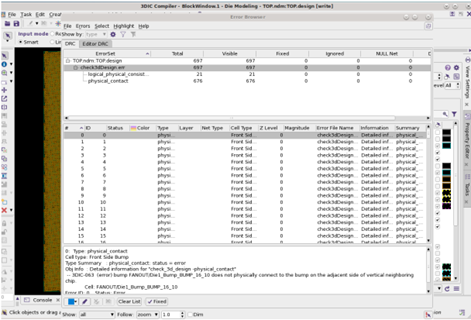

布線完成后,進行top-level的3D rule檢查和基于ICV的DRC、LVS、dummy fill和degassing hole創建等。

ICV的檢查結果可以在錯誤窗口進行查看,分為幾種類型:物理連接,匹配類型,邏輯物理一致性,bump cluster,芯片布局擺放,物理設計規則等。

圖18

ICV檢查結果

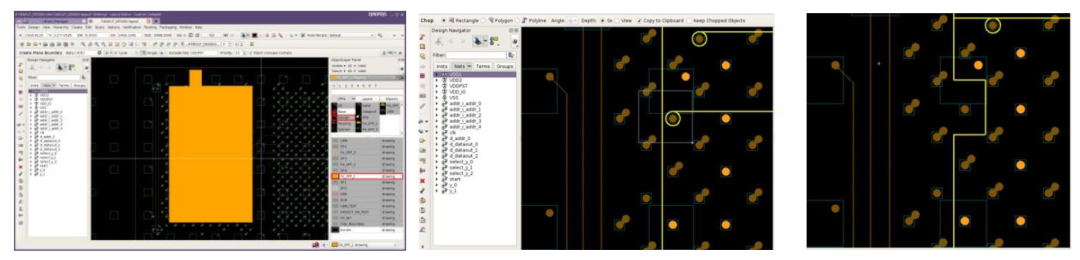

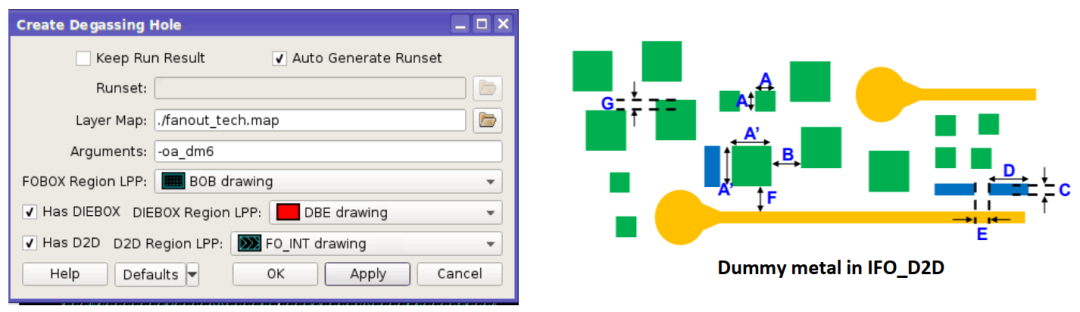

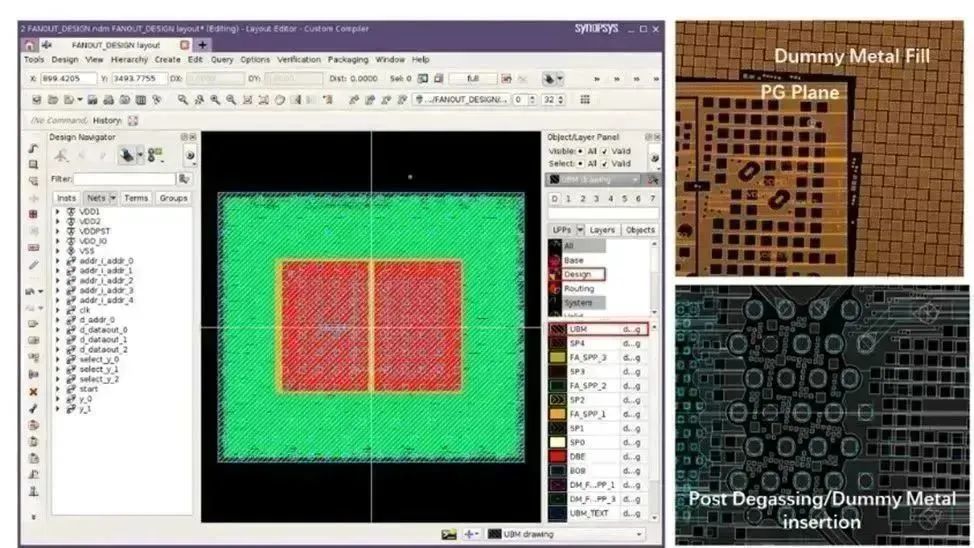

打開Packaging > Create DeGassing Hole,選擇如下:

圖19

de-gassing hole and dummy fill

生成設計的GDS,運行ICV來生成de-gassing holes和dummy fills,將de-gassing holes導入到當前設計中,代替PG平面。當操作結束以后,degassing holes被創建完成,版圖展示如下:

圖20

post de-gassing hole and dummy layout

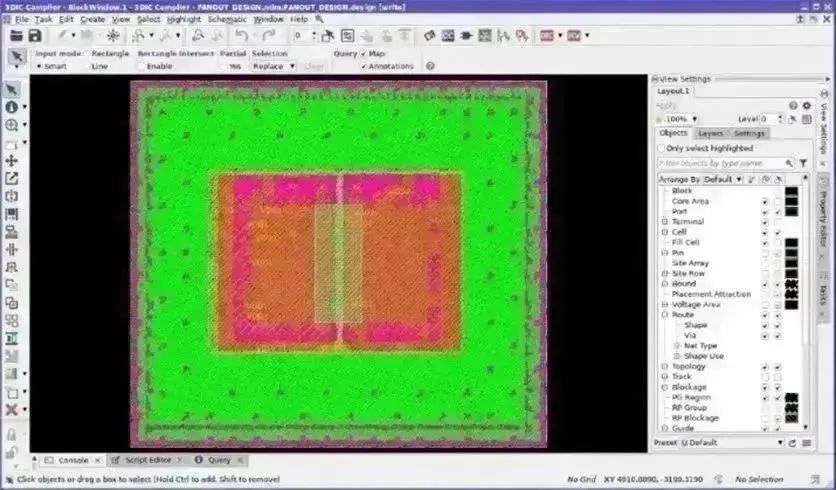

6.同步頂層設計

使用Custom Compiler完成InFO布線和編輯后,在3DICC中直接打開編輯過的設計,Tools > Digital Implementation > 3DIC Compiler,完成設計的同步更新。

圖21

最終版圖結果

總結

3DIC Compiler可以幫助設計者實現InFO封裝物理設計和分析,能夠達到高度自動化(可以將數周的實現時間壓縮到幾小時),具有可定制substrate、高容量、高性能等特點。并且和芯片設計數據在統一平臺上完全同步,實現芯片-封裝協同設計。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52306瀏覽量

437766 -

封裝

+關注

關注

128文章

8598瀏覽量

144989 -

布線

+關注

關注

9文章

796瀏覽量

84961 -

info

+關注

關注

0文章

11瀏覽量

10272 -

芯和半導體

+關注

關注

0文章

117瀏覽量

31752

原文標題:【應用案例】如何基于3DICC實現InFO布局布線設計

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

HarmonyOS NEXT應用元服務布局合理使用布局組件

高速PCB布局/布線的原則

如何布線才能降低MDDESD風險?PCB布局的抗干擾設計技巧

解決噪聲問題試試從PCB布局布線入手

Vivado之實現布局布線流程介紹

串行接口PCB設計指南:優化布局與布線策略

求助,關于模擬電路的PCB布線及布局問題求解

AM62Ax/AM62Px LPDDR4 電路板設計和布局布線指南

谷歌Tensor G5芯片轉投臺積電3nm與InFO封裝

高速ADC PCB布局布線技巧分享

非常實用的PCB布局布線規則,畫出美而高性能的板子

PCB布局布線技巧之功率回路

如何基于3DICC實現InFO布局布線設計

如何基于3DICC實現InFO布局布線設計

評論