6 回路電感

現(xiàn)實(shí)設(shè)計(jì)中,電流是在一個(gè)完整的回路中流動(dòng),此完整電流回路的總電感稱為回路電感,又稱為回路自感。即當(dāng)回路中流過1安培電流時(shí),從信號(hào)源出發(fā),沿著導(dǎo)線行走時(shí),整個(gè)回路中所有電流產(chǎn)生的磁力線總匝數(shù)。

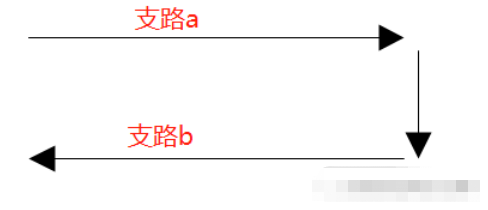

以支路a和支路b組成的回路為例,整個(gè)回路的自感

Lloop=La-Lab+Lb-Lab=La+Lb-2Lab

Lloop是整個(gè)回路的回路自感。Lab是支路a和支路b之間的局部互感。La和Lb是各自支路的自感。此公式說明,當(dāng)兩支路靠近時(shí),各自的支路自感不變,兩支路之間的互感增大,導(dǎo)致回路自感減小。

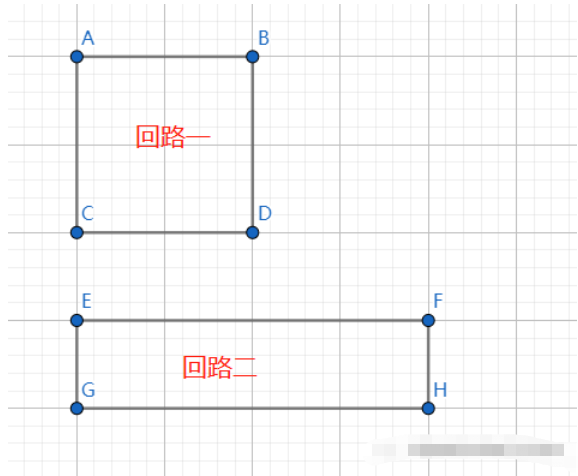

很多時(shí)候,我們?cè)谧?a target="_blank">PCB設(shè)計(jì)時(shí),都要求回路面積盡量小,其實(shí)這只是一個(gè)籠統(tǒng)的說法。更關(guān)鍵的在于回路中兩支路的距離是否近。如下圖是2個(gè)面積一樣,但是回路電感不同的設(shè)計(jì)。當(dāng)此回路中兩個(gè)支路電流方向相反時(shí),回路二的互感更大,整個(gè)回路電感更小。

下面有三種特殊結(jié)構(gòu)的回路電感。

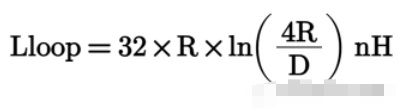

第一種:環(huán)形線圈回路的回路電感公式

R是線圈半徑,單位是in;D是構(gòu)成線圈的導(dǎo)線直徑,單位是in。Lloop的單位是nH。從以上公式可以看出,此種回路的電感不是與圓環(huán)的面積或者周長成正比。而是與圓環(huán)的半徑乘以半徑的對(duì)數(shù)成正比。因?yàn)閳A環(huán)周長越長,每一段的局部自感就越大。但同時(shí),回路中相反方向的電流距離越遠(yuǎn),相互之間的互感越小。

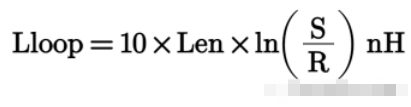

第二種:兩根相鄰的直圓桿,其中一條為另一條的返回電流路徑。它們的回路電感公式

Len是圓桿長度,單位是in;R是圓桿半徑,單位是mi;S是兩圓桿之間的間距,單位是mil,Lloop的單位是nH。此公式說明兩根平行導(dǎo)線的回路電感和導(dǎo)線的長度成正比,與中心距離的自然對(duì)數(shù)成正比。注:自然對(duì)數(shù)變換相對(duì)緩慢。此種情況和兩條扁平PCB走向有點(diǎn)像。

第三種:兩個(gè)寬平面。在下一篇文章中有說明。

注意:任何阻抗可以控制的互連線,它的單位長度回路電感都是恒定的。

7 電源分布系統(tǒng)(PDS)和它的回路電感

7.1電源分布系統(tǒng)

電源分布系統(tǒng)就是電源和負(fù)載、以及它們之間的電源路徑和地路徑。此系統(tǒng)也會(huì)影響到信號(hào)完整性。在PDS中,從電源到負(fù)載,中間有很多的互連線,還有過孔、電源平面或者地平面、封裝引線、鍵合線等。當(dāng)進(jìn)入芯片的電流發(fā)生變化時(shí)(例如LPDDR4的數(shù)據(jù)在快速的變化,即邏輯門在快速的開和關(guān)),電源和負(fù)載之間PDS的這些互連線等因素的阻抗就會(huì)引起電壓降,稱為軌道下降或者軌道塌陷。要使電流變化引起的電壓降最小,PDS的阻抗就要小于一定的值。這樣即使電流還在變化,引起的電壓降也還在負(fù)載可以接受的范圍之內(nèi)。

7.2降低PDS阻抗的辦法

方法一:使用電源平面和地平面?zhèn)鬏旊娏鳌k娫雌矫婧偷仄矫姹入娫醋呔€和地走線更好的原因,就在于電源平面和地平面的回路電感非常低,造成的電壓降更小。

方法二:在低頻段,使用低阻抗的去耦電容。高頻段,使去耦電阻和負(fù)載焊盤間的回路電感最小,以保持它們之間的阻抗低于一定值。

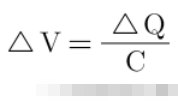

那么使用多大的去耦電容合適呢?原則是依據(jù)在時(shí)間段△t內(nèi),去耦電容必須提供的電荷量來大致估算。因?yàn)樵凇鱰時(shí)間內(nèi),會(huì)有△Q的電荷從電容上向芯片釋放,這個(gè)動(dòng)作會(huì)導(dǎo)致電容上電壓下降△V。即

而在此時(shí)間段內(nèi),芯片需要的電流由芯片自身決定,例如對(duì)SOC而言,就要看那個(gè)時(shí)間段,它處于什么狀態(tài),運(yùn)行功耗是多少?運(yùn)行功耗又和它的供電電壓,以及需要消耗的平均電流有關(guān)。假設(shè)它需要的電流是I、功耗是P、供電電壓是V,則

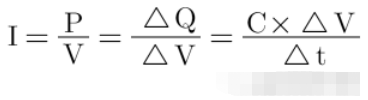

通常大多數(shù)芯片要求電壓紋波不超過正常值的5%,因此

△t的單位是秒,C的單位是法拉,V的單位是伏,P的單位是瓦特。

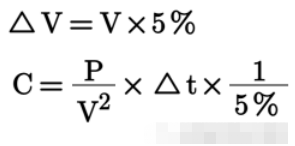

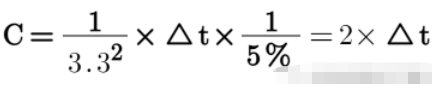

例如一個(gè)小的Nor flash,工作電壓是3.3V,假設(shè)其功耗是1W,則需要的總?cè)ヱ铍娙萘渴?/p>

如果給Nor flash供電的LDO沒辦法在10us之內(nèi)對(duì)Nor flash的耗電做出足夠的反應(yīng),則需要在LDO和Nor flash之間提供20uF的去耦電容。如果去耦電容量小于這個(gè)值,Nor flash的供電電壓紋波會(huì)大于5%。

7.3去耦電容帶來的回路電感

針對(duì)上面提到的例子,不建議使用單個(gè)20uF的去耦電容。應(yīng)該將多個(gè)電容器并聯(lián)使用。目的是多個(gè)電容并聯(lián)使用,可以降低回路電感。因?yàn)閷?shí)際電容器管腳和Nor flash的電源pin焊盤之間有PCB走線,這段走線會(huì)有相應(yīng)的回路電感。此回路電感和電容串聯(lián),導(dǎo)致電容的阻抗隨著頻率的上升而增大。

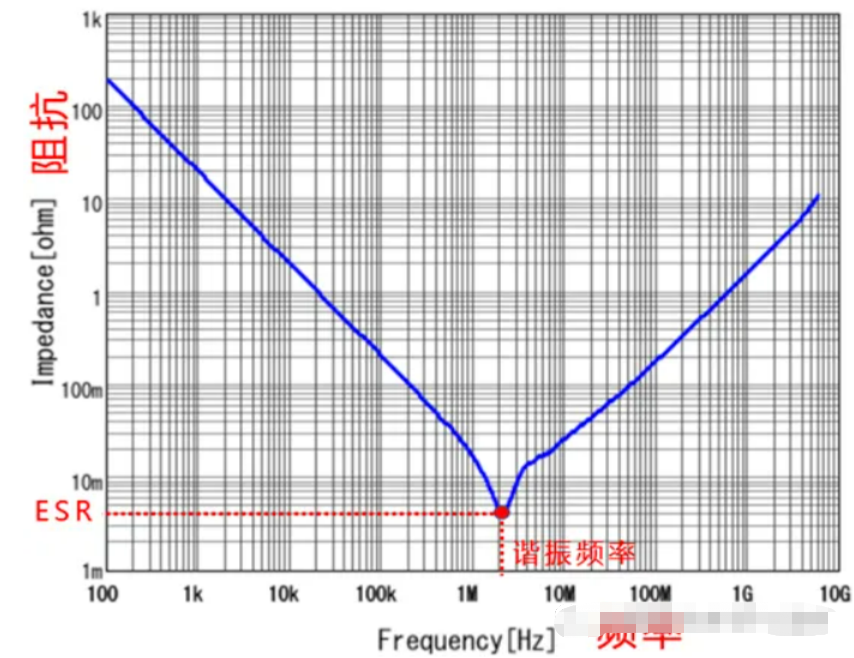

下圖是一顆電容的阻抗曲線。在2MHz以下,它就像理想電容一樣,阻抗隨著頻率增大而減小。從2MHz開始,串聯(lián)的回路電感開始起主導(dǎo)作用。把2MHz稱為自諧振頻率,從此點(diǎn)開始,阻抗增大。注:當(dāng)越過自諧振頻率點(diǎn)之后,電容的阻抗和電容量沒有關(guān)系了,只與相關(guān)的回路電感有關(guān)。因此要想在頻率較高點(diǎn),減小去耦電容的阻抗,就要減小去耦電容相關(guān)部分的回路電感(如上面提到的減小去耦電容管腳到負(fù)載芯片電源pad之間的距離和回路電感),單純的增加電容量是沒有用的。

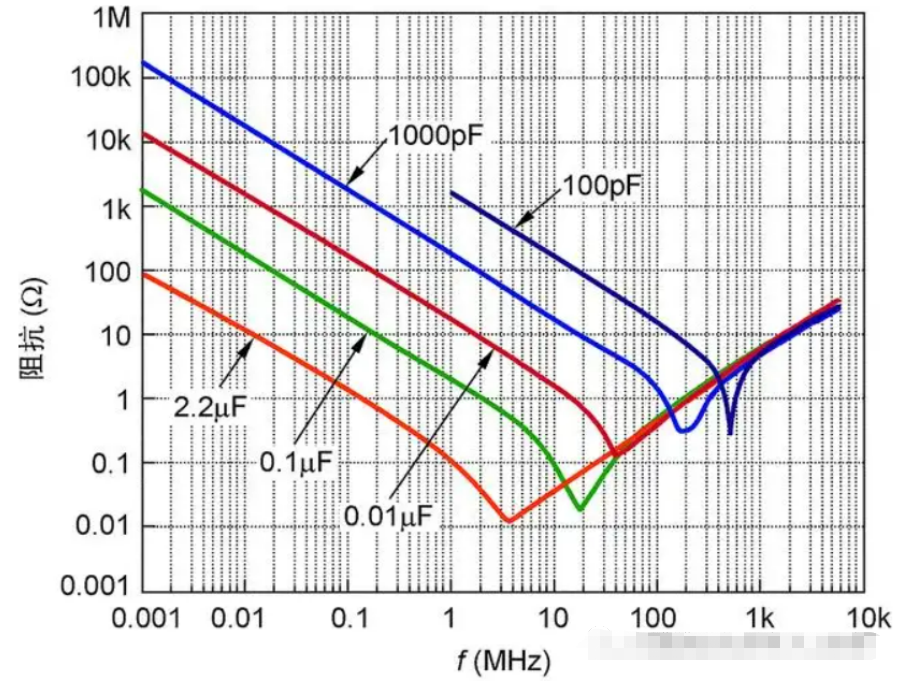

下圖是5個(gè)電容量不同但都是0603封裝的電容阻抗測(cè)試結(jié)果。可以看出在低頻段時(shí),電容量的容值不同,因此阻抗各有差異。在高頻段,因?yàn)榉庋b結(jié)構(gòu)相同,阻抗也趨于一致。因此高頻段曲線和電容容值沒關(guān)系,和電容的封裝、電容到負(fù)載電源pad的走線有關(guān)系。

7.4總結(jié)

總結(jié):減小去耦電容回路電感的幾種方法

①電源和地走線都用平面,這是回路電感最小的一種互連線結(jié)構(gòu)。

②盡量減小電源平面和地平面的間距

③使電源平面層和地平面層,盡量靠近電路板的表層,以縮短過孔距離

④使用封裝小的電容

⑤電容焊盤到過孔距離、電容焊盤到負(fù)載管腳的距離盡量短。同時(shí)此段走線要遠(yuǎn)離PCB的IO端口,降低對(duì)外的EMI輻射。

⑥多個(gè)電容器并聯(lián)使用

⑦電容焊盤到負(fù)載管腳的走線和返回路徑,設(shè)計(jì)成回路電感最小的方式

-

電源

+關(guān)注

關(guān)注

185文章

18373瀏覽量

256393 -

pcb

+關(guān)注

關(guān)注

4368文章

23492瀏覽量

409864 -

信號(hào)源

+關(guān)注

關(guān)注

5文章

499瀏覽量

45817 -

電感

+關(guān)注

關(guān)注

54文章

6207瀏覽量

104247 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1445瀏覽量

96768

發(fā)布評(píng)論請(qǐng)先 登錄

信號(hào)完整性為什么寫電源完整性?

何為信號(hào)完整性?信號(hào)完整性包含哪些

信號(hào)完整性原理分析

什么是信號(hào)完整性

信號(hào)完整性與電源完整性仿真分析

信號(hào)完整性分析

信號(hào)完整性分析基礎(chǔ)知識(shí)

信號(hào)完整性系列之“信號(hào)完整性簡介”

信號(hào)完整性與電源完整性的仿真

信號(hào)完整性之電感的知識(shí)(二)

信號(hào)完整性之電感的知識(shí)(二)

評(píng)論